3.2 基本要求与方法

3.2.1 理想恒流与恒压

偏置电路的关键和基础地位对模拟集成偏置提出了更高的要求,即稳定性与适用性,偏置的目的是提供电路理想的恒流源或理想的恒压源。CMOS电路系统中电压偏置的基本要求是提供电路(主要是MOS管)稳定的栅电压,对于电流偏置而言,即提供MOS管稳定的输出电流。提供的偏置应尽量减小对工艺和温度的敏感性,降低功耗和成本。

图3-1所示的理想偏置中,其特性是工作范围宽,精度高且稳定,具体表现就是不受工艺、电源电压和温度的影响,即通常所说的PVT无关性,这也是一般意义上模拟电路设计所追求的最高境界。

在CMOS电路中,电压和电流偏置既相互关联,也可相互转化。电路设计和应用也是利用这一基本原理,将稳定的电流转换成恒定的电压,或者将稳定的电压转换成恒定的电流。只要其中之一能够确定并稳定,相对应的另一个变量也能达到相应的稳定要求。在CMOS偏置电路设计中,就是寻找电流和电压相互之间的依存或因果关系,通过合理的反馈控制,获得稳定的电流、电压状态。需要特别指出,CMOS中NMOS的栅压VGSN是以GND为参考,稳定电流偏置的条件是VGSN为常数,表现为VGSN的固定或恒定电压偏置;而PMOS的栅压VGSP是以VCC为参考,电流恒定的要求是VGSP为常数,即VGSP跟随VCC的变化而同步变化。

图3-1 具有互补对称特性的理想电流和电压源特性

理想电压电流源的输出特性由其交流小信号输出阻抗决定。理想电流源要求其输出阻抗为无穷大,导纳为零,理想电压源输出阻抗为零,导纳无穷大。其次,在精度满足的前提下,要求适应的范围无限大。显然,实际电路中不可能存在具有这种理想特性的元件,如线性电阻,其阻抗受限。MOS管可实现近似理想的恒流和简单的恒压(电压钳位)特性,BJT的恒压和电压钳位能力虽有提高,但离理想偏置要求无论从精度还是适用范围上都有很大距离。因此,偏置电路设计的基本要求,就是利用已有元件的I-V特性,采用适当的元器件组合及相关控制技术构造高性能的偏置电路结构。

偏置电路设计中的三个核心问题,首先是静态工作点的确定,即静态支路电流的定义,这是一个涉及直流电阻分压的问题,静态电流至少应与VCC无关;其次是支路电流的电源抑制比特性,这是一个交流阻抗分压的交流小信号问题,利用MOS管饱和恒流及共源共栅Cascode调节控制,降低电源噪声对偏置电流的影响;最后,是各支路电流的线性匹配精度控制,这本质上是直流工作点的匹配问题,由此形成各类高精度电流镜。以上三个方面既相互联系,又有不同侧重。显然,采用基本电阻分压结构无法满足以上各方面的要求,但各类高性能电压和电流偏置,都可以看成是从最基本的电阻分压原型结构发展得来。

3.2.2 交直流分析方法

电路分析是电路设计的重要基础。电路分析方法主要有两类,一类是等效电路法,即将电路元件用其交直流等效模型代替,并通过电路方程求解相应的信号变量输出。显然,这种基于等效电路的分析方法本质上是一种数学方法,适合单元结构及小规模模拟电路的设计,结果精确但不直观,对于复杂电路的分析应用受到一定的限制。另一类为物理近似法,该方法的特点与以上基于等效电路分析方法互补,直观但精度欠佳。在物理近似分析中,关键在于抓住电路最核心和本质的物理机制及相关制约条件,而将枝节和无关紧要的内容完全忽略,大体精确并快速得到具有特定物理意义的描述,因此容易获得对电路本质更加清楚的认识。

在实际的电路分析中,通常需要将以上两种方法有机结合。对于单元和典型电路结构,通常采用精确的等效电路法,而对于复杂电路,根据实际条件和相应的物理控制机制,可在忽略次要因素的前提下简化电路,并利用基本电路的已有分析结果,达到对复杂电路简化分析的目的。以下结合具体电路,对比两种分析方法的不同特点。

设某个MOS管的宽长比为(W/L)i,考虑简单的N个MOS管的串并联问题。首先分析并联结构,若并联MOS管的沟道长度均为相同的L,则并联等效MOS管的W/L为

若各MOS管的沟长互不相同,则对其进行归一化处理,将各个MOS管的沟长等效为L,即(Wi/Li)=[(Wi/Li)L]/L,此时等效宽度Wi′=(Wi/Li)L,沟长全部相同并为L,此时利用式(3-1)的结果,得到同样性质的关系式。对于并联结构,无论各MOS管的沟长是否相同,并联等效MOS管的W/L总是各MOS管(W/L)i的线性叠加求和,因此MOS并联总是使W/L增加。

类似地,对于N个MOS管的串联结构,若各管沟道宽度W相同,则串联等效MOS管的L/W为

采用同样的分析方法,即使当W不同时,以上式(3-2)同样成立,即对于串联MOS管,其等效MOS管的L/W为各管(L/W)i的线性叠加,即L/W增加或W/L减小。由于串联等效与并联等效相对应,则在保持叠加规律不变的条件下,并联的W/L对应为串联的L/W;与此等价,当串联MOS仍然采用W/L描述时,其等效值可由式(3-2)改写为

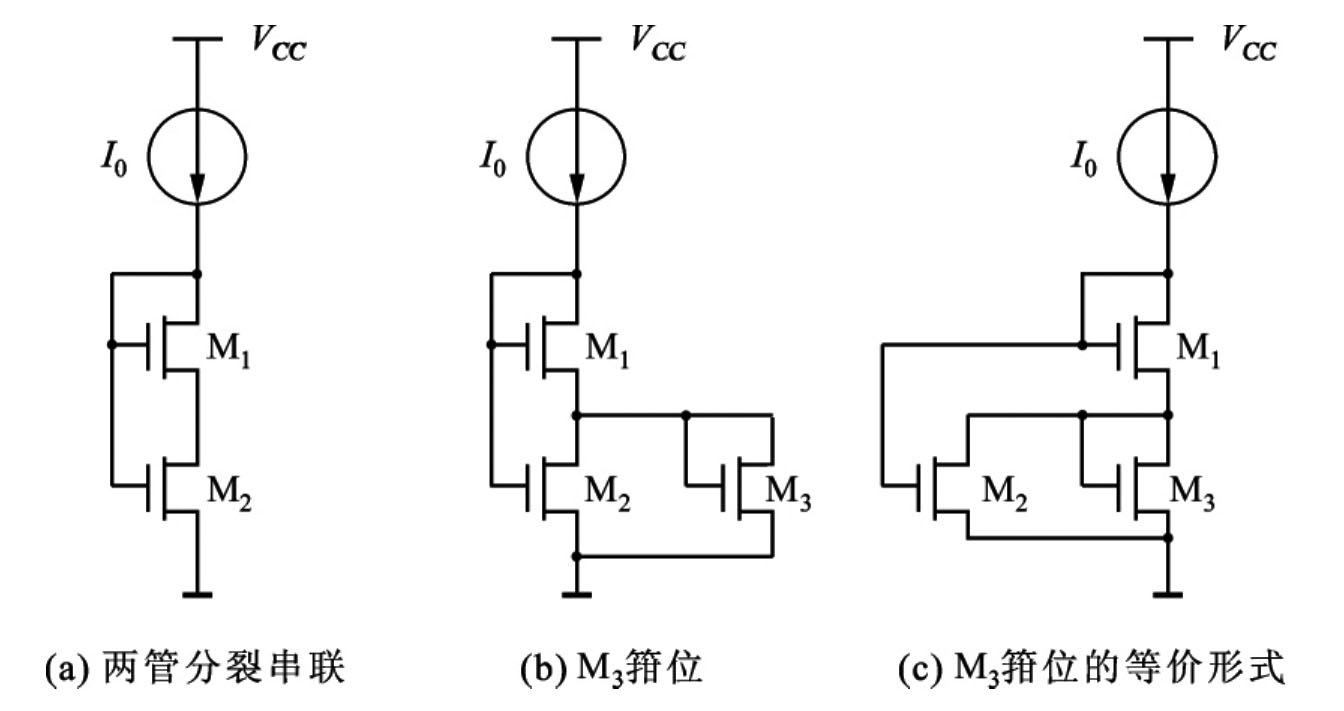

利用MOS串并联引起的W/L变化及其在电路内的连接关系,可以清晰地判断各MOS管的工作状态。以图3-2(a)所示的两串联MOS管恒流驱动结构为例,位于上方的M1二极管一定处于饱和恒流区,而M2一定处于线性电阻区。

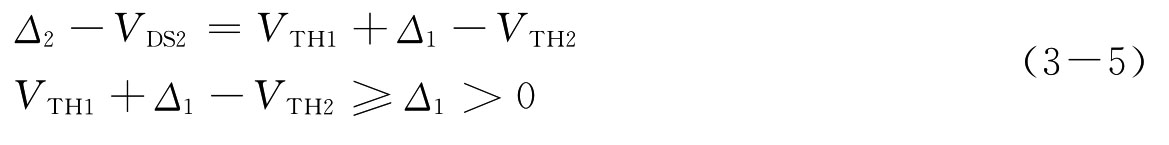

首先,采用基于数学模型推导的分析方法,从图3-2所示电路结构上看,M1的连接方式决定了饱和恒流的状态无条件满足。根据数学模型关系,饱和M1管与M2管的过驱动电压满足以下制约关系

M1管衬底偏置效应的影响使VTH1≥VTH2,因VDS2较小,M1管衬偏作用可以忽略,NMOS管的开启电压近似相同,并且M1饱和导通一定有Δ1>0,则

对以上数学推导的物理理解为:当(W/L)2≥(W/L)1,M2管如在饱和区,由于M2管的VGS2大且(W/L)2大,显然饱和电流不能连续,而电流连续是基本限制条件,则只有M2管进入线性区使M2电流减小,满足电流连续的限制条件;当(W/L)2<(W/L)1,由于固定电流在M1管上形成的过驱动电压Δ1恒定,(W/L)2减小时VGS1和VDS1同步变化以保持Δ1恒定,M2管则同样处于线性电阻区。实际上M1管的饱和导通给出的限制条件为VS1<VGVTN,由于VS1=VDS2,VG-VTN=VGS1-VTN,使M2管一定处于VDS2<VGS1-VTN的线性电阻区。

图3-2 分裂的MOS二极管及其应用

以上问题还可从器件W/L等效的角度进行分析。根据串联等效原理,M1、M2串联等效MOS管的W/L总是小于(W/L)1、(W/L)2,在等效限制下两者均流过相同的电流,且M2与等效M管具有相同的栅压。由于M管一定处于饱和工作区,在以上电流和栅压均相同的条件下,(W/L)较大的M2管一定强制进入线性电阻区,否则电流不满足基本的连续性限制条件。显然,(W/L)2越大,M2管的线性程度越高,当(W/L)2趋近无穷时,VDS2=0,M2管等效短路而不起作用,此时M管即为M1管。

因此,对于MOS分裂的二极管,无论两管的W/L如何,也无论M1与M2中间串联结点的电位如何,只要MOS管导通,二极管M1管一定位于饱和区,而与此对应的靠近GND的M2管一定位于线性电阻区。应当注意的是,以上结论建立在支路电流连续和开启电压VTH相同的限制条件下。

如图3-2(b)所示,如果M2的漏端再并联一个二极管M3管,M3工作在何种状态?该结构又有何特点?显然,由于采用二极管连接,M3管理论上只有截止及饱和两种状态。如果电源电压足够高,即使VG1电位上升也不会引起恒流源进入线性区而导致偏置电流下降,则M3的截止状态可以排除。相比图3-2(a)中M3管为等效截止的状态,图3-2(b)中因M3的分流作用,虽然M2的电流减小,但M2管仍保留线性电阻的工作状态。

图3-2(c)是M3管位电路等价形式,M2管在电路中的负反馈控制起到稳定M3工作点的作用。当电源VCC增加时,如无M2管则VGS1、VGS3均相应增加,导致支路电流提高。当M2管反馈控制起作用后,由于VG2=VG1的关系,M2线性电阻R1随VCC的增加而减小,导致M1管电流增加,从而抑制了M3管栅压VGS3的增加。当以上两种作用相互平衡时,即支路增加的电流几乎流入M2中,由此获得基本稳定的VGS3偏置输出。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。