E题 简易频率特性测试仪

一、任务

根据零中频正交解调原理,设计并制作一个双端口网络频率特性测试仪,包括幅频特性和相频特性,其示意图如图E-1所示。

图E-1 频率特性测试仪示意图

二、要求

1.基本要求

制作一个正交扫频信号源。

(1)频率范围为1~40 MHz,频率稳定度≤10-4;频率可设置,最小设置单位100 kHz。

(2)正交信号相位差误差的绝对值≤5°,幅度平衡误差的绝对值≤5%。

(3)信号电压的峰峰值≥1 V,幅度平坦度≤5%。

(4)可扫频输出,扫频范围及频率步进值可设置,最小步进100 kHz;要求连续扫频输出,一次扫频时间≤2 s。

2.发挥部分

(1)使用基本要求中完成的正交扫频信号源,制作频率特性测试仪。

① 输入阻抗为50 Ω,输出阻抗为50 Ω;

② 可进行点频测量:幅频测量误差的绝对值≤0.5 dB,相频测量误差的绝对值≤5°;数据显示的分辨率:电压增益0.1 dB,相移0.1°。

图E-2 RLC串联谐振电路

(2)制作一个RLC串联谐振电路作为被测网络,如图E-2所示,其中Ri和Ro分别为频率特性测试仪的输入阻抗和输出阻抗;制作的频率特性测试仪可对其进行线性扫频测量。

① 要求被测网络通带中心频率为20 MHz,误差的绝对值≤5%;有载品质因数为4,误差的绝对值≤5%;有载最大电压增益≥ -1 dB;

② 扫频测量制作的被测网络,显示其中心频率和-3 dB带宽,频率数据显示的分辨率为100 kHz;

③ 扫频测量并显示幅频特性曲线和相频特性曲线,要求具有电压增益、相移和频率坐标刻度。

(3)其他。

三、说明

(1)正交扫频信号源必须自制,不能使用商业化DDS开发板或模块等成品,自制电路板上需有明显的覆铜“2013”字样。

(2)要求制作的仪器留有正交信号输出测试端口,以及被测网络的输入、输出接入端口。

(3)本题中,幅度平衡误差指正交两路信号幅度在同频点上的相对误差,定义为:![]() ×100%,其中U2≥U1。

×100%,其中U2≥U1。

(4)本题中,幅度平坦度指信号幅度在工作频段内的相对变化量,定义为:![]() ×100%。

×100%。

(5)参考图E-2,本题被测网络电压增益取: 。

。

(6)幅频特性曲线的纵坐标为电压增益(dB);相频特性曲线的纵坐标为相移(°);特性曲线的横坐标均为线性频率(Hz)。

(7)发挥部分中,一次线性扫频测量完成时间≤30 s。

四、评分标准

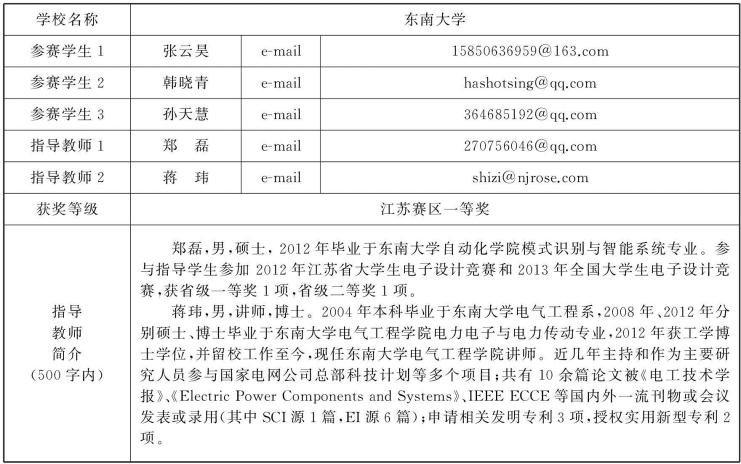

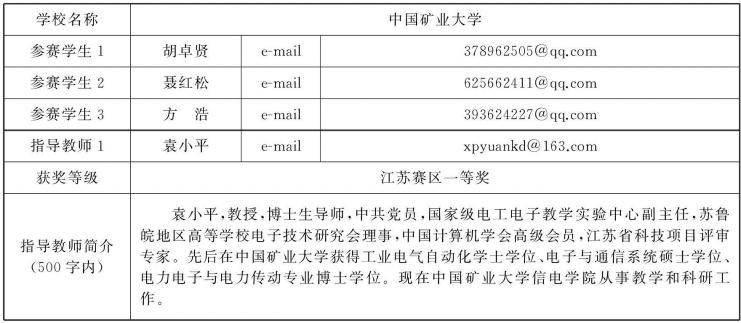

报 告 1

基本信息

一、设计方案工作原理

1.预期实现目标定位

本系统以MSP430F6638单片机为控制处理核心,由DDS芯片AD9854作为正交信号源,根据零中频正交解调原理,实现测试双端口网络幅频特性、相频特性的功能。

系统主要由三部分组成:信号产生部分、网络部分、测量显示部分。系统可由DDS芯片AD9854产生两路幅度稳定、相位差恒定的1~40 MHz正交信号,放大后经过被测网络,利用AD835混频,其后低通滤波,由高精度ADS1115采样正负电压至MCU进行计算,并进行点频测量、绘制网络幅频相频特性曲线,计算中心频率与-3 dB带宽,在320240液晶屏上显示。

2.系统结构工作原理

系统结构如图E-1-1所示。

图E-1-1 系统总体框图

本系统主要由控制模块、正交扫频信号源模块、放大模块、被测网络模块、混频模块、测量显示模块、电源模块组成。系统由DDS芯片AD9854产生1~40 MHz正交扫频信号,与自制的RLC串联谐振电路输出信号进行混频,再经过两路低通滤波和A/D转换之后,测量得到所需的幅度特性和相位特性,并在320240液晶显示器上进行显示。

3.技术方案分析比较

(1)正交扫频信号源模块的论证与选择

方案1:采用单片机控制两片AD9851产生正交信号。AD9851是高集成度DDS频率合成器,它内部包括可编程DDS系统、高性能DAC及高速比较器,能实现全数字编程控制的频率合成和时钟发生。AD9851接口功能控制简单,可以用8位并行口或串行口直接输入频率、相位等控制数据。32位频率控制字,在180 MHz时钟下,输出频率分辨率达0.0372 Hz。但是由于使用两片芯片,无法控制其时钟同步,所以难以达到题目要求的相位差范围。

方案2:采用FPGA查表方式,通过高速DAC经滤波后产生正弦信号。FPGA是具有高速运算功能的可编程逻辑器件,具有处理速度快、处理数字信号便捷等优点。但是由于所需D/A引脚数量多,FPGA开发板引脚数量有限,引脚密集造成高频信号互相干扰,使输出波形抖动较为严重,不能满足题目对输出波形的要求。

方案3:采用单片机控制一片DDS芯片AD9854产生I、Q两路正交信号。AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器,通过数字化编程可以输出I、Q两路合成信号。在高稳定度时钟的驱动下,AD9854将产生高稳定的频率、相位、幅度可编程的正弦和余弦信号,允许输出的信号频率高达150 MHz,且通带内平坦,符合题目对正交信号频率、幅度、相位的要求。

综合比较以上三种方案,选择方案3。

(2)低通滤波器的论证与选择

方案1:有源滤波器。有源滤波器易于设定截止频率或中心频率连续可调的滤波器。有源滤波器需要电源供电,可得到电压增益,易引入不必要的直流分量干扰后级测量。

方案2:无源滤波器。无源滤波器易于实现与前后级输入输出阻抗匹配,不需要电源供电,不会引入直流偏置,但信号幅度会有所衰减。

综合以上两种方案,考虑到本系统对混频输出的直流值有测量要求,所以选择方案2。

(3)计算和显示模块(处理器)的论证与选择

方案1:使用CycloneII EP2C5Q208C8 型号FPGA进行数字运算,并用VGA显示。FPGA具有高速运算的特点,但其不适合进行复杂的三角运算。用VGA显示分辨率高、色彩多,可以显示两种不同颜色的波形,且所需I/O口较少。

方案2:使用MSP430F6638单片机进行运算,并用320240液晶屏显示。MSP430F6638单片机具有片内资源丰富、可进行复杂计算、I/O口多、控制显示方便等特点。320240液晶屏显示直观、方便,便于用单片机控制显示。

考虑到本系统测量的信号为直流信号,且扫频速度不高,无需高速运算。所以利用单片机计算能力强、控制320240液晶屏显示便捷的特点,采用方案2。

4.测量控制分析处理

正交扫频信号源测试:将示波器通道输入阻抗调为50 Ω,用示波器测试两路正交信号在各个频点的输出峰峰值,用于计算幅度平衡误差以及幅度平坦度;用示波器测试两路信号的相位差,用于计算相位误差。

RLC被测网络的特性测试:用函数发生器输入峰峰值为1 V的正弦信号,测试各个频点的输出电压幅度,测量计算中心频率、有载品质因数Q、有载最大电压增益。

低通滤波器特性测试:用函数发生器输入峰峰值为1 V的正弦信号,测试各个频点的输出电压幅度,找到上限截止频率。

对RLC网络的点频测量:使用本系统制作的简易频率特性测试仪对待测的RLC网络进行点频测量,测量各频率下计算出的网络增益及相位,通过系统中的液晶屏显示。

二、核心部件电路设计

1.关键器件性能分析

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1 μHz)。输出17位相位截断保证了良好的无杂散动态范围指标。AD9854允许输出的信号频率高达150 MHz,符合本系统要求产生的1~40 MHz频段I、Q两路正交信号的设计要求。

2.电路结构工作机理

(1)放大电路原理图

由于AD9854输出信号幅度仅200~300 mV,需要对其进行1~40 MHz通带内平坦放大,考虑到后级AD835输入信号会衰减3 dB左右,而输入AD835信号在1V左右为宜,所以此级放大电路需放大10倍以上,芯片增益带宽积至少需要40 M×10=400 M。TI公司的宽带放大器OPA847具有3.9 GHz的增益带宽积,±5 V供电,低噪声高压摆率,且12倍增益时稳定。所以选择OPA847放大12倍作为本级放大电路合适。

图E-1-2 OPA847放大电路图

(2)混频电路原理图

本设计以ADI公司的AD835模拟乘法器为核心设计混频电路,AD835具有250 MHz的带宽,±5 V供电,输入输出电压范围符合本系统设计要求,混频效果较好,所以选择AD835作为混频模块。

图E-1-3 AD835混频电路图

(3)低通滤波电路原理图

① 低通滤波前级放大电路:选用直流性能较好的OP07作为前级放大电路可有效放大直流分量供后级测量,还可一定程度上滤除高频。

图E-1-4 OP07放大电路图

② 无源低通滤波电路:选用5阶巴特沃斯滤波器构建无源网络,实现低通滤波得到直流分量的效果。

图E-1-5 无源低通滤波电路图

3.核心电路设计与仿真(RLC网络设计与计算)

(1)理论计算

根据LC谐振原理,![]()

考虑到现有电容电感的数值,取L=1.5 μH,C=44 pF,计算得f0=19.5 MHz,经实测带宽,计算出Q值,符合题目要求。

(2)设计仿真结果

图E-1-6 设计出的RLC串联谐振电路

图E-1-7 设计出的RLC网络频率特性仿真图

图中显示幅度峰值处频率为19.712 MHz,经频标移动测得-3 dB点频率值分别为17.349 MHz和22.403 MHz。Q=19.712/(22.403-17.349)=3.90。

三、系统软件设计分析

1.系统总体工作流程

主程序流程图如图E-1-8所示。

图E-1-8 系统主程序流程图

本系统主要有扫频和点频两个功能。点频功能下,只需要设置频率,系统便可测量出I、Q两路电压,经过计算显示在液晶屏上。扫频功能下则需设置起始频率、终止频率以及步进值,系统便会循环测量I、Q两路电压,最终计算并将曲线和数据显示在液晶屏上。

2.主要模块程序设计

(1)AD9854控制模块

AD9854 是由AD 公司生产的单片DDS芯片, 它内部集成了48-Bit频率累加器、48-Bit相位累加器、正余弦波形表、12位正交数模转换器以及调制和控制电路,该芯片能够在单片上完成频率调制、相位调制、幅度调制以及I和Q正交调制等多种功能。

因此在对AD9854进行控制的时候,一定要注意设置好各引脚的初始值和时钟信号的变化量。同时,也要正确地写入频率控制字并设置相位偏移寄存器,以及读写寄存器。

(2)时钟初始模块

本设计中,由于单片机控制的模块较多,包括控制DDS、模数转换器、显示器,而各模块的进程都需要一定的反应时间,因此为了正确地读取和显示数据,时钟的设置相当重要。

(3)ADS1115控制模块

ADS1115是一种具有内部基准的超小型、低功耗、16位模数转换器,能够以高达每秒860 个采样数据(SPS)的速率执行转换操作。它具有一个可编程增益放大器(PGA),该PGA 可提供从电源电压到低至±256 mV的输入范围,因而能够以高分辨率来测量大信号和小信号。另外,ADS1115还具有一个输入多路复用器(MUX),可提供2 个差分输入或4 个单端输入。

本设计中,ADS1115需要读取两路电压信号,因此我们采用两路差分输入。对ADS1115芯片的控制,包括开始ADC通信、指向转换结果寄存器、配置A/D转换芯片、读A/D转换结果、将模拟量采集转化为数字量等。

(4)LCD320240显示模块

LCD320240使用功能强大的RA8835 作为控制器,4位显示数据线,传输数据迅速;具有强大的作图功能;支持文本显示、图形显示以及图文混合显示;具备简捷的MPU 接口和功能齐全的控制指令集。

LCD320240共有20个输出引脚,因此在引脚配置时应注意不能搞混,且在不同的状态下,控制字也不相同。在基本函数中将各类显示函数都书写完整,这样主程序中可以直接调用这些函数。基本函数包括液晶屏的初始化、写命令、写数据、清屏、光标定位、字符串显示、画网格、显示图片、画直线和正弦波等基本图形。

四、竞赛工作环境条件

1.设计分析软件环境

竞赛期间,本组主要使用了Multisim仿真软件、IAR单片机开发平台、Altium Designer绘制PCB板图软件等。

2.仪器设备硬件平台

测试仪器如表E-1-1所示。

表E-1-1 测试仪器列表

五、作品成效总结分析

1.系统测试性能指标

表E-1-2 正交扫频信号源输出幅度 (单位:频率/MHz 幅度(峰峰值)/V 相位/°)

幅度平衡误差计算:

最大为(1.07-1.06)/1.06=0.94%

幅度平坦度计算:

I路:(1.12-1.07)/1.07=4.6%

Q路:(1.11-1.06)/1.06=4.7%

相位差误差:

(95-87)/87=9.1%

表E-1-3 RLC网络特性测试 (输入值:1 V) (单位:频率/MHz 幅度/mV)

表E-1-3中的-3 dB频率值是在找到峰值后寻找0.707峰值点的频率得到的。

中心频率测量:

f0=19.5 MHz

有载品质因数计算:下限截止频率为17.4 MHz,上限频率为22.5 MHz

Q=19.5/(22.5-17.4)=3.823

有载最大电压增益计算: 980/1000=0.98,即-0.17 dB

表E-1-4 低通滤波器特性测试 (输入值:1 V) (单位:频率/kHz 幅度/mV)

从表E-1-4可以得到,-3 dB截止频率为970 kHz,能将混频后的上边频完全滤去。

表E-1-5 RLC网络点频测量 (单位:频率/MHz, 增益/dB,相位/°)

从上表可以分析出,其幅频特性与前文“RLC网络特性测试”表中幅频特性基本一致。中心频率在19~20 MHz之间,-3 dB带宽为5 M左右。

2.成效得失对比分析

根据上述测试数据,可以得出以下分析结果:

(1)正交扫频信号在1~40 MHz通带内平坦,I、Q两路正交信号幅度平衡,相位差基本恒定在90°附近,相位差误差偏大。

(2)RLC网络设计参数基本满足题目要求,使用本系统对网络特性测试,数据接近实际值。

(3)低通滤波器实际性能良好。

综上所述,本系统基本达到设计要求。

3.创新特色总结展望

系统基本完成题目的基本要求和发挥要求。信号发生部分可以产生两路幅度平坦、相位差恒定的正交扫频信号,信号放大、混频、滤波效果良好。网络部分制成符合题目对中心频率和Q值等要求的RLC谐振网络。测量显示部分实现高精度数据采集,绘制出较高分辨率的幅频特性曲线和相频特性曲线,显示中心频率和-3 dB带宽。

在设计过程中我们发现,阻抗匹配是一个很关键的问题。前后级间的阻抗匹配有利于实现通带内平坦,避免器件本身的工作状态产生明显的影响。不匹配的网络会造成高频电磁波的反射、叠加,使得产生的正交信号带内不平坦。本系统测试数据时使用泰克示波器DPO4504,其通道输入阻抗可调为50Ω,也是为了使正交信号源输出阻抗与示波器输入阻抗相匹配,用通道阻抗不匹配的示波器测出的平坦度明显不如通道阻抗匹配的示波器。

六、参考资料

陶益凡,唐慧强,黄勋,等.基于AD9854的信号发生器设计.微计算机信息, 2006 (02Z): 241-243

Li H, Chen X, Huang B, et al.High Bandwidth Visible Light Communications Based on a Post-Equalization Circuit.2014

INPUT R F, OUTPUT I F, MIXER I, et al.Mixers and Modulators.

吴凌燕.基于 Mulitisim11 的串联谐振电路特性研究.国外电子测量技术, 2011, 30(8): 84-86

鞠文云.基于 AD9850 的频率特性测试仪.硅谷, 2009 (21)

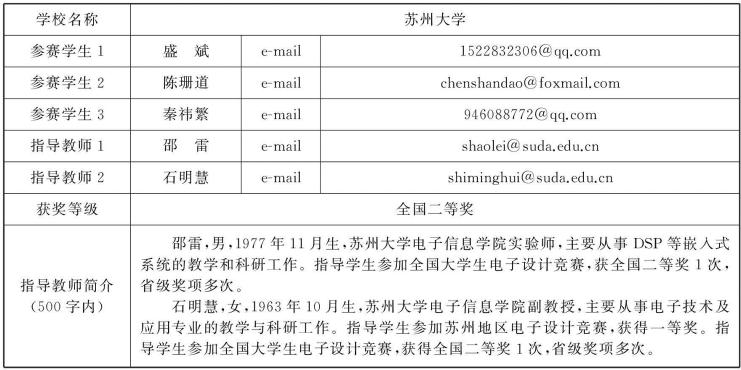

报 告 2

基本信息

一、设计方案论证分析

1.方案比较与选择

(1)信号源模块设计

方案1:信号源部分用FPGA完成数字频率合成,在FPGA内部完成系统时钟设置,频率字设置,相位累加,数据存储,并利用高速D/A输出双路正交信号。但本次设计要求的扫频速度较快,且输出频率最高达40 MHz,对FPGA的内部时钟频率要求较高,而FPGA内部的块存储器容量有限,难以实现较高的频率分辨率。FPGA本身并不包含D/A,因此需要外接高速D/A,市售常用的D/A速率无法达到题目要求,该方案成本较高,工作稳定性和输出信号质量很难满足本次设计的测量要求,故放弃方案1。

方案2:采用美国AD公司生产的DDS芯片AD9854来实现信号源。AD9854内部有高速的数字锁相环,可以对片外时钟进行高速倍频,作为内部的系统时钟,最高频率可达300 MHz;有两个48位的频率控制字寄存器,能够实现的最高频率分辨率约为fS/248≈10-6 Hz;能够输出的最高频率理论上可达到fS/2=150 MHz;输出信号的信噪比在100 MHz时可达80 dB。AD9854本身包含两路正交的输出信号通道,采用方案2。

(2)乘法器模块设计

方案1:输出的双路正交信号和待测网络的响应信号分别用高速A/D进行采样,然后送入单片机或者FPGA中进行数字相乘,再进行数字FIR低通滤波,最后对滤波后的直流信号进行运算处理,得到待测网络的幅度和相位频率信息。考虑到信号最高频率可达到40 MHz,为保证奈奎斯特采样定律,至少应使用80 MHz采样率的A/D芯片,但高速A/D芯片成本高,并且外围电路的设计和PCB布局布线要遵照高速数字设计规范,难度较高。同时采样后的高频信号直接进行数字乘法和数字低通滤波,运算量很大,单片机的运算速度根本无法满足要求,因此方案1不合适。

方案2:使用高速模拟乘法器芯片AD835,AD835是美国AD公司生产的四象限电压输出模拟放大器,有两个差分电压信号输入端X和Y,另有一个直流偏置信号输入端Z,均为高输入阻抗,信号电压W输出端最高可输出±2.5 V的电压,最高可带25 Ω的负载。该芯片一般采用±5 V双电源供电,输出信号电压W=XY+Z,输出信号的3 dB带宽最高达到250 MHz;混频后输出信号的频谱纯度高,X通道和Y通道的馈通在200 MHz以下低于-50 dB;构成乘法器电路时所需的外围元件很少,电路简单。DDS输出的两路正交信号和待测网络的响应信号在乘法器中相乘后再经过模拟低通滤波器,可以获得直流信号,再送入A/D进行采样,最后送入单片机进行数据处理分析。采用本方案,模拟乘法器电路设计简单可靠,成本较低,模拟低通滤波器输出是直流信号,可以使用低速的高精度A/D进行采样,外围电路稳定可靠,对单片机的处理速度要求不高,整个设计指标均能完成,最后选择方案2。

2.系统结构和工作原理

由于DDS信号源输出信号幅度相对较小,在DDS信号源之后加两路宽带放大器,为提高两路正交信号的对称度,两路宽带放大器的外部元件参数和PCB走线应尽可能对称,并且放大器在1~40 MHz频率范围内应当具有尽可能平坦的通带增益。此外,AD9854具有增益设置功能,可以利用软件编程微调信号增益来补偿放大器通带内的增益起伏。

假设信号源模块输出的两路正交信号分别为:

U1=Acos(ωt), U2=Asin(ωt)

其中用A表示信号幅度,ω表示信号频率,信号的初始相位假设为零。

U1信号作为待测网络的激励信号,待测网络是线性网络,输出的响应信号可以表示为:

U0(t)=AH(ω)cos(ωt+φ(ω))

其中H(ω)是待测网络的幅频特性,φ(ω)是待测网络的相频特性。

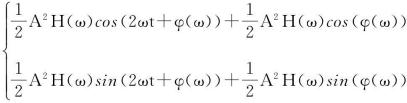

待测网络的激励信号与信号源输出的两路正交信号在乘法器中相乘后的输出为:

U0U1=

输出信号中第一项为高频分量,第二项在每个频率点对应一个直流分量。

乘法器的两路输出信号经过低通滤波器后,高频分量被滤除,上下两路的输出分别是:

![]()

根据上面两个公式可以得到:

![]()

因此,只要对信号源输出信号的频率ω进行扫描,就可以得到在不同频率ω处待测网络的增益信息和相位信息。在扫频模式下,每隔100 kHz记录下一个频率点的响应,即可绘出待测网络的幅频与相频曲线。

在实际设计中先将余弦信号送入被测网络,被测网络的输出分为两路,分别与原正弦、余弦信号在模拟乘法器AD835中进行相乘运算,再经过低通滤波滤出直流分量。由于乘法器输出的直流分量幅度较小,约20~50 mV,为提高测量精度,需要加一级直流放大器。直流放大器设置10倍增益,将滤波后的直流信号放大到200~500 mV,然后送入A/D进行采样。采样后的数字信号送入单片机进行数据处理和分析,得到待测网络的频率与相位信息,通过320×240分辨率的TFT彩屏绘制出被测网络的幅频、相频曲线。系统总体框图如图E-2-1所示。

图E-2-1 系统总体框图

二、核心部件电路设计

1.DDS信号源模块设计

DDS信号源模块采用DDS芯片AD9854,利用官方推荐的原理图进行外部电路设计。AD9854的电源需要良好地去耦,尤其是锁相环路部分,如果电源高频纹波过大,会使内部的系统时钟不稳定。PCB布线时要注意减小信号线长度,减小电路板面积,采用贴片元件,减小引线电感和分布电容。外部电源供电分别经过两个稳压芯片滤波,得到芯片的数字电源和模拟电源,使数字电源和模拟电源进行隔离。数字地和模拟地各自分开,最后一点接地。电路板上采用50 MHz的有源时钟提供外部参考时钟,DDS的四路信号输出分别经过多级的巴特沃茨滤波器进行低通滤波,滤除和信号频率对称的镜像干扰。四个滤波器的电容和电感参数选择尽可能做到对称,减小由于信号通道上的滤波器频率响应不均衡导致的输出信号幅度不均衡,信号的输出接口统一采用标准的SMA接口,输出信号线选择特征阻抗为50 Ω的同轴电缆,使信号的输出阻抗和传输线的特征阻抗匹配,减小信号的反射和衰减。

2.低通滤波器电路设计

DDS信号源的输出信号存在一个关于系统时钟对称的镜像频率干扰,因此需要外加低通滤波器滤除镜像干扰信号,我们使用官方推荐的高阶巴特沃茨低通滤波器,电路图和仿真的波形分别如图E-2-2,图E-2-3所示。从仿真波形中可以看到,该滤波器的3 dB带宽超过100 MHz,带外衰减超过80 dB,可以很好的滤除镜像干扰信号,提高DDS信号源输出信号的频谱纯度。两个正交信号通道的低通滤波器的电容和电感选择应尽可能对称,可以减小滤波器频响不对称造成的正交信号通道幅度和相位差。

图E-2-2 巴特沃茨低通滤波器电路原理图

图E-2-3 仿真的滤波器幅频响应

3.宽带放大电路设计

DDS信号源输出电压的峰峰值不到400 mV,因此需要外加宽带放大电路。宽带放大电路设计采用TI公司的电流反馈型运算放大器THS3001。使用电流反馈型运放构成放大器时,带宽和增益不受带宽增益积的限制,反馈电阻R2可设置带宽,带宽和R2的阻值成反比,但R2不可取很小,否则会导致幅频响应在靠近截止频率附近处出现明显的上翘,放大器的相位稳定裕量减小,严重时会导致放大器的自激振荡。电阻R1设置增益,电源用±5 V双电源供电。本设计中需要将双路正交信号放大6倍,以满足信号源输出幅度的要求。电路原理图如图E-2-4所示。用TI公司的仿真软件tina-9进行仿真的电路幅频响应,如图E-2-5所示,可以看到电路3 dB带宽大约为280 MHz,在1~40 MHz范围内增益的波动不超过0.1 dB,完全满足增益波动不超过5%的要求。制作出的宽带放大器经过实测,在1~40 MHz范围内增益的波动不超过0.3 dB。

图E-2-4 THS3001放大电路原理图 图E-2-5 放大电路仿真的幅频响应

4.RLC待测网络设计

待测网络电路如图E-2所示,其中R代表电感的损耗,Ro表示前级DDS信号源的输出阻抗,大约为50 Ω,Ri表示负载,即网络测试仪接收响应信号电路的输入阻抗,一般为50 Ω。

待测网络是一个典型的串联谐振网络,中心频率为:

![]()

最大电压增益出现在中心频率处,![]() ,题目要求Amax≥-1 dB,因此可以估算出电感的损耗电阻R不能超过6 Ω。有载品质因数:

,题目要求Amax≥-1 dB,因此可以估算出电感的损耗电阻R不能超过6 Ω。有载品质因数:

![]()

根据以上两式可以计算出C≈20 pF,实际C取18 pF,L取3.51 μH,仿真的LC谐振回路的幅频特性曲线如图E-2-6所示,电感的等效损耗电阻取6 Ω。仿真的中心频率约为20 MHz,3 dB带宽约为4.78 MHz,中心频率处的增益约为-0.5 dB,满足题目要求。

若使用磁导率较高的铁氧体加空心线圈来绕制电感,容易出现磁饱和,并且空气气隙的存在会使电感在高频时有较大损耗,在中心频率处的增益会低于-1 dB,因此,采用较粗的漆包线来直接绕制空心线圈作为电感,实验测量的LC谐振回路幅频特性曲线如图E-2-7所示,谐振回路的中心频率约为20.34 MHz,中心频率处的最大增益约为-0.22 dB,3 dB带宽约为5 MHz,有载品质因数约为4, 均满足题目要求。

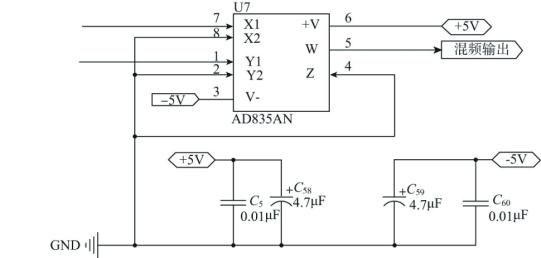

5.乘法器电路设计

采用高速模拟乘法器芯片AD835,输出信号的基本传递函数为W=XY+Z。两个信号输入端口是双端差分输入,在实际电路中将X2、Y2接地,实现单端信号输入。直流信号偏置输入端Z接地,即可实现两路输入信号的乘法功能。乘法器采用±5 V双电源供电,由于输入信号频率较高,乘法器的电源不仅需要电容去耦,还要加入磁珠以抑制电源线上产生的高频干扰。需要指出的是,乘法器输出存在一定的直流偏移,该直流偏移量并不是一个常数,而是与输入信号的频率、信号幅度以及工作温度都有关系,直流偏移量的变化会影响系统最后的频率响应测试精度。因此需要通过测量时的初始化校正和软件前期测量调试来进行修正。

图E-2-6 仿真的待测网络幅频特性曲线

图E-2-7 实际测量的待测网络幅频特性曲线

6.低通和放大及电平调整电路设计

低通滤波器的主要作用是滤除乘法器输出的高频信号分量,得到包含待测网络增益信号和相位信息的直流分量。由于乘法器输出的直流分量幅度较小,约20~50 mV,为提高测量精度,需要加直流放大。直流放大电路采用低失调电压运放OP27芯片,为减小输入端噪声,采样反相放大,设置增益为10倍,将滤波后的直流信号放大到200~500 mV。由于选用的A/D芯片只支持单极性信号输入,两路直流分量的极性无法事先确定,所以在进入A/D转换器芯片之前需要将I与Q分量信号进行电平移动。因此在直流放大电路后面加入了一级电平调整电路。由LM385电压基准芯片提供2.5 V的基准电压,加到AD817的同相输入端,AD817设置1倍电压增益,AD817的输出信号是固定的直流偏置电压(2.5 V)和放大后的直流电压叠加,保证输入到A/D采样芯片的直流信号是单极性。电路原理图如图E-2-8所示。

图E-2-8 低通放大和电平调整电路

三、软件系统设计

本系统中共用两片MSP430F149,一片用作DDS信号源的控制器,通过对AD9854编程设置,实现题设要求DDS输出各个功能模块,并以液晶屏幕12864模块及键盘交互的模式提供友好的人机界面,方便频率特性测试仪的各项功能设置。另一片MSP430F149位于整个系统的后端,实现数据处理,通过对被测网络的测量结果进行数据处理和分析,显示被测网络单频点的幅度和相位信息,同时绘制出被测网络的幅频及相频特性曲线。两片单片机之间通过串口通信协议进行通信,主单片机在设置完扫频参数后可实时告知数据处理端的单片机当前的扫频频率,便于后者将获取的幅度相位数据与扫频频率一一对应,从而成功将被测网络特性曲线描绘至TFT屏幕。

单片机设置A/D芯片的采样频率为1 kHz,在获得采样的I、Q两路直流信号后,软件处理时首先对采样得到的直流信号取50点平均,滤除干扰噪声;随后减去固定的2.5 V直流偏置信号,通过前期测量调试获取的乘法器直流漂移信号对平均后的采样值进行拟合修正,尽可能减小乘法器直流漂移引起的叠加误差;最后通过查表计算,获得各个扫频频率点的幅度和相位信息。图E-2-9和图E-2-10分别为DDS信号源控制端的MSP430F149单片机与数据处理端的MSP430F149单片机的软件处理流程图。

图E-2-9 DDS信号源主控单片机工作流程图

图E-2-10 后端数据处理和绘图单片机工作流程图

四、竞赛工作环境条件

测试所使用的仪器设备有:直流稳压稳流电源:型号GPD—3303。200M的DDS合成信号发生器:型号EE1461。五位半数字万用表:型号 FLUKE8808A。200 MHz数字存储示波器:型号Tektronix TDS2022B。2.5 GHz高性能射频一体化矢量网络分析仪:型号AV3620A。

五、测试方案分析

1.DDS信号源输出信号幅度和相位测试

将DDS信号源模块的两路正交输出信号分别接示波器的两个输入通道,用示波器测量两路信号的幅度和相位差,信号的输出端口采用标准的 SMA接口,信号线用同轴线,示波器的通道选择50 Ω输入,和同轴线的特征阻抗匹配。

表E-2-1 DDS输出信号幅度和相位测试

从上表测试数据中可以看出,两路正交通道的幅度平坦度小于4%,相位误差也在2°以内。需要说明的是,示波器输入信号通道本身的电路频率响应存在着一定的起伏,并且两个通道的频率响应之间也存在微小的差异,因此可以认为测量数据完全满足题目基本部分的要求。频率在40 MHz时输出的双路正交信号时域波形如图E-2-11所示。

图E-2-11 信号源输出的双路正交信号(频率为40 MHz)

图E-2-12 实测的待测网络相频特性曲线

2.RLC待测网络测试

用商用的矢量网络分析仪测量的待测网络中心频率约20.34 MHz,有载最大增益约为-0.22 dB,3 dB带宽约为5.02 MHz,有载品质因数为4,完全满足题目要求,实测的待测网络相频特性曲线如图E-2-12所示。

3.待测网络的频率特性测试

使用商用的高性能矢量网络分析仪测量RLC待测网络的频率特性数据;再用自制频率特性仪测量相应数据,记录在同一张表中,对比两种测量方式的数据测量误差。数据表格如下(AV1、φ1为商用网络分析仪的测量数据,AV2、φ2为自制频率特性仪的测量数据):

表E-2-2 频率特性测试

从表中数据可以看出,和商用矢量网络分析仪相比较,测试的增益误差绝对值最大为1.35 dB,大部分的测量增益误差绝对值在0.5 dB以内。测量的相位数据误差较大,主要是由乘法器电路的随机直流偏移误差引起的,在计算相位时,乘法器很小的直流偏移会给相位计算带来很大的误差;另外单片机通过查表计算反正切函数值时由于存储的数据有限,字长效应和存储数据量不够,也带来一定的误差。由于竞赛时间有限,在处理直流偏差的校准时因前期调试校准的数据量不够,带来了较大的相位测量误差。实际测试时,扫频时间满足要求,能同时显示出待测网络的中心频率与-3 dB带宽。

六、参考资料

康华光.电子技术基础模拟部分.5版.北京:高等教育出版社,2005

张肃文.高频电子线路.4版.北京:高等教育出版社,2004

洪利,章扬,李世宝,等.MSP430单片机原理与应用实例详解.北京:北京航空航天大学出版社,2010

黄根春.全国大学生电子设计竞赛教程——基于TI器件设计方法.北京:电子工业出版社,2011

报 告 3

基本信息

一、技术方案分析比较

1.正交扫频信号源设计方案

方案1:直接模拟频率合成技术是用一个晶体参考源,经过分频、混频和倍频来得到各种频率信号,输出频率的稳定性和精度与参考频率相同。直接模拟频率合成技术简单易行、频率转换时间短、相位噪音低,但因采用了大量的分频、倍频和滤波等模拟元件,使合成器的体积大,易产生杂散分量,元件的非线性影响难以抑制。

方案2:基于锁相环的频率合成技术:因为锁相环相当于窄带跟踪滤波器,所以PLL频率合成技术能够很好地选择频率,而且频率的长期和短期稳定性都很好。但PLL有惰性,频率分辨率和频率转换时间相互矛盾,频率转换时间较长,压控振荡器引起的噪声也较大。

方案3:直接数字合成技术:采用数字化DDS芯片AD9854。DDS 结构由5个主要部分构成:相位累加器、波形存储器、数模转换器、低通滤波器以及参考时钟,其结构如图E-3-1所示。AD9854是AD公司采用先进的DDS技术生产的具有高集成度的DDS器件,最高工作时钟为300 MHz,其电路结构允许同步正交输出信号的频率最高达到150 MHz。它具有双48位可编程频率寄存器(也即理论上其分辨率可以达到![]() ≈10-6Hz),双14位可编程相位寄存器以及两个内部高速高性能正交数模转换器,通过微处理器的适当控制便可产生合适的正交正弦波信号。该方案产生的正交信号频率稳定性较好,分辨率高,操作简易。

≈10-6Hz),双14位可编程相位寄存器以及两个内部高速高性能正交数模转换器,通过微处理器的适当控制便可产生合适的正交正弦波信号。该方案产生的正交信号频率稳定性较好,分辨率高,操作简易。

图E-3-1 DDS原理图

综合以上论证比较:与直接模拟频率合成及锁相环频率合成相比,采用DDS芯片合成正弦信号的频率建立与切换简单,频率单一,频率覆盖范围广,分辨率高,可控性强,功能扩展能力大,故采用方案3。

2.混频模块设计方案

混频模块实现的功能是将两路信号相乘,这里选择AD公司的乘法器AD835。AD835是一款完整的四象限电压输出模拟乘法器,采用先进的介质隔离互补双极性工艺制造。它产生X和Y输入电压的线性乘积,3 dB输出带宽为250 MHz(小信号上升时间为1 ns)。其中X,Y均为高阻输入,输入范围-1~1 V。输出电压可驱动低至25 Ω的负载,输出范围-2.5~+2.5 V。该乘法器外围电路简单,给整个系统的设计带来了便捷,因此我们就采取此种方案,不再分析其他方案。

二、系统结构工作原理

1.系统结构

整个系统由微处理器STM32F103控制核心、AD9854正交信号源模块、RLC串联谐振网络、AD835混频模块、滤波模块、A/D采样模块、显示模块组成,系统的结构框图如图E-3-2所示。

图E-3-2 系统的结构框图

2.基本原理分析

图E-3-2中所示的正交扫频信号源产生两路信号:

Ul1=Acos(ωt)

Ul2=Asin(ωt)

其中一路信号Acos(ωt)作为输出加载到被测网络上,由于被测网络是由R、L、C组成的线性网络,被测网络输出信号仍是频率为ω的正弦波(此时幅度与相位发生了变化):

Uo=Bcos(ωt+φ)

Uo与Ul1、Ul2在乘法器处做乘法操作得到两路信号:

![]()

![]()

上述两路信号Uo1、Uo2都是由低频分量与高频分量组成,经过低通滤波后留下低频分量,再由A/D转换器转换后得到:

![]() cosφ

cosφ

![]()

对于被测网络来说,网络的增益是正弦波的幅值比:

![]()

网络的相移为φ,结合上面I、Q、AV得到AV、φ为:

![]()

![]()

这样,网络传输特性就可以通过不同频率下的A/D采样值I、Q以及输入信号幅度A来获得。实际上我们正是通过正交扫频信号源产生1~40 MHz的扫频信号,同时采集I、Q两路信号,得到1~40 MHz频率范围内网络的幅频、相频特性曲线。

三、核心部件电路设计

1.电路结构工作原理

(1)AD9854正交信号源模块

AD9854输出的两路正交信号的幅度较小,为了满足系统设计需求,将这两路信号进行放大,由于本系统的带宽比较宽(1~40 MHz),选取宽带放大器AD8009。AD8009是一款超高速电流反馈型放大器,压摆率可达到5 500 V/μs,上升时间仅为545 ps,因而非常适合用作高频放大器。本模块的部分原理图如图E-3-3所示,放大器放大之后的信号经50 Ω的电阻输出,输出信号接口为SMA接口,信号线是特征电阻为50 Ω的高频线。

图E-3-3 宽带放大器AD8009原理图

(2)混频模块

混频模块采用乘法器AD835为核心,电路原理图按照官方文档给出的推荐电路图,如图E-3-4所示。

图E-3-4 混频电路

其中X2,Y2,Z接地,X1,Y1接入要进行乘法操作的两路信号,W为混频输出信号。

(3)滤波模块

低通滤波器的作用是阻高频,通低频。低通滤波器包括有源低通滤波器和无源低通滤波器,无源低通滤波器通常由电阻、电容组成,也有采用电阻、电感和电容组成的。有源低通滤波器一般由电阻、电容及运算放大器构成。本系统中使用有源低通滤波器,将由混频器输出的混频信号中的高频部分滤去,仅留下与被测模块相关信息的低频部分,将低频信号经采样后输入到STM32中做处理,就可得到被测模块幅频特性与相频特性。该系统低通滤波器主要由MAX297与TL084构成,具体如图E-3-5所示。

图E-3-5 低通滤波

(4)微处理器STM32与采样

本系统使用的微处理器为STM32F103, STM32F103是一款增强型系列微型处理器,它使用高性能的ARM Cortex-M3 32位的RISC内核(工作频率为72MHz),内置高速存储器(高达128K字节的闪存和20K字节的SRAM),丰富的增强型I/O端口和连接到两条APB总线的外设。该处理器包含2个12位的ADC、3个通用16位定时器和一个PWM定时器,还包含标准和先进的通信接口:2个I2C和SPI、3个USART、一个USB和一个CAN。综合考虑工作频率、内存配置、片上外设等要素,该微处理器是本系统设计的最佳选择。其中2个12位的ADC刚好可以用来为A/D采样模块提供模数转换器。

(5)显示、交互模块

本系统使用3.2英寸带触控的TFT屏。提供网络特性测试参数、特性曲线的显示,以及提供人机交互界面,所有操作都可以通过触摸屏完成,十分便捷。

2.核心电路设计仿真

按题目要求要制作一个RLC串联谐振电路作为被测网络,其中R1和R0分别为频率特性测试仪的输入阻抗和输出阻抗,制作的频率特性测试仪可对其进行线性扫频测量。被测网络通带中心频率为20 MHz,有载品质因数为Q=4,设中心频率为f。

对于RLC串联电路,有:

![]()

所以,谐振频率为:

![]()

而有载品质因数为:

![]()

题中要求f=20 MHz, Q=4, Ri=Ro=50 Ω,有载最大增益:

这使得R要小于12 Ω,这里取R=2 Ω。于是得到:

L=3.3 μH, C=20 pF。

由此在Multisim下进行仿真得到串联谐振网络的幅频、相频特性曲线,如图E-3-6所示。

图E-3-6 RLC串联谐振网络幅频、相频特性(100 kHz~40 MHz)

四、系统软件设计分析

1.系统总体工作流程

系统主程序流程图如图E-3-7所示,系统首先进行初始化工作,包括对微处理器STM32F103自身的初始化、AD9854的初始化、触摸屏显示以及中断的初始化,随后程序进入while(1)循环中等待中断事件来唤醒程序。这里的中断事件来自触摸屏,触摸屏上的触摸操作包括进行测试参数设置以及测试功能虚拟按键的按下,这些操作都能产生中断。一旦中断产生,主程序立即跳出循环,判断中断事件,响应中断。

图E-3-7 系统主程序流程图

2.主要模块程序设计

如图E-3-7所示的流程图中,整个程序分为三大模块,分别为:初始化模块、中断模块、显示交互模块。

(1)初始化模块

程序开始后首先进行STM32F103、AD9854以及触摸屏的初始化。STM32F103的初始化即设置好微处理器时钟频率、通信端口等;AD9854的初始化,即使AD9854复位、设置好各个控制寄存器、调整两路正交信号的幅度相差等;触摸屏的初始化,即设置好触摸屏上的界面显示,更好地控制相应的屏幕中断。

(2)中断模块

初始化工作完成后程序进入一个While(1)循环中等待来自屏幕的中断,当触摸屏上的虚拟按键被按下后,产生中断,程序首先判断中断对应的事件是什么,共有五大类事件,分别是:

① 点频输出:包括频率设置事件和输出事件。频率设置事件:在屏幕上点击频率值的步进按钮而产生的中断事件,用来完成频率值的输入;输出事件:在屏幕上点击频率更新按钮而产生的中断事件,用来通知STM32F103将刚输入的频率值更新到AD9854中,使正交信号源产生频率值对应的正交信号。

② 扫频输出:包括扫频范围设置事件、扫频步长设置事件以及输出事件。扫频范围设置事件: 在屏幕上点击频率范围初始值、终止值的步进按钮而产生的中断事件,用来完成扫频范围的输入;扫频步长设置事件: 在屏幕上点击频率步长的步进按钮而产生的中断事件,用来完成扫频步长的输入;输出事件:在屏幕上点击扫频开始按钮而产生的中断事件,用来通知STM32F103安装刚输入的扫频信息控制正交信号源,使正交信号源输出扫频信号。

③ 点频测量:包括频率设置事件和测量事件。频率设置事件:在屏幕上点击频率值的步进按钮而产生的中断事件,用来完成频率值的输入;测量事件:在屏幕上点击点频测量按钮而产生的中断事件,用来通知STM32F103完成该频率点下的网络特性测量,并在屏幕上显示相关信息。

④ 扫频测量:包括扫频范围设置事件、扫频步长设置事件以及测量事件。这里的扫频范围设置事件、扫频步长设置事件同扫频输出是一样的,不再详细描述。测量事件:在屏幕上点击扫频测量按钮而产生的中断事件,用来通知STM32F103完成扫频范围内的网络特性测量,并在屏幕上显示相关信息。

⑤ 结束事件:测量结束。

(3)显示交互模块

程序初始化时对触摸屏界面进行初始化,将屏幕分块,分别为:测试信息输入区和测试结果显示区。测试信息输入区提供测试参数步进虚拟按钮、测试功能开始虚拟按钮,在测试参数步进虚拟按钮、测试功能开始虚拟按钮被按下时,都会产生屏幕中断。测试完成后,网络特性曲线与参数将在测试显示区显示。显示交互模块将实现以上功能,提供测试结果的显示以及测试进程的控制。

五、竞赛工作环境条件

1.设计分析软件环境

设计过程中主要使用的软件有:Multisim、MDKARM开发平台、Altium Designer等。

2.仪器设备硬件平台

所使用的硬件设备如表E-3-1所示。

表E-3-1 测试仪器

六、作品成效总结分析

1.AD9854正交信号源

测量AD9854输出的正交信号在1~40 MHz 下的幅度与相差,结果是:频率稳定度小于10-4,相位绝对误差小于5%,相位平衡误差小于5%。信号峰峰值大于1 V,接近3 V。唯一不足的是,信号幅度的平坦度大于5%,这反映在接近40 MHz时信号幅度明显增大,分析原因可能是其他频率的干扰被放大。

对于信号源的扫频输出,前文中的设计指标都可实现。

2.RLC串联谐振网络

我们根据前文的理论分析选取电容、电感、电阻,发现中心频率不对,考虑到器件的分布电感、电容,通过实验最终选取的RLC值分别为2 Ω、3 μH、18 pF。得到的中心频率在19.7 MHz左右,完全满足设计目标。

3.频率特性的测试

我们测量了1~40 MHz下网络的特性曲线,得到的结果及误差见表E-3-2,由表E-3-2可以看到除了个别点,幅频测量绝对误差都不大于0.5 dB,相频测量绝对误差都不大于5°,最大增益大于-1 dB,中心频率在19.9 MHz基本满足设计要求。其中,幅频测量误差较大,这在前文也有所提及,可能是由于AD9854输出的信号幅度稳定度不够高。

表E-3-2 频率特性

七、参考资料

王文理,王丽.DDS在数字频率特性测试仪中的应用.国外电子元器件,2007

施智强,何欣,唐铭杰,等.频率特性测试仪.国外电子元器件,2008

张春水,张佳培.基于单片机和FPGA的频率特性测试仪.电子设计工程,2009

全国大学生电子设计竞赛委员会.全国大学生电子设计竞赛获奖作品选编.北京:北京理工大学出版社,2005

报 告 4

基本信息

一、设计方案工作原理

1.设计方案

(1)幅频和相频特性测试方案

方案1:利用公式H(s)=R(s)/E(s),以冲击函数为激励,则输出信号的拉氏变换与系统函数相等。但是产生性能很好的冲击函数比较困难,需要对采集的数据做FFT变换,需要占用大量的硬件和软件资源,且精度也受到限制。

方案2:扫频测试法。当系统在正弦信号的激励下,稳态时,响应信号与输入激励信号频率相同,其幅值比即为该频率的幅频响应值,而两者的相位差即为相频特性值。采用频率逐点步进的测试方法,无需对信号进行时域与频域的变换计算,通过对模拟量的测量与计算完成,且精度较高。

方案3:利用零中频正交解调原理,用两个乘法器和低通滤波器分别对经过RLC网络之后的两路正弦波进行零中频正交解调,从而提取出两路已调信号中包含的调制信号的信息,信息包含的特性即反映了RLC网络的阻抗特性。但是这种方法要求本振信号与载波信号保持严格的同频同相,要求两路载波信号完全正交,因此对正交扫频信号源的要求较高。

根据题目的相关要求,选择方案3。

(2)正交扫频信号源方案

方案1:采用锁相环(PLL)频率合成信号源,PLL频率合成器的输出频率可以按需要步进地变化,锁定后,其输出频率可以达到与参考频率同量级的频率精度和稳定度。但其电路连接较为复杂,频率调整麻烦。

方案2:使用FPGA编程,运用DDS原理产生系统所需波形信号源。此法成本低廉,但其性能受晶振频率精度限制较大,外部对应处理电路较为复杂。

方案3:使用集成DDS芯片AD9851模块实现扫频波形发生,操作简单,频率精度与范围都可达到较高水平,波形稳定度高。

综上,我们采用方案3。

(3)显示与控制方案

方案1:选用MSP430单片机,该款单片机具有低功耗,抗干扰能力强的特点,编译器功能强大,例程丰富,是一款非常流行的MCU,但是该款I/O口的电平是3.3V的,使用外围器件的时候要考虑电平的匹配问题。

方案2:选用ATMEGA16L单片机,该款单片机具有丰富的程序类库,片上资源丰富,管脚电平是通用的5.5V,在使用的过程中不需要考虑电平兼容性的问题。

由于本系统要使用许多的外设器件,结合两款单片机的特点,选择方案2。

(4)低通滤波器方案

方案1:用无源元件(R、L 和C)组成带通滤波电路,此方法虽然成本低,但通带内的信号有能量损耗,负载效应比较明显,使用电感元件时容易引起电磁感应,系统不稳定,效果较差。

方案2:运用RC及运放搭建二阶巴特沃斯带通滤波器,集成度高,反应动作迅速,多级级联时相互影响较小,且幅频响应在通带中具有最大平坦度。

有源滤波器比无源滤波器设计更为灵活,且具有良好的隔离性能,系统稳定,体积小,因此选用方案2。

(5)方案描述

本系统使用两片DDS芯片AD9851产生两路正交信号,用AD603程控运放搭建程控放大电路,检波电路以检波管为核心,配合RC元器件搭成。乘法器电路选用AD835乘法器芯片搭建,相乘之后的信号通过用NE5532运算放大器搭建的有源低通滤波器之后提取出与网络阻抗特性有关的直流分量,该直流经过AVR单片机片上的ADC采样转换成数字信号,并在单片机内部进行计算,运算的结果通过12864液晶屏显示出来,按键输入是为了控制扫频范围和定频测量。操作功能都通过单片机控制实现,同时该系统还带有自动休眠的功能,当该测量仪10分钟时间没有任何操作的时候,会自动进入休眠状态。

图E-4-1

2.工作原理

(1)系统原理

系统由正交扫频信号源产生两路相互正交的载波Acos(ωt)和Asin(ωt),其中Asin(ωt)经过被测网络之后幅值和相位都发生变化,设被测网络的输出端信号表达式为:

X(t)=Bcos(ωt+θ)

其中B为变化后的信号幅值,θ为产生的相位差。

信号经过被测网络之后分别与两路载波相乘:

上路:

![]() AB[cosθ+cos(2ωt+θ)]

AB[cosθ+cos(2ωt+θ)]

下路:

![]() AB[sinθ+sin(2ωt+θ)]

AB[sinθ+sin(2ωt+θ)]

经过低通滤波器之后得到:

![]() ABcosθ

ABcosθ

将I与Q相除得到:

![]() =tanθ

=tanθ

这样就能计算出阻抗角θ。

计算出阻抗角之后,就可以由

![]()

计算出|Z|的值,其中I是直流量,经过检波电路及A/D采样即可测得,同样的方法也可得到A的有效值。

(2)滤波器设计

本题在系统的末级需要提取与RLC网络特性有关的直流分量,所以需要加一级低通滤波器。由于有源低通滤波器在确定参数的时候自由度比较高,方便实际电路的实现,所以选择设计有源低通滤波器。设置RC参数可由电路导出多项式计算求得,但是这种方法太复杂,于是选择查看归一化表确定各级的截止频率和Q值,再进行RC参数的计算。计算参数参考的公式为:

Rf=R1=R2

C1=2QC2

![]()

本题要设计4阶切比雪夫LPF,查归一化表格得

f1:0.78926 f2:1.15327 Q1:0.61880 Q2:2.18293

将以上数据代入公式,即可计算出RC的参数。

(3)ADC设计

数模转换器(ADC)基本上是一个比例上的问题,即由ADC产生的数字值跟输入模拟量与转换器量程的比值有关,转换关系如下:

Uin/Ufullscale=X/(2N-1)

其中X是数字输出,N是数字输出的位数(ADC的位数),Uin是模拟输入量的值,Ufullscale是模拟输入量的最大值。

数模转换的转换精度计算:

Uersolution=Ufullscale/(2N-1)

本题直接使用AVR单片机片上自带的10位ADC,AVR单片机的ADC具有两个ADC寄存器:ADC控制与状态寄存器ADCSR,控制ADC的运行;ADC多路复用选择器ADMUX,控制8个测量的模拟量输入。

为了ADC以最大的精度操作,要求使用50 Hz~200 kHz之间的时钟频率,选择合适的比例分频因子以获得50 Hz~200 kHz的转换频率。由于ADC的速度比较慢,如果处理器在ADC转换数据时处于等待状态,会浪费时间,所以ADC通常采用中断模式。ADC初始化:

① 设置ADCSR的最低三位,确定分频因子;

② 设置ADIE为1,打开中断模式;

③ 设置ADEN为高电平,使ADC有效;

④ 设置ADSC,以马上开始转换。

(4)被测网络设计

经计算可得17 pF<C<19 pF,3.3 μH<L<3.4 μH,0<R<12 Ω;我们取C=18 pF,L=3.3 μH。

二、核心部件电路设计

1.正交扫频信号源电路

正交扫频信号源以两片DDS芯片AD9851为核心,在单片机的控制下使得两路正弦信号的初始相位相差90°,同时在输出端加一个无源滤波电路,减小谐波的干扰。

图E-4-2 正交扫频信号源电路

2.程控放大电路

这部分电路以AD603程控运放为核心,单片机通过ADC采集输出信号幅值之后再通过控制D/A输出改变运放的控制电压,从而达到稳定输出幅值的目的。如图E-4-3所示。

图E-4-3 程控放大器电路图

3.乘法器电路

乘法器电路部分以AD835乘法器IC为核心,配合简单的外围器件即可实现功能。如图E-4-4所示。

图E-4-4 乘法器电路

4.低通滤波器电路

如图E-4-5所示为四阶巴特沃斯有源低通滤波器,截止频率为5 kHz,阻带衰减为30 dB,性能良好。

图E-4-5 低通滤波器电路

三、系统软件设计分析

1.软件设计

本系统以ATMEGA16L为主控芯片,来控制产生信号频率以及对数据的采集、处理、转换、显示,单片机软件编程采用C 语言完成,集成环境采用AVR Studio。

单片机软件设计按照“需要完成任务分析→界面功能设计→流程设计→编写代码→调试”的顺序完成。

图E-4-6 工作流程图

根据系统的整体设计,单片机部分在系统中的任务可归结为以下几个方面:

(1)控制DDS产生扫频信号,并且能获得扫频信号的频率,以便频率定标;

(2)控制A/D采样以实现幅值的检测;

(3)处理扫频信号的频率与采集到的有效值信号,并且接收键盘输入;

(4)LCD显示控制,频率特性图形的绘制,数值的计算等;

(5)系统不同功能之间的切换和每个功能的控制。

2.系统总体工作流程

系统总体工作流程图如图E-4-6所示。

四、竞赛工作环境条件

本设计测试使用的是220V,50 Hz的市电。

软件使用平台:AVR Studio

本设计使用的仪器仪表如下:

示波器:Tektronix TDS 1002

万用表:DT9205

信号发生器:H/N8135

五、作品成效总结分析

1.测试方案

(1)测试信号源频率范围:从1 MHz频率开始以100 kHz的单位步进增加信号的频率,观察示波器,记录示波器中显示的频率,并记录此刻的Vp-p;

(2)测试正交扫频信号源的扫频性能:选取五个不同的扫频区间进行扫频并且记录一个扫频过程的时间;

(3)分别记录1 MHz和40 MHz两个频率点的电压峰峰值,重新上电五次,每次上电之后待波形平稳之后记录并计算幅度平坦度;

(4)测试“点频测量”性能:任意取十个不同的频率,测试同一个阻抗网络,分别记录测得的阻抗值,并计算误差;

(5)测试制作的被测网络:用简易频率特性检测仪测试制作的阻抗网络,记录其中心频率值和3 dB带宽,反复测量五次。

2.测试结果与分析

表E-4-1 信号源频率范围测试结果

表E-4-2 扫频性能测试结果

表E-4-3 幅度平坦度测试结果

正交扫频信号源的性能基本达到题目要求,但是在幅度平坦度这个指标上还有需要改进的地方。

六、参考资料

樊昌信,曹丽娜,等.通信原理.6版.北京:国防工业出版社,2009

康光华.电子技术基础-模拟部分.5版.北京:高等教育出版社,2009

王艳芬.通信电子电路.北京:清华大学出版社,2005

稻叶保.模拟技术应用技巧101例.北京:科学出版社,2013

远坂俊昭.测量电子电路设计(模拟篇).北京:科学出版社,2013

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。