2.4.2 Xilinx公司XC3000系列的结构

Xilinx公司的FPGA产品内部结构为逻辑单元阵列(Logic Cell Array,LCA),主要由可配置逻辑块(Configurable Logic Block,CLB)或可配置逻辑单元(Configurable Logic Cell)、各模块互连资源和输入输出模块(Input/Output Block,IOB)组成。LCA利用已编程的查找表实现模块逻辑,程序控制的多路复用器实现功能选择,程序控制的开关晶体管连接金属断片,实现模块间互连。

1)可配置逻辑块

XC3000的可编程逻辑块如图2.18所示。每个CLB由一个组合逻辑功能发生器、两个D触发器和内部控制部分组成。它包含5个逻辑输入端(A、B、C、D、E)、一个公共时钟输入(K)、一个异步直接复位输入(RD)、一个时钟使能(EC)及一个直接数据输入端(DI)。每个CLB有两个输出端(X和Y),它们可驱动互连网络。

图2.18 XC3000的CLB结构

CLB的组合逻辑部分使用32×1(或16×2)查找表(Look up Table)存储器来实现布尔函数。从5个逻辑输入和两个内部触发器输入中选择的变量作为查找表的输入。该组合逻辑单元的延时是固定的,与实现的逻辑函数的复杂程度无关,也就是说,该组合函数发生器对逻辑的复杂程度没有限制,只与输入变量的数目有关。

2)输入/输出模块IOB

输入/输出模块IOB为外部封装引脚与内部逻辑之间提供一个可编程的接口。如图2.19所示,每个IOB单元具有两个触发器、两根时钟输入线、输入门限检测缓冲器、三态控制的输出缓冲器、上拉电阻及一组程序控制存储单元。每个IOB包含寄存器输入和直接输入通路,提供一个可编程三态输出缓冲器(可由寄存器或直接输出信号驱动),配置选项允许每个IOB输出具有反相、可控转换速率和高阻上拉选择。

图2.19 XC3000系列的IOB

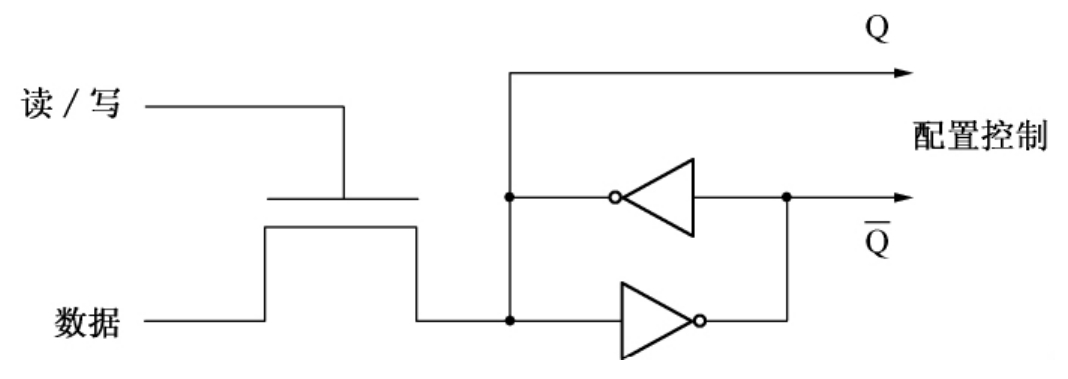

3)配置存储单元

如图2.20所示,基本的存储单元由两个CMOS反相器和一个用于读写数据的开关晶体管组成。在配置期间,只写入数据;在读回期间,只读出数据。在正常工作模式,开关晶体管处于OFF状态,不影响单元的稳定性。

图2.20 配置存储单元

4)可编程互连

可编程互连线是连接各模块的通道,将CLB、IOB连接起来形成功能电路。采用的是分段互连,布线是通过两层金属线段网和可编程开关单元(转接矩阵Switch Matrix和可编程互连点Programmable Interconnection Points)完成的。互连线有以下三种:

(1)通用互连(General Purpose Interconnect,GPI),是夹在CLB之间的5根金属连线,有横线和纵线,相交处有转接矩阵,可编程互连。

(2)直接互连(Direct Interconnect),提供相邻CLB之间或CLB与IOB之间的直接连接。CLB的X输出可连接到左边CLB的C输入和右边CLB的B输入;Y输出可连接到上一CLB 的D输入和下一CLB的A输入。当CLB与IOB相邻时,CLB与IOB之间也有直接互接。

(3)长线(Longlines),是夹在CLB之间不通过转接矩阵的连续金属连线,与IOB相邻时还有附加的长线。水平长线带有上拉电阻,每根长线输入端带有隔离缓冲器,在需要连接时自动使能。长线可由逻辑块或IOB的输出按列驱动。芯片左上角有一全局缓冲器,与一专用长线相连,可用于CLB或IOB的时钟输入,芯片右下角有一辅助缓冲器,可驱动水平长线,转接后也可驱动垂直长线,驱动所有CLB。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。