6.5 宽线性范围差分输入级

实际运放的信号处理精度最终由电路噪声决定,而在噪声起主导作用前,电路失真已成为限制精度提高的主要因素。失真包括线性失真和非线性失真两大类。线性失真不产生新的频率分量,主要是信号幅度或形状的改变,它主要由信号增益的变化引起。非线性失真产生新的频率分量,其根源在于器件的非线性工作状态。

设电路的输出具有n阶非线性响应特性,即y=∑aixi(t),则在x(t)=Acos(ωt)的基波信号输入下,包含直流、基频以及各次谐波分量的输出为

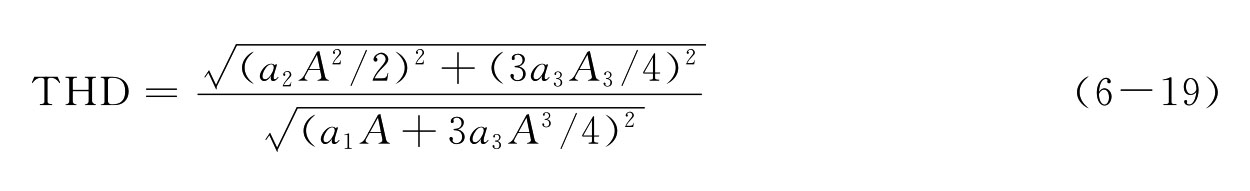

式中,直流输出对应系统的静态工作点失调,各次谐波能量相对基波信号能量的比例主要由非线性失真系数ai(i>1)决定。在全差分对称结构中,直流失调和各偶次项失真被有效抑制,电路失真主要由3次以上的奇次谐波分量决定。通常,谐波次数越高,能量越小,总的谐波失真THD(Total Harmours Distortion)定义为各次谐波失真的总和。在THD<0.1%的要求下,电路增益至少应大于60dB。如仅考虑3次以内的谐波失真,则THD近似为

基本差分对性能上的局限性主要表现在线性范围与共模范围窄(达不到轨至轨)、压摆率小、增益低。根据差分输入级对称结构抑制偶次谐波失真的特性,电路中仅残留奇次谐波分量,偶次谐波分量被有效抑制。与最大线性失真度NL相关的线性范围,可通过以下误差的相对变化率求解得到,即

差分对中的任一单管流过的最大电流为ISS,则Δmax为差分对中单个放大管在最大驱动电流下的最大过驱动电压,而与此管相对应的放大管截止,其过驱动电压为零,因此Δmax实际代表了差分输入Vid的最大动态范围。上式表明,在特定非线性误差NL的限定条件下,动态范围Δmax增加,线性范围自然相应增加。同时,放宽非线性误差NL的容限,线性范围也自然提高。以NL=1%非线性失真为例,输入信号的线性范围大致占整个动态范围的20%。

线性范围的扩展存在以下几种基本方式:①由Vid,max=ΔVo/AVd<VCC/AVd的关系,最大输入动态范围与开环电压增益成反比,则线性范围也应与电压增益成反比。通过负反馈控制方式降低电压增益,或者通过负反馈分担部分Vid输入电压,可换取动态范围增加以及线性范围的提高。②通过提高尾电流ISS、减小差分对管W/L的方式,增加动态范围,线性范围作为其中的一部分,自然提高。③采用补偿技术消除非线性项,或利用基本电路规律将非线性I-V关系转换为线性关系。根据以上原理,可以设计出多样化的宽线性范围的差分电路结构。

6.5.1 增益降低技术

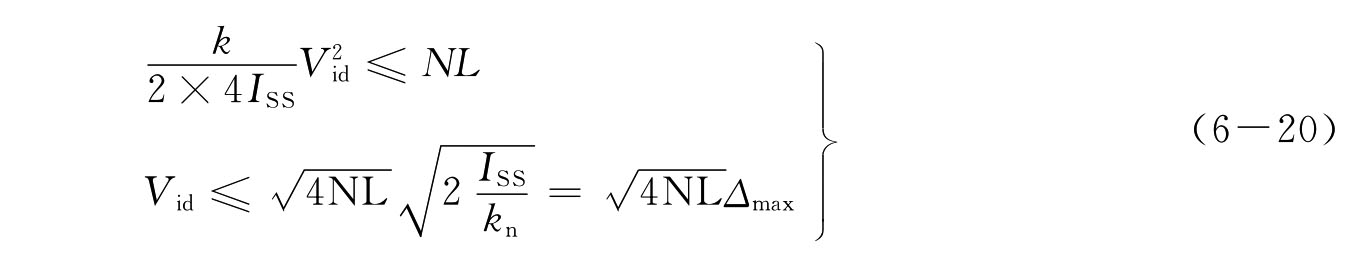

降低增益的最有效方法是采用闭环负反馈控制系统,将高增益的开环运放Av通过反馈系数为F的反馈网络构成闭环控制。理想反馈网络的闭环增益为Av/(1+FAv)≈1/F。对于α0x+α1x2的非线性响应系统,反馈将使二次谐波失真为

因有限开环增益而引入的闭环控制误差信号为

闭环系统的非线性失真及误差小于最大的环路增益精度误差。除了采用全局的闭环负反馈外,采用局部负反馈以降低开环运放的增益,同样可以达到提高线性度、抑制非线性失真的目的。采用MOS二极管负载,电路增益Av=-gm/gmL降低到可控范围,其值仅由放大管负载恒流管的W/L之比决定。此外,增加尾电流管的RS电阻也能实现增益降低,当gmRS》1时,Gm≈1/RS,增益Av=-RL/RS,显然增加RS可显著降低等效跨导和输出增益,若RS与RL均采用恒流负载,则由电阻比决定的增益同样可降低到可控范围内。

降低开环增益成为改善线性范围最直接有效的方法。图6-20(a)所示的差分电路,通过在差分对管的源极引入差模信号负反馈电阻R,实现差模增益的降低。该结构中的反馈电阻在实现线性范围增加的同时,同样对共模信号产生作用,导致输出信号的动态范围降低。进一步的改进措施如图6-20(b)所示,将原来独立的尾电流管分裂为两个并联的尾电流源,并分别接在差模反馈电阻R的两端。显然,在共模输入下,电阻R两端的电位相同,没有共模电流流过电阻R,即R电阻仅流过差模信号,保持对差模信号的反馈作用。由于电阻R不受共模信号的影响,避免了输出电压动态范围的损失。同时,由于电阻R中存在差模电流,则电阻R的中点位置不随差分信号而改变,等效为交流(差模)接地,即R的差模负反馈控制依然成立,而总的尾电流保持不变。

图6-20 局部源电阻差模负反馈电路

采用源电阻R的串联差模负反馈、共模短路的控制方法,仅是众多采用负反馈控制方式中的一种类型。针对差分对结构和尾电流控制的改进,将逐步演化出众多的高线性低失真的差分输入结构。

6.5.2 辅助源耦对负反馈结构

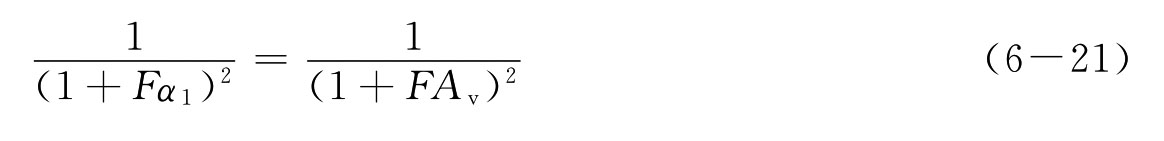

采用附加或辅助的源耦合对分担一部分差分电压,可使总差分信号Vid的范围扩大。图6-21(a)给出了一种非对称的Vid分担结构,M1/M2为W/L相同的主差分对,增益因子为k1,承担Vid中的V1分量,流过的差分电流分别为I+i和I-i;M3/M4为辅助差分对,其W/L与M1/M2一致,对应的增益因子为k2,承担Vid中的V2,流过的差分电流分别为n(I+i)和n(I-i)。

图6-21 采用辅助源耦对负反馈实现的一种Vid分担结构

根据电路结构和静态偏置条件,有

类似地

![]()

由Vid=V1+V2,计算得到V1占总差分输入Vid的比重为

![]()

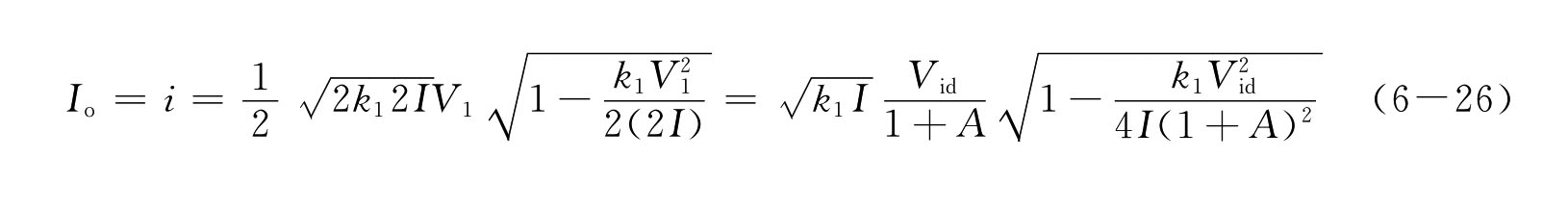

通过提高M5/M6负载静态电流比例因子n以及k1/k2比例因子的方式,扩展常数A,有利于扩展等效输入差分信号Vid的动态范围,实现线性范围的提高。该结构由于为单端输出,输出电流的变化量减半,即Io=i,由以上3式解出

当A=0,即取消辅助源耦对后,可还原为普通差分对,式(6-26)还原为与基本差分对类似的交流小信号输出电流,但电流值减半。

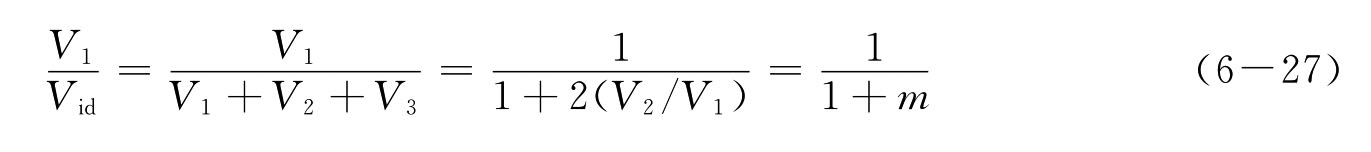

为充分利用差分输入信号,获得最大的差分输出电流,图6-21(b)给出了采用M3~M6两对相同PMOS辅助源耦对的Vid电压分担方式,M1~M2构成NMOS主差分对,其增益因子为k1,差分电压Vid。辅助单元的静态偏置电流均与主差分对相同,在相同的W/L下,各单元增益因子相同k2=k3=k1,承担的差分电压也相同V2=V3=V1。则有

式中m为电路中对称辅助源耦合对的个数,有效差分电压为总差分电压的1/(1+m),非线性失真减小到原有的1/(1+m)2。

6.5.3 自适应补偿

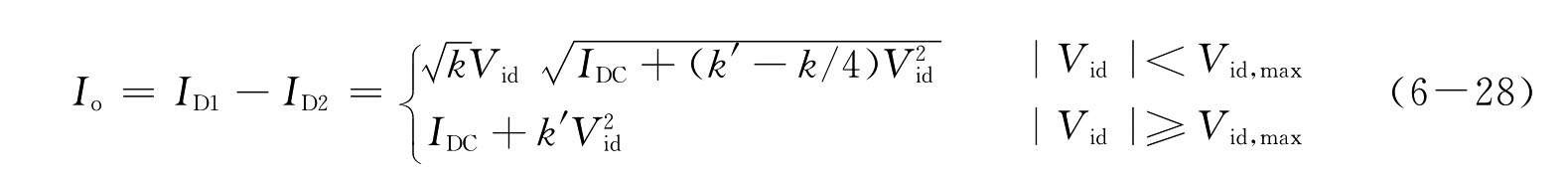

在基本差分对中,尾电流ISS固定,并与Vid多半呈现非线性关系。将基本差分对结构中的差分电流重写为Io=Vid[k(ISS-kVid2/4)]1/2。在自适应补偿策略中,尾电流ISS不再是常数,而是随Vid变化。若ISS=IDC+k′Vid2,将此ISS关系代入上式中,并根据Vid的变化范围,应有

式中,Vid,max为差分对输入差模电压的最大值,超出此范围后,一个MOS管将截止。而在输入信号的动态范围内,若取k′=k/4,则在理想匹配的条件下,动态范围内输出电流的非线性将被完全抑制,输出差分电流与输入差分电压呈线性关系,即Io=(kIDC)1/2 Vid。

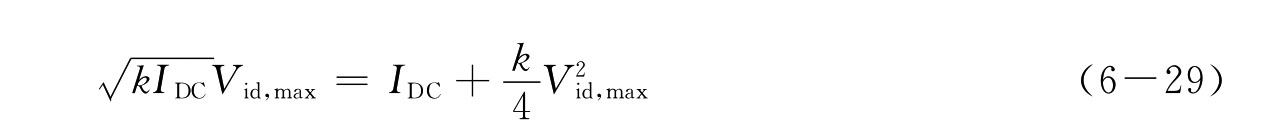

显然,线性范围内的最大电流对应于Vid,max条件,即ID1=0或ID2=0,而非截止MOS管中流过全部的尾电流,则

由此解出Vid,max=(4IDC/k)1/2。根据以上原理,图6-22给出了一种六管自适应的尾电流动态补偿结构,所有MOS管均相互匹配,VSH为固定的电平移位。经过VSH的电平移位后,维持M5/M6管在输入信号的动态范围内始终保持饱和恒流并最终可进入截止状态。因此,尾电流并不固定,而是与Vid密切相关,满足基本约束条件。

图6-22 六管自适应补偿结构

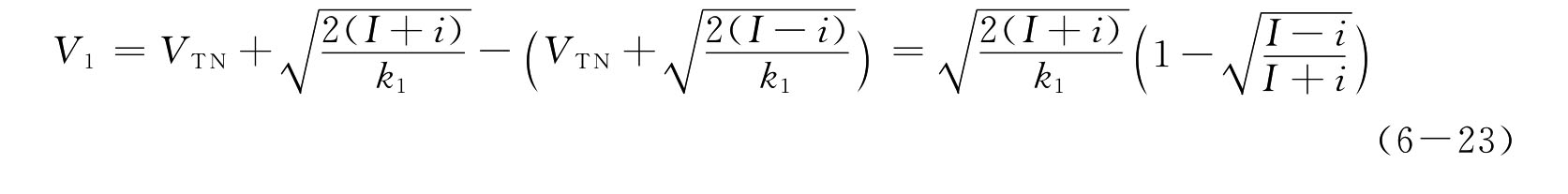

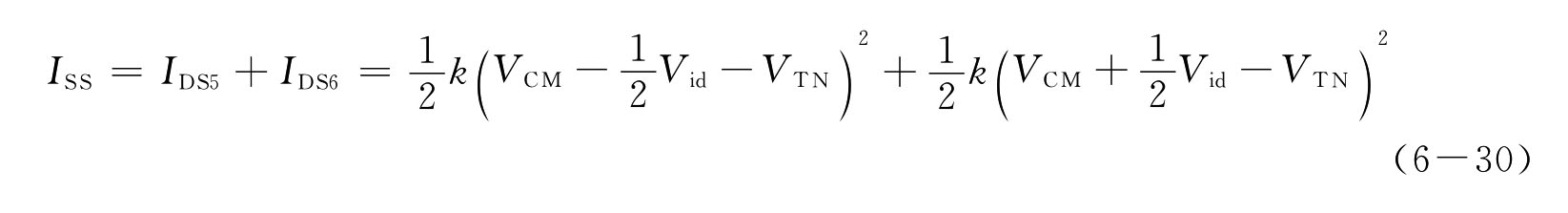

图6-22中,在各MOS管W/L匹配且单支路内电流连续的条件下,同时忽略衬底偏置效应的影响,应有VGS1=VGS3,VGS2=VGS4。经过以上VGS的变量代换,得到Vid=VGS3-VGS4=VS4-VS3。经过电平移位,有VG5=VS3-VSH,VG6=VS4-VSH。代入Vid关系后,得到Vid=VG6-VG5=VGS6-VGS5。设M5、M6两管的共模信号为VCM,则VGS6=VCM+0.5Vid,VGS5=VCM-0.5Vid,由此得到符合动态补偿要求的ISS为

化简后得

![]()

图6-23 尾电流交叉耦合调制法

在静态平衡条件下,M5、M6两管电流相同并分别与各差分支路中的电流相等,则VGS6=VGS3,式中共模信号电平VCM=(VGS6+VGS5)/2=(VGS3+VGS5)/2=(VB-VSH)/2。为保证静态尾电流IDC,至少应满足VB-VSH>2VTN的基本要求,从图中也可直观看出该限制条件的物理意义,即VB-VSH电压至少应使M3/M5或M4/M6两个MOS管饱和导通。这种六管结构的动态尾电流控制技术满足k′=k/4的电流输出要求,线性范围扩展到与动态范围相同的区域。

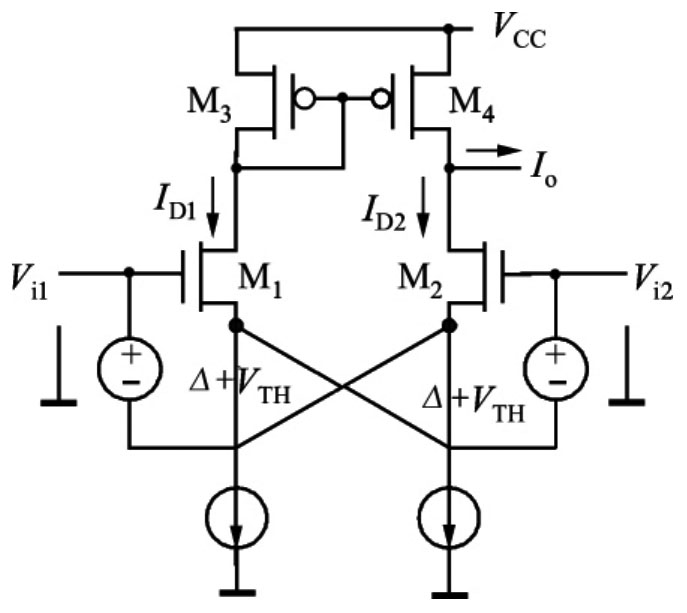

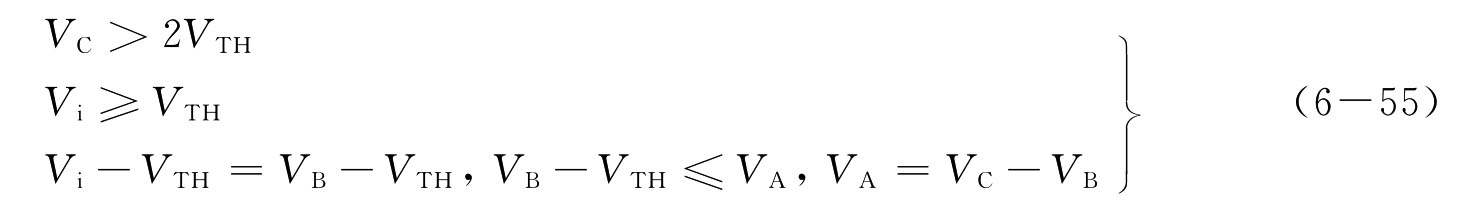

图6-23给出了抑制非线性失真的另一种电路实现方式,即采用交叉耦合对管(Cross pair)消除存在的非线性项。与普通差分对独立尾电流偏置不同的是,将尾电流偏置分裂成相同电流的两路结构,同时将一个VTH+Δ的直流电平移位电压插入到一端输入与另一端源极之间,即

![]()

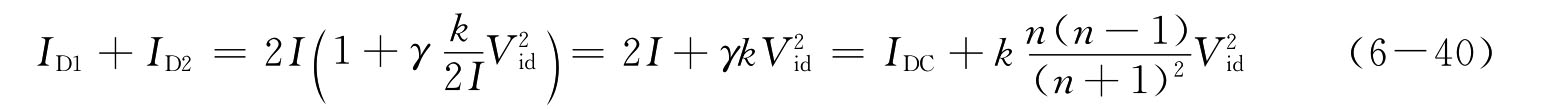

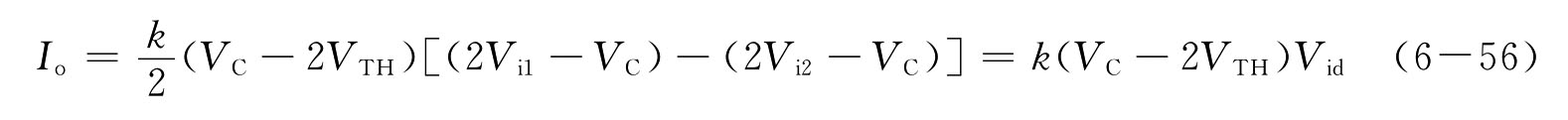

设Vid=Vi1-Vi2,则差分对管中的电流分别为

当以上两式中移位电平的过驱动电压Δ为相同的常数时,则差分输出电流为Io=ID1-ID2=(2kΔ)Vid。因此,普通差分对输出电流中的非线性Vid项被完全抵消,同样得到与动态范围一致的线性范围。该原理电路结构实现的关键在于直流电压移位电平为固定常数,并不受Vid影响。实际电路中,由于受Vid影响,移位支路中的Δ并不严格相同,电路参数设计应将这种失配的影响降到最低。

根据以上非线性补偿原理及电路设计要求,图6-24(a)给出了基于交叉耦合差分对电平移位结构的具体实现方式,即W/L相互匹配的M3和M4管,分别与M2和M1组成源极耦合的差分对,图中K=W/L。为降低M3、M4管过驱动电压Δ受差分Vid的调制作用,应提高其静态电流偏置并降低电流的变化。

图6-24 基于差分对交叉耦合的非线性抵消结构

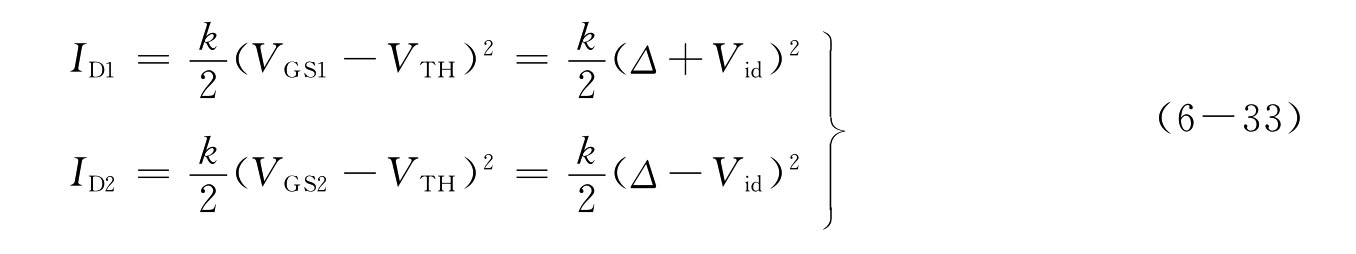

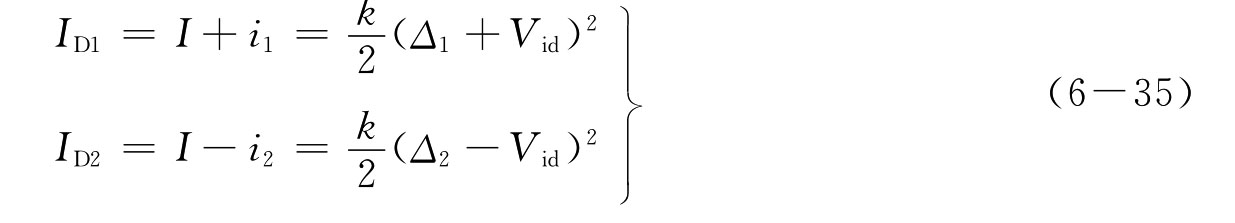

设M4的W/L比M1大n倍,则静态时的尾电流为nI,其差分电流的变化量为i1;同样,M2与M3组成的非匹配差分对,静态偏置与M1/M4完全相同,其差分电流的变化量为i2。因此,电平移位管M3和M4中流过的电流分别为nI+i2和nI-i1。由于差分小信号电流i1和i2的影响,使流过两管的电流并不是固定常数,无法严格实现所要求的相同Δ电压,为此需要尽可能提高因子n的数值。考虑差分输出电流的作用后,原来相同的Δ变成两个不同的值Δ1和Δ2,则式(6-33)修正为VGS1-VTH=Δ1+Vid,VGS2-VTH=Δ2-Vid。设k为差分对管M1/M2的增益因子,则由M4和M3电流决定的过驱动电压分别为

由于电平移位电压受输入电压的调制,则M1和M2中的实际电流为

由以上方程求解后得出

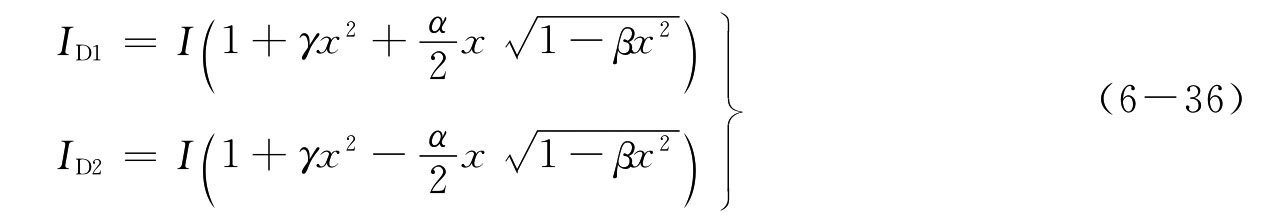

式中,参量x为Vid相对单管静态条件下过驱动电压的比值,α、β、γ为与n有关的参变量:

![]()

输出差分电流为

![]()

为保证输出电流为实数解,Vid应满足的条件为

![]()

当n=1、α=2、β=1/4时,则完全退化为为普通差分对特性,对非线性抑制没有改进作用。只有增大n使β近似以1/n减小,才能有效抑制差分对中的非线性因子。很明显,线性性能的改善是以牺牲面积和功耗性能为代价。

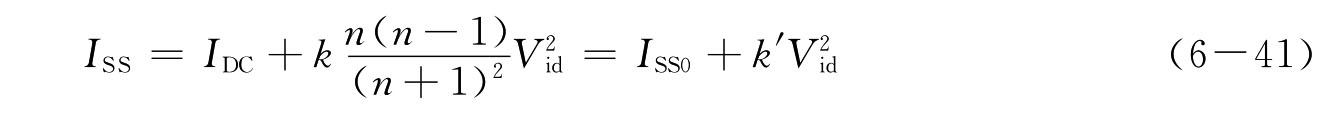

进一步分析发现,若通过某种方式取输出电流ID1与ID2的和而非差值,则又返回到原始自适应补偿的非线性控制结构设计,即

若取ISS=ID1+ID2作为自适应差分对的尾电流,则ISS可以满足动态补偿基本要求,即

根据动态补偿所需的k=4k′约束条件,即4n(n-1)=(n+1)2,解得 ≈2.16。

≈2.16。

图6-24(b)给出了根据动态尾电流控制原理而设计的输入差分对结构,其中M1~M4组成交叉耦合的差分对,形成如式(6-41)所示的动态尾电流,为将此电流传输到M6/M7差分对的尾电流中,引入M5管及两个附加的电流源aI,因此有aI=IDS5+IDS1+IDS2=IDS5+IDS6+IDS7,即IDS6+IDS7=IDS1+IDS2=ISS,该式表明输入差分对M6/M7中的尾电流之和ISS由M1/M2交叉耦合对电流和决定,从而通过电流移位作用实现差分对尾电流的动态补偿。为保证M5管在Vid动态范围内均处于饱和导通状态,应有aI>ISS,max=2I+k′Vid,max2,即

代入n=2.16的条件,解得a=3.16>β。在以上自适应补偿设计中,采用Vid调制ISS电流动态偏置以消除非线性,与此相对应的,保持尾电流不变,可采用交叉耦合对改变复合差分对ID电流的等效调制方法。即通过两个并联的同型差分对将各自的非线性项相互抵消,达到扩展线性范围的目的。

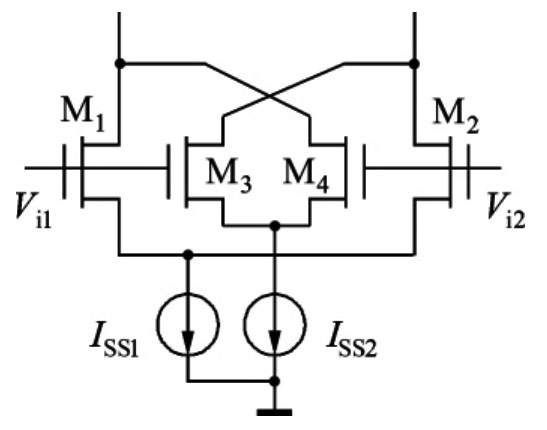

图6-25 漏交叉耦合差分对

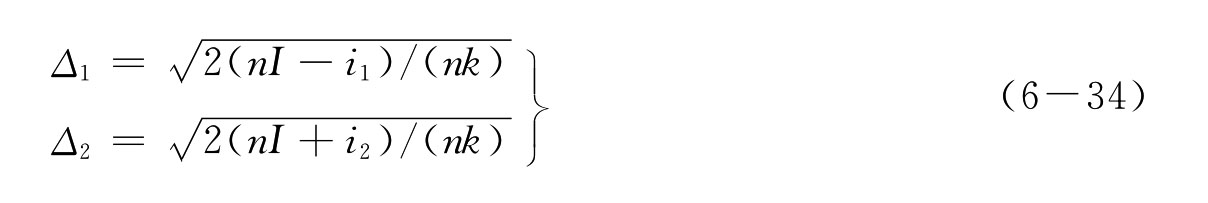

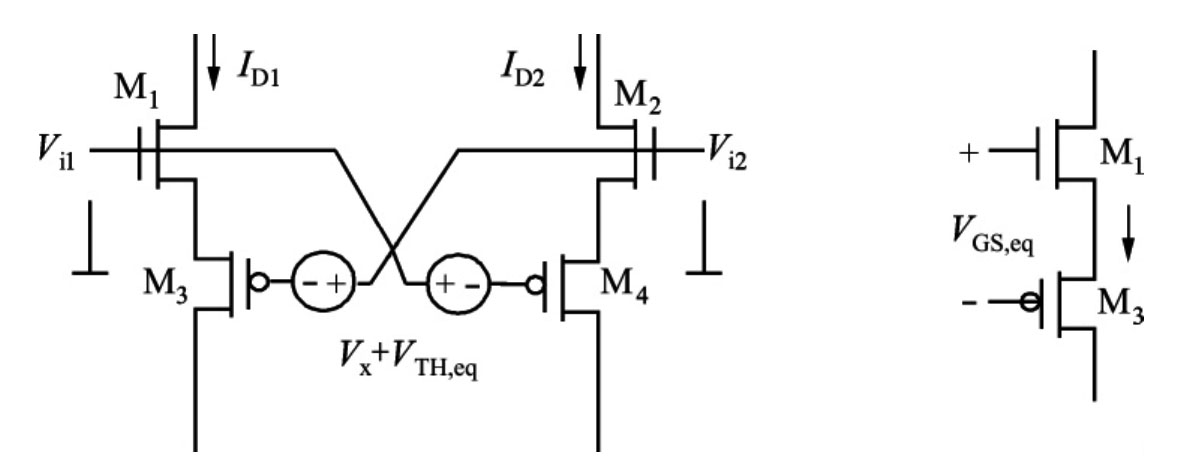

电路如图6-25所示,四管漏交叉耦合差分对中,M1和M2的增益因子为k1,接尾电流源ISS1,M3和M4的增益因子为k2,接尾电流源ISS2。由两差分对M1/M2、M3/M4电流传输特性并在小信号Vid的条件下得到

输出差分电流为Io=ID1+ID4-(ID2+ID3)=(ID1-ID2)-(ID3-ID4),即

![]()

对称结构可自然抵消偶数项谐波失真,当满足(ISS1/ISS2)=(k1/k2)3的约束条件时,奇数次谐波项被抑制,即3次以上的谐波失真迅速衰减并可忽略,因此输出保留线性项。为了保留线性项,两差分对并不能完全相同,即ISS1≠ISS2、k1≠k2,此结构中两个晶体管,引入了更多的输入噪声。

6.5.4 Class AB补偿

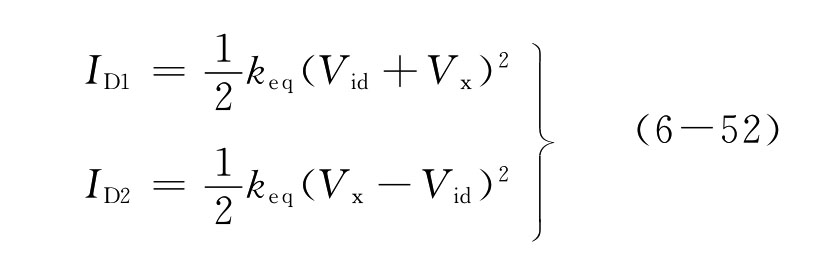

在自适应动态偏置的补偿结构下,跨导输出的最大电流可大于静态偏置电流。Class AB也具有类似的特性,因此同样可用于非线性补偿的设计。Class AB在消除差分对非线性的同时,还具有高频特性好、抗噪声能力强的显著特点,但共模范围损失成为Class AB需要解决的一个问题。在饱和状态下,差分对中两支路电流形成的差分输出为

![]()

如果VGS1+VGS2为常数,由于Vid=VGS1-VGS2,在此条件下差分输出电流与输入Vid呈现所需的线性关系。然而,对于普通的差分对,总的VGS由于电流的变化而无法满足恒定常数的要求,这也是普通差分对产生非线性的根源。只有在Vid很小的条件下,差分对中的电流才近似相同,VGS之和近似为常数并表现出良好的线性特性。

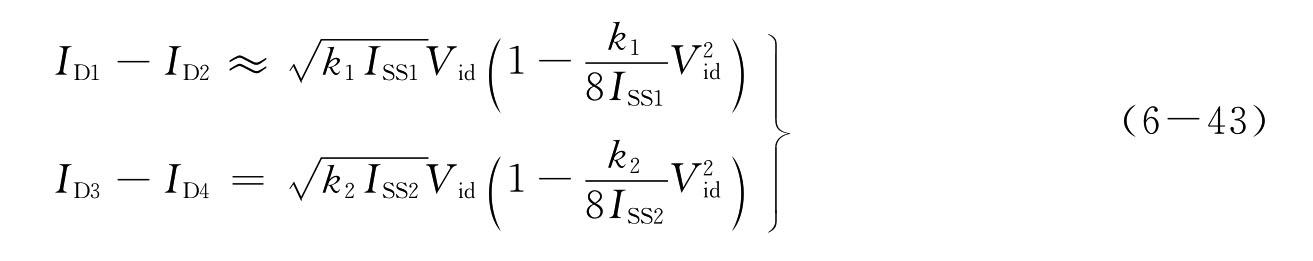

Class AB差分对的实质,就是通过对普通差分结构的改造,实现差分对VGS电压之和为常数的要求,同时保持VGS电压之差Vid的差分性质。由此构造出如图6-26所示的Class AB差分对输入,将M1/M3、M2/M4分别看成两个独立的组合MOS管,并且尾电流分裂为两条相同的支路电流,即由原来M1/M2的NMOS差分对,扩展为M1/M3、M2/M4的CMOS差分对。

图6-26 Class AB差分对原型结构

Class AB差分输入级的具体实现中,在交叉耦合的NMOS与PMOS差分管的栅极之间引入一辅助电压源VM=Vx+VTH,eq,当VM电压源中流过固定的偏置电流I时,即可实现VM与Vid是独立无关的常数。因此,利用VM固定电压偏置复合差分对管,使复合管等效VGS电压之和保持与Vid无关,即可达到扩展线性范围的目的。一对CMOS组合管的总栅压为

![]()

将总的栅源电压表示成复合型单管等效的VGS,eq,则有

![]()

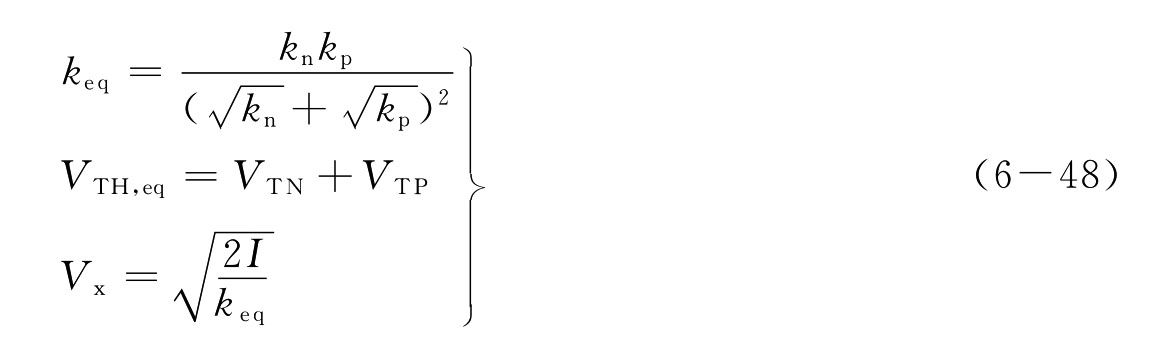

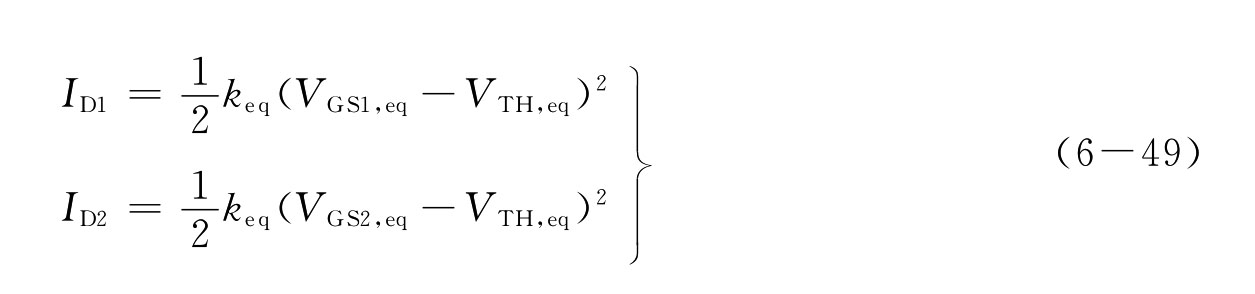

式中,等效的增益因子、开启电压和过驱动电压分别为

根据图6-26中VM电压源的偏置结构,设CMOS差分对与VM辅助电压源中CMOS组合管的等效增益因子keq和等效开启电压VTH,eq分别相同,即有Vi1-(VGS1+VGS3)+VM=Vi2,同时相对应,有Vi2-(VGS2+VGS4)+VM=Vi1,则差分输入Vid=Vi1-Vi2=VGS1,eq-VM=VM-VGS2,eq。根据基本差分对原理,两独立CMOS差分对管的输出饱和电流分别为

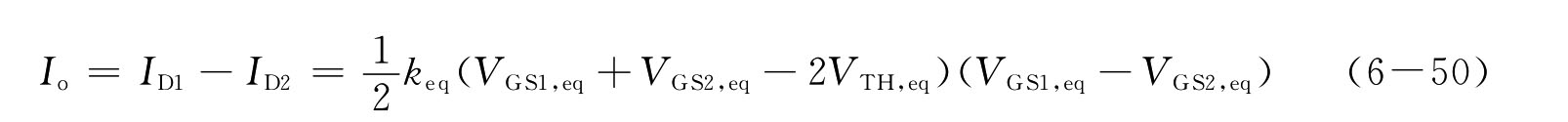

差分输出电流为

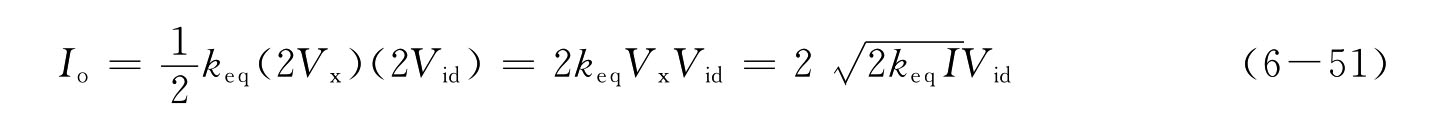

由VGS1,eq+VGS2,eq=2VM=2(Vx+VTH,eq),知VGS1,eq-VGS2,eq=(Vid+VM)-(VMVid)=2Vid。通过CMOS差分结构和VM电平的移位作用,Class AB实现了在整个Vid动态范围之内的线性输出,即

图6-27给出了Class AB宽线性范围差分输入的原理图,并给出了线性范围等效于动态范围的控制原理。Class AB的动态范围对应于ID1或ID2为零时的Vid范围,根据VGS1,eq=Vid+VM,VGS2,eq=VM-Vid,VM=Vx+VTH,eq的基本约束关系,输出电流与差分输入电压的关系为

图6-27 Class AB差分对结构示意图

图6-28 多管组合线性单元结构

由ID1=0及ID2=0的条件,得到的Vid范围为-Vx≤Vid≤Vx,代入Vx=(2I/keq)1/2的条件,对应的输出差分电流的动态和线性范围为-4I≤Io≤4I。

显然,Class AB差分放大电路中VM电平移位电路设置的偏置电流I越大,实现的动态范围与线性范围也越大。同时,Class AB差分对的跨导和电流驱动能力也随偏置电流I的增加而提高。

6.5.5 线性化单元技术

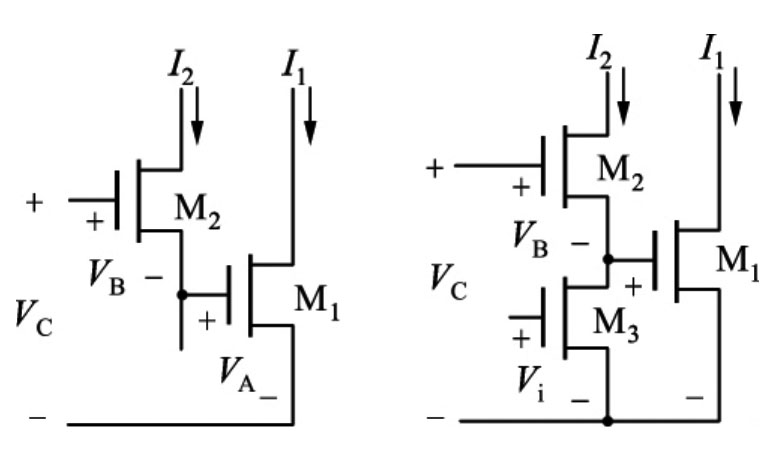

与Class AB的控制特性相类似,通过采用多管组合的线性化技术,也可提高差分输入电路的线性范围。图6-28给出了三管线性组合单元的原型结构。

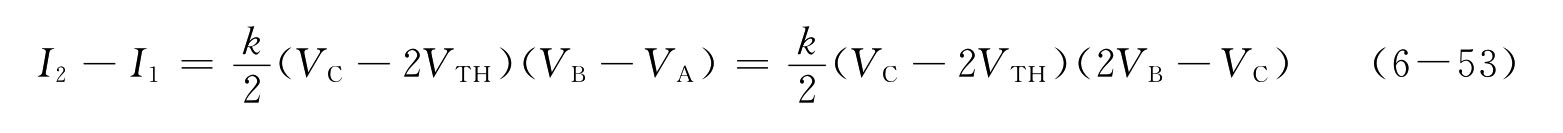

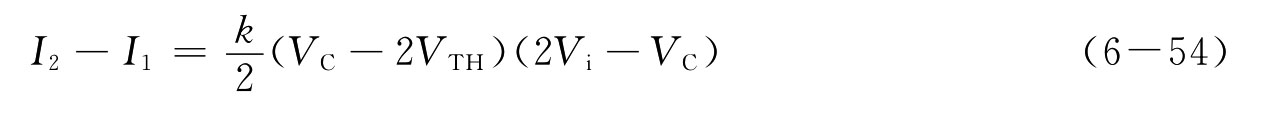

设3个MOS管的增益因子k完全相同,VA和VB分别为M1与M2管的VGS电压,其中VC=VA+VB,则VB-VA=2VB-VC=VC-2VA。根据最简单的两管组合线性结构,获得输出差分电流为

显然,若VC为固定偏压常数,且VB=Vi时,差分电流即与输入电压Vi呈线性关系。由于M2管没有直流通路而无法正常工作,因此为实现两管组合单元的控制作用,应增加M3管并与M2管串联,形成I2电流的直流通路。M3与M2管的参数设计完全相同,在忽略衬底偏置效应的前提下,处于饱和工作区的M2与M3管的VGS相同。当输入信号加到M3管的栅极时,Vi=VGS3=VGS2=VB,由此实现了差模电流与单端输入电压Vi的线性关系,即

M3管饱和工作区限定的输入电压Vi与偏置电压VC应满足的约束条件为

即2VB<VC+VTH,VA使M1导通,则VA,min=VTN,VA使M2导通,则VA,max=VC-VTN,VA的变化范围则为VTN~VC-VTN。与此相对应的,VB使M1/M2导通的动态范围为VC-VTN~VTN,进一步M3工作于饱和区下对VB即Vi的动态范围改变为VTH~(VC+VTH)/2。因此,3管组合线性单元在构成线性放大电路时存在两个严重的限制,首先是输入信号的共模范围受到限制,共模抑制比低,其次是输出电流中存在固有的直流失调项。因此,将以上线形组合单元结构扩展到差分结构中,有效克服了以上两类缺陷,具体电路实现结构如图6-29(a)所示。

图6-29 基于组合线性结构的差分输入对

对于图6-29(a)所示的6管组合线性差分结构,输出为两组线性组合单元差模电流的差分电流,用以消除支流直流偏移失调及扩展输入信号的共模范围Io=Ia-Ib、Ia=I4+I2、Ib=I1+I5,整理后得Io=(I2-I1)-(I5-I4)。代入单组线性组合单元的差模电流公式,得到:

由于差分对仍然采用单一的源极耦合尾电流源,因此差分对Vid的动态范围与普通差分对动态范围的关系式完全相同,即Vid,max=(4I/k)1/2。该电路并没有完全解决输入共模信号范围向上扩展的问题,当Vic增加时,源电位VS相应提高,但VS的上限范围受到限制,即VS<VC-VTN,且VS过高后还使M1/M4进入线性区。

在图6-29(b)的改进结构中,为了避免VS电位变化对M1和M4电流的影响,分别增加了M7和M8串联的隔离PMOS管,其W/L远大于NMOS的W/L,即交流阻抗远低于NMOS交流阻抗而近似为零,所以仍然保持以上分析的交流输出电流关系。然而,由于VC2和VTP的作用,M1/M4管的源电位直流电平上升了VC2+VTP值,导致VC1也会有同等幅度的增加。M2/M5实际构成了一种套筒式Cascode差分增益结构,进一步的分析表明,当其偏置VC提高时,差分输出的电压摆幅明显下降。因此,对于N型输入的此类型差分结构,比较适合处理具有较低共模电平的差模信号。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。