6.4 全差分输入级

差分输入、差分输出的全差分电路具有抗噪声能力强、共模抑制比高的突出优点。下面首先分析低增益和高增益的两种全差分增益结构,并对高增益全差分对中的共模负反馈CMFB电路设计进行分析。

6.4.1 全差分结构

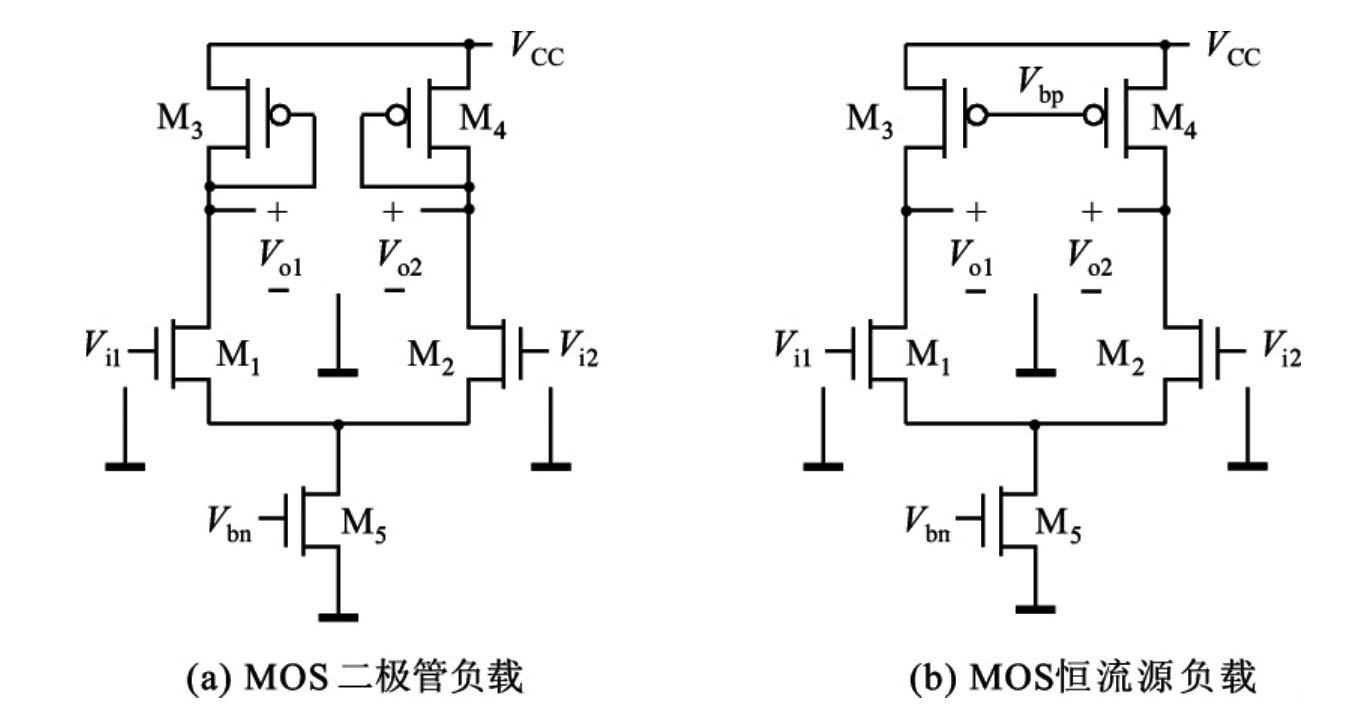

基本的全差分输入结构如图6-11所示,由于采用全差分输出,理想条件下电路的静态工作点完全匹配,系统失调可忽略。若工艺造成的随机失调能够控制在很小的范围内,则全差分结构总的输入失调很低,可以获得很高的共模抑制比和电源抑制比特性。在全差分级连信号的处理中,有利于消除信号中以共模分量表现出的噪声信号,适合高精度的信号处理。

根据输出阻抗的差异,全差分输入级分为低阻低增益和高阻高增益两种结构类型。图6-11(a)的全差分结构采用MOS二极管低阻负载,虽然差分增益较低,但增益的可控性强,输出信号的共模电平可由MOS二极管的钳位而稳定设置和控制,无需高增益全差分结构所必备的CMFB共模反馈电路。

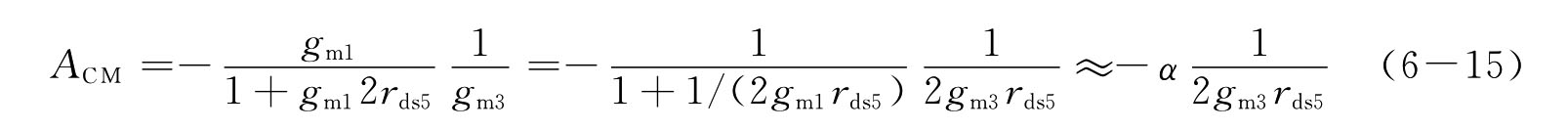

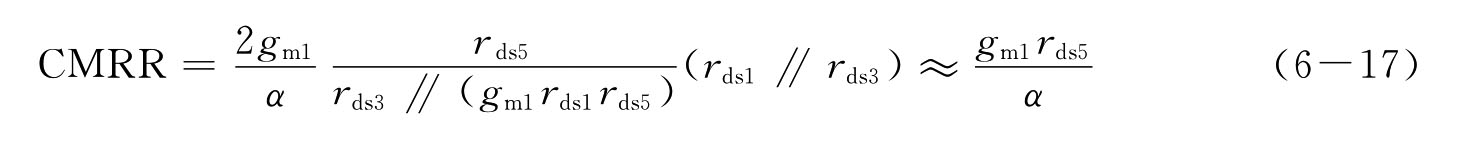

该类型全差分电路的差模信号增益为Adm=-gm1/gm3,若考虑共模信号的单端输出,则共模信号增益ACM即为单端输出的共模增益,即

式中α≤1,则系统工作点失配决定的共模抑制比CMRR=2gm3rds5/α≈gm3(2RS),即为负载跨导与两倍尾电流电阻决定的增益关系。

图6-11 差分输入—差分输出的全差分结构

在图6-11(b)所示的恒流负载全差分结构中,差模与共模增益近似按相同的速率增加因此,无论负载如何,低输出阻抗与高输出阻抗的全差分结构具有近似相同的CMRR。考虑到高阻输出的全差分结构中共模输出阻抗提高的幅度更大,则其CMRR相对低阻输出的全差分结构略有减小,即

对于高阻全差分输出电路,需要CMFB控制电路以确定输出支路的共模静态点,电路结构相对复杂;低阻全差分输入电路虽然结构简单,CMRR相对较高,但差模增益过小,应用受到局限。而采用恒流源与MOS二极管并联的负载差分结构,可兼顾以上两种负载各自的优点,同时克服两种电路结构各自的不足。

对于图6-12所示的兼容结构,当从不同角度考查时得到不同的结论。如删除起钳位作用的M4/M5管,则增益增加,因此消极的观点认为MOS二极管的引入将导致增益的下降;另一方面,以MOS二极管为基本负载,如没有M6/M7管的分流,则MOS二极管过大的静态电流导致增益下降,因此积极的观点认为M6/M7恒流源的引入可使电路增益提高。显然,形成这两种观点的原因在于参照对象的不同。由于并联电阻中的低阻决定增益,因此在差分对管或尾电流相同的条件下,M6/M7的分流使MOS二极管输出阻抗增加,实际差分增益相对独立MOS二极管负载条件下的增益略有提高,同时保持了该结构输出共模电压和增益可控的优点。设计中使M6/M7的偏置电流较大而M4/M5的偏置电流较小,可以更有效地提高全差分增益。

图6-12 兼容负载的全差分结构

6.4.2 共模负反馈(CMFB)电路

单端输出的运算放大电路在闭环负反馈下,由于输入的虚短性质,则输出支路的共模信号由差分输入端的共模信号所决定,即单端输出依靠Vid的失调及输入分辨率进行控制。而全差分运放的输出各自反馈到输入则情况完全不同,首先,相互间没有可供参照的参考电平,其次,差分输出两支路的失配状态不同,因此调节每一个支路的共模点所需的Vid失调不同,即不存在相同的Vid失调能将两输出支路的共模电平设定在同一静态点。只有采用附加的共模负反馈(CMFB)电路才能实现对输出共模点的调节,因此,CMFB为高增益全差分电路必不可少的控制电路。

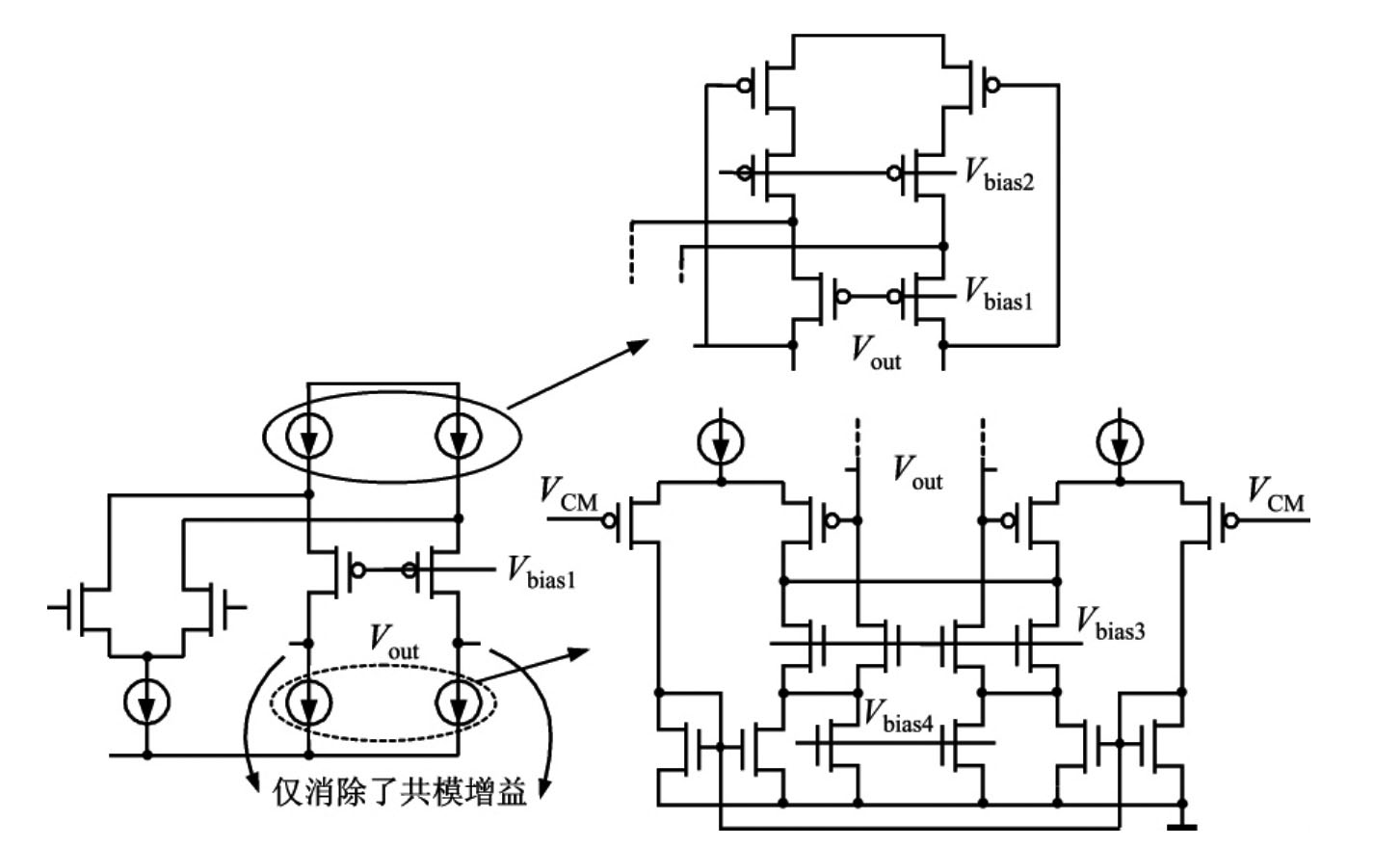

差分放大器是对差模输入信号进行感应并放大,而CMFB则是对输出共模信号进行检测,并利用其负反馈控制调节输出支路的静态电流。图6-13(a)(b)分别为全差分CMFB控制结构,在该全差分电路中,CMFB的输出可以选择调节负载恒流源或尾电流源的栅电位。此外,也可选择调节放大管的静态电流,将输出共模点调节到合适的电平位置。与差分放大相对应,CMFB本质上是一种共模信号负反馈放大器,通过对共模增益的抑制处理,实现共模点的稳定。

CMFB电路通常包括两个组成部分,首先是共模信号感应检测与放大模块,其次是控制信号的产生与控制模块。CMFB可以有多种不同的实现方式,图6-13中(c)给出了两种简单的VCM检测方式。一种是采用平衡电阻的检测,根据VCM=(Vo1+Vo2)/2的定义,采用叠加原理,电阻中点的输出电压为VM=Vo1+(Vo2-Vo1)/2或VM=Vo2+(Vo1-Vo2)/2,即VM=VCM。这种共模信号的检测电路结构简单,而且在静态平衡条件下,电阻R两端的共模信号相同,且电阻中没有电流,因此对静态偏置点没有影响。但以R作为差分对的输出阻抗,其值较低,降低了差模增益的值。因此,为抑制电阻共模电压感应带来的不利影响,需要采用大的共模检测电阻R。

图6-13 全差分CMFB控制结构

为了彻底克服电阻检测型CMFB电路的不足,可采用串联电容代替串联电阻。电容上没有静态电流,低频下的容抗很高,对运放低频下的差模增益影响小。当Vo1=Vo2=VCM时,电容C两端没有压差,则VM=VCM;在差分输入电压下,当Vo1和Vo2以相反的极性变化时,若电容的充放电速度足够快,电容C存储的电荷能够达到其与电压驱动的平衡值。则根据两电容C上存储电荷的平衡条件,有C(Vo1-VM)=C(VM-Vo2),即VM=(Vo1+Vo2)/2=VCM。

电容反馈型CMFB虽然解决了电阻反馈型CMFB存在的问题,但电容反馈型CMFB带来的新问题是反馈控制电路的速度相对较慢。直观上看,输出电容的充放电延迟,一方面对差分增益的频率和动态响应速度产生不良影响;另一方面,VCM作为一种宽范围的大信号变化,其延迟相当于差模信号显著增加,造成CMFB的响应速度降低,限制了电容反馈CMFB控制的全差分电路在高速信号处理领域内的应用。

采用开关电容CMFB可解决普通电容CMFB电路面临的各种问题,并保留低功耗的优异性能。开关电容CMFB的一种基本结构如图6-14(a)所示,利用开关电容等效的开关电阻实现CMFB控制,解决线性电阻带来的低频功耗与增益损失。开关电容型CMFB电路的另一种常用结构如图6-14(b)所示。一组共模电平用于对电容充电的参考电压,其中Vcm_ref是期望的共模电压,Vcmfb为CMFB输出的实际偏置电压,用以调节恒流源并控制输出共模点。开关用于切换电容的充放电状态,实现CMFB控制功能。两个相同电容C2串接在差分输出Von、Vop的两端,其中点的输出电位感应的是差分输出的共模信号,提供Vcmfb的反馈电压信号。在以上电容两端通过开关控制,可分别并接上电荷传输电容C1。

在开关电路依次相邻的两个工作周期内,第一个周期一组开关导通后对采样电容C1充电,第二个周期另一组互补的开关导通后将C1对电容C2放电。经过若干采样周期后,差分输出端的共模电平以及反馈输出分别被设置在所需的电平位置。CMFB电路中的电容作为运放的负载,降低了电路处理的速度,因此C1和C2电容必须尽量减小。选择C1》C2有利于降低各种误差,并使共模电压具备较快的建立时间;而选择C2》C1,可使运放在不同的开关状态下有近似相同的电容负载。为抑制高频共模噪声,CMFB的GBW应明显大于差分运放的GBW。

开关电容CMFB通常用于开关电容电路中全差分运算放大的设置。在时间连续的全差分运放电路中,一般需要时间连续的CMFB控制电路。为此,可采用基本的单级放大结构组成共模反馈电路。

图6-14 采用开关电容的CMFB电路

图6-15给出了一种基于CS增益控制的CMFB电路。差分输出X、Y直接作为M13/M14对管的输入信号。对于X、Y的差模输入,对管中的总电流不变,即A点电位不变,因此这种对管对差模信号不响应。相反,当输入为共模信号时,对管中的电流同时增加或减小,导致A点电位响应输入共模信号的变化。由于M13/M14与差分对管的性质正好相反,可视为共模对管,响应共模信号的变化。当X、Y共模输出偏高时,共模对管中的电流增加,但由于M5/M6恒源偏置作用,迫使A点电压下降,A点电压的降低又使M11/M12CG管中的电流增加,而NMOS恒流源电流的增加将使输出共模点降低。设置合适的器件参数,以上对共模信号的负反馈将使输出共模点稳定在所需的静态偏置下。

图6-16中的CMFB控制从主输出支路中独立出来,减小了它对输出电压动态范围损失的不利影响。同时,对共模信号的感应放大采用NMOS与PMOS上下互补对称的CSCG共模对结构,提高共模增益。当输出点X、Y输出的共模信号偏低时,互补共模对的输出A点偏高,导致主差分对静态偏置电流降低,输出共模点升高,平衡下达到稳定的静态工作点。由于这种方式改变了差分对管等效静态电流,使电路差分放大的性能发生改变,在具体应用中应十分慎重。

图6-15 CS控制的CMFB电路

图6-16 互补CS-CG控制的CMFB电路

图6-17给出了两种CMFB电路。一种是将电路输出信号直接加在PMOS负载管的栅极对电路输出共模电平进行控制;另一种是用一组差分对实现CMFB电路。图中,CMFB电路中PMOS差分对的一端接所需控制的共模信号VCM,当差分对感应的实际输出共模电平高于VCM时,尾电流全部流入NMOS二极管负载管,再经过NMOS CS的放大,使反馈的控制电位降低,将差分输出的共模电压下拉,并稳定在VCM。而当输出为差模信号时,两感应PMOS管中的电流之和保持不变,共源端交流接地,并使CMFB输出支路电流相同;同样,NMOS二极管负载中的电流之和保持为常数,等效为交流接地,维持CMFB输出支路电流平衡的状态。最终,CMFB的输出不响应差模信号,实现共模信号的反馈控制。

图6-17 采用差分对结构的CMFB电路

6.4.3 高增益全差分运放电路

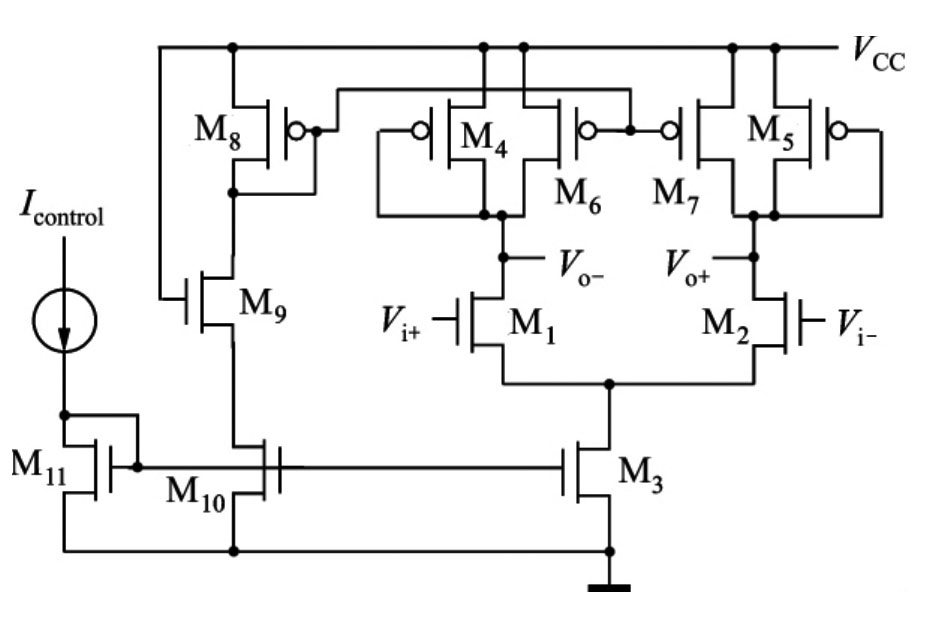

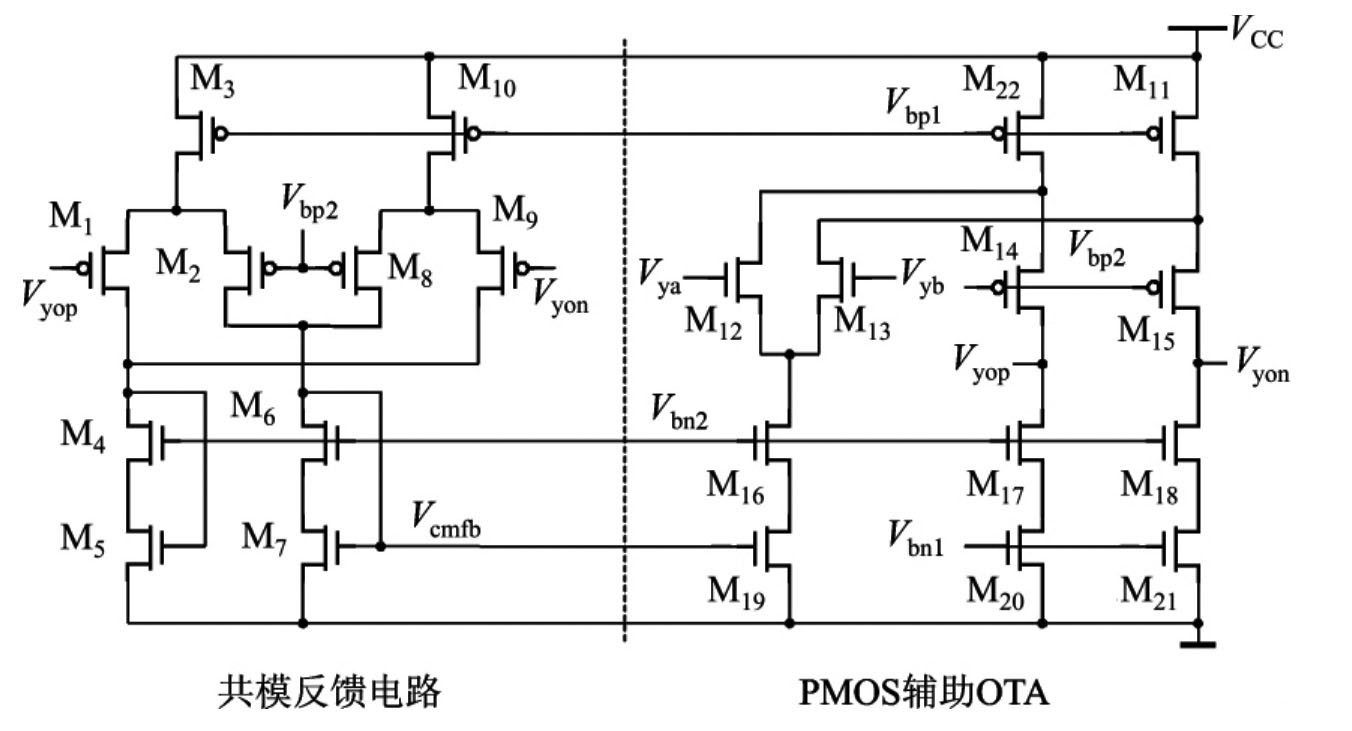

完整的高增益全差分运放电路包括主增益运放结构及CMFB共模负反馈电路。图6-18和图6-19分别给出了一种N型和P型差分输入的折叠式Cascode全差分运放电路,CMFB电路同时提供主运放尾电流及Cascode恒流源偏置。

图6-18 N型折叠式Cascode全差分电路

以图6-19所示的电路为例,M1/M9的输入分别感应输出信号,其漏电极短路以感应共模电流而抑制差模电流,即差模输出不改变以上对管的电流之和,而共模信号则改变两管的电流之和。由于Vbn1恒流偏置的作用,M3/M10两管中近似流过相同的电流。因此,对于输出差模信号,M2/M8对管中的电流和固定不变,从而确保M7/M6中稳定的电流并提供主差分对的尾电流偏置。

图6-19 P型折叠式Cascode全差分电路

对于共模信号,当输出共模电平偏高时,M1/M9中的电流总和增加,则必然导致M2/M8中的电流总和减小。这实质上是一个负反馈作用,减小的电流使PMOS差分对的尾电流减小,进而使NMOS CG管的电流增加,而PMOS Cascode恒流特性稳定不变,从而将输出共模点向电平减小的方向推移,最终达到稳定的共模静态点。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。