4.3 属性描述与定义语句

VHDL中预定义属性描述语句有许多实际的应用,可用于对信号或其他项目的多种属性检测或统计。VHDL中可以具有属性的项目有:类型、子类型;过程、函数;信号、变量、常量;实体、结构体、配置、程序包;元件;语句标号等。

属性的值与对象(信号、变量和常量)的值完全不同,在任一给定的时刻,一个对象只能具有一个值,但却可以具有多个属性。VHDL还允许设计者自己定义属性(即用户定义的属性)。

预定义属性描述语句实际上是一个内部预定义函数,其中综合器支持的属性有:LEFT、RIGHT、HIGH、LOW、RANGE、RVERS_RANGE、LENGTH、EVENT和STABLE等。

其语句格式是:

属性测试项目名'属性标识符

属性测试项目即属性对象,可由相应的标识符表示,以下仅就可综合的属性项目使用方法作一说明。

1)信号类属性

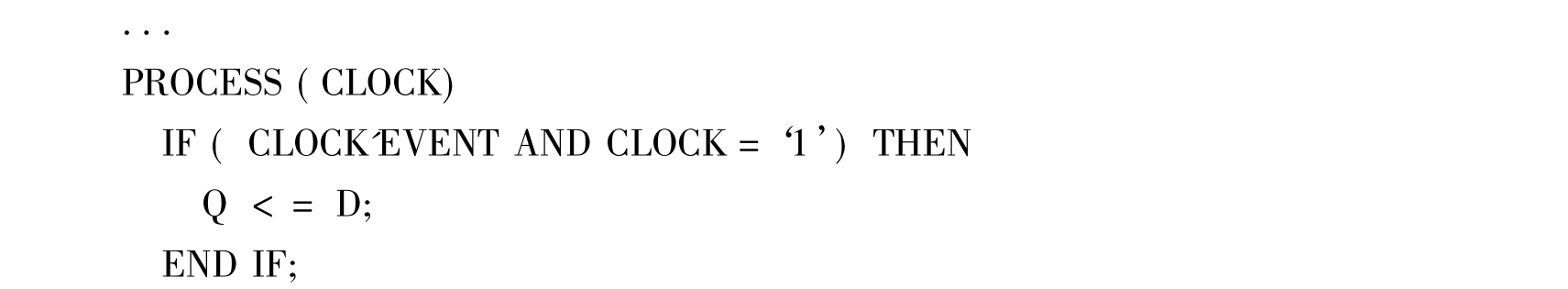

(1)EVENT

信号类属性中,最常用的当属EVENT。VHDL通过以下表达式来测定某信号的跳变边沿:

![]()

例如,语句“CLOCK'EVENT”就是对以CLOCK为标识符的信号,在当前的一个极小的时间段δ内发生事件的情况进行检测。所谓发生事件,就是电平发生变化,从一种电平方式转变到另一种电平方式。如果CLOCK的数据类型定义为BIT,则在此时间段内,CLOCK由0变成1或由1变成0都认为发生了事件,于是这句测试事件发生与否的表达式将向测试语句,如IF语句,返回一个BOOLEAN值TRUE,否则为FALSE。

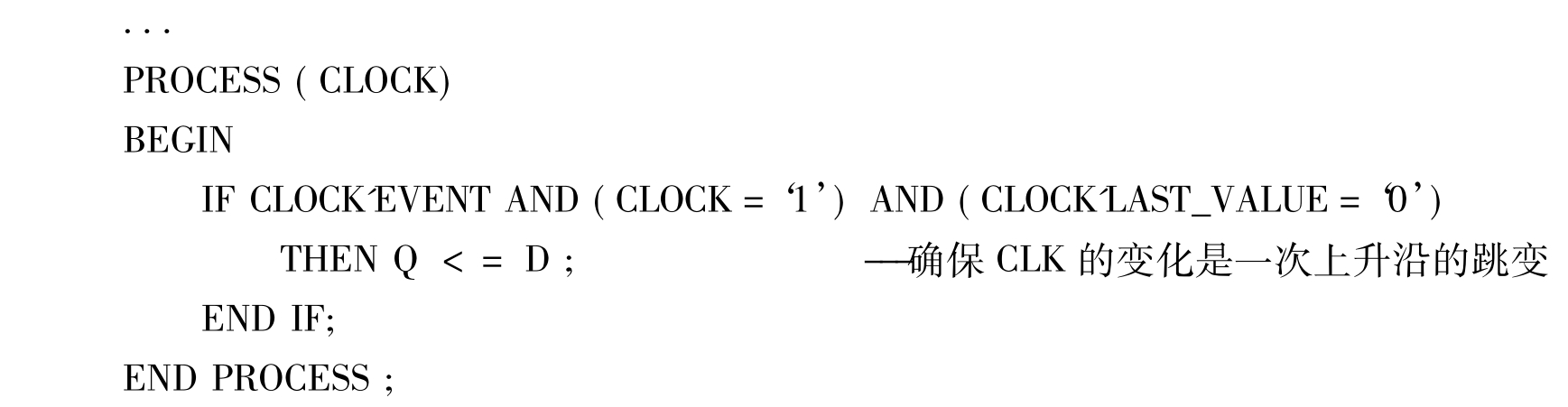

如果将“CLOCK'EVENT”改成如下语句:

![]()

此语句表示对CLOCK信号上升沿的测试。即表示一旦“CLOCK'EVENT”在δ时间内测得有一个跳变,之后又测得CLOCK为高电平1,于是AND两边的表达式都满足条件,两者相与后返回值为TRUE。如果CLOCK的数据类型定义为BIT,便可以从当前的CLOCK=1推断,在此前的δ时间段内,CLOCK必为0。因此语句CLOCK'EVENT AND CLOCK=1可以用来对信号CLOCK的上升沿进行检测。

【例4.44】

![]()

(2)LAST_VALUE

对于普通的BIT数据类型的CLOCK,它只是有1和0两种取值,因而CLOCK'EVENT AND CLOCK=1表述作为对信号上升沿到来与否的测试是正确的。但如果CLOCK的数据类型定义为STD_LOGIC,则其可能的值有9种。这样一来,就不能从“(CLOCK=‘1’)=TRUE”来推断δ时刻前CLOCK一定是0。因此,对于这种数据类型的时钟信号边沿检测,可用以下表达式来完成:

![]()

与EVENT一样,LAST_VALUE也属于预定义信号属性,它表示最近一次事件发生前的值。

【例4.45】

上升沿的测定还可以用以下表达式来完成:

RISING_EDGE(CLOCK)

这条语句只能用于标准位数据类型的信号,其用法如下:

IF RISING_EDGE(CLOCK)THEN

或WAIT UNTIL RISING_EDGE(CLOCK)

(2)STABLE

属性STABLE的测试功能恰与EVENT相反,它是信号在δ时间段内无事件发生,则返还TRUE值。以下两语句的功能是一样的。

![]()

请注意,语句“NOT(CLOCK'STABLE AND CLOCK=‘ 1’)”表达方式是不可综合的。

2)数据区间类属性

数据区间类属性有RANGE[(n)]和REVERSE_RANGE[(n)],这类属性函数主要是对属性项目取值区间进行测试,返还的内容不是一个具体值,而是一个区间。对于同一属性项目,RANGE和REVERSE_RANGE返回的区间次序相反,前者与原项目次序相同,后者相反,见例4.46。

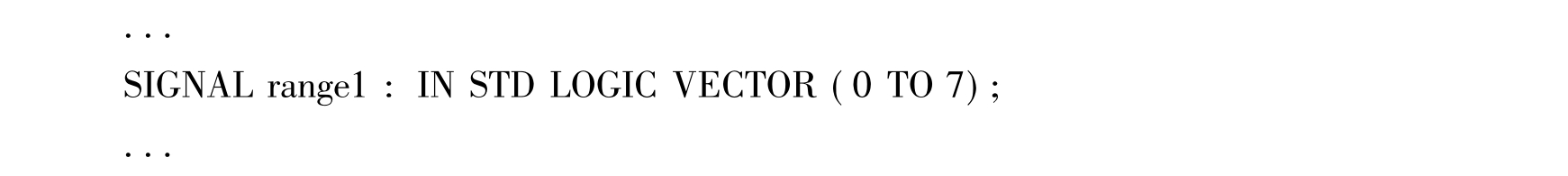

【例4.46】

![]()

本例中的FOR_LOOP语句与语句“FOR i IN 0 TO 7 LOOP”的功能是一样的,这说明RANGE1'RANGE返回的区间即为位矢range1定义的元素范围。如果用REVERSE RANGE,则返回的区间正好相反,是(7 DOWNTO 0)。

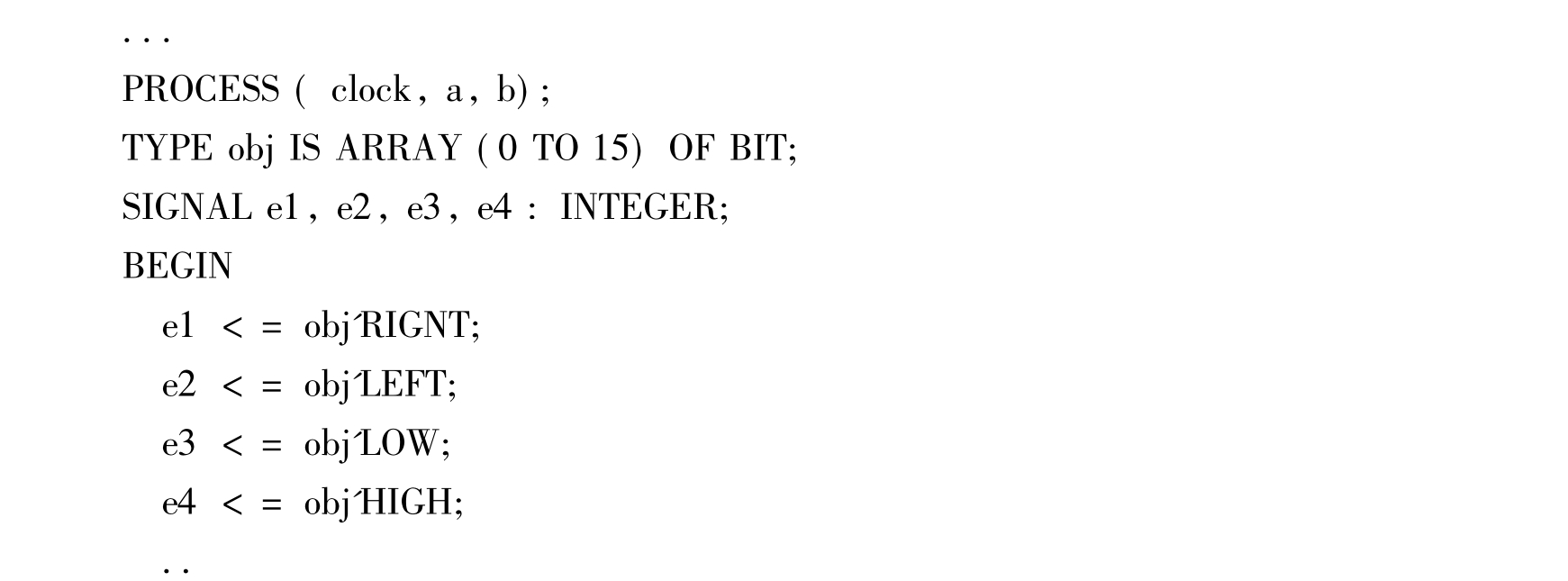

3)数值类属性

在VHDL中的数值类属性测试函数主要有LEFT、RIGHT、HIGH和LOW。这些属性函数主要用于对属性目标的一些数值特性进行测试。

【例4.47】

信号e1、e2、e3和e4获得的赋值分别为0、15、0和15。

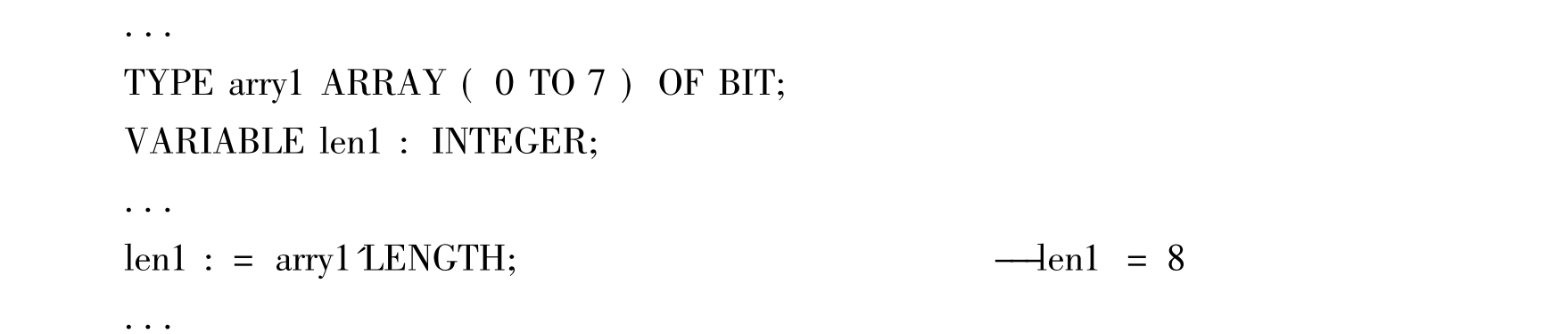

4)数组属性

数组属性LENGTN是对数组的宽度或元素的个数进行测定,用法如下例。

【例4.48】

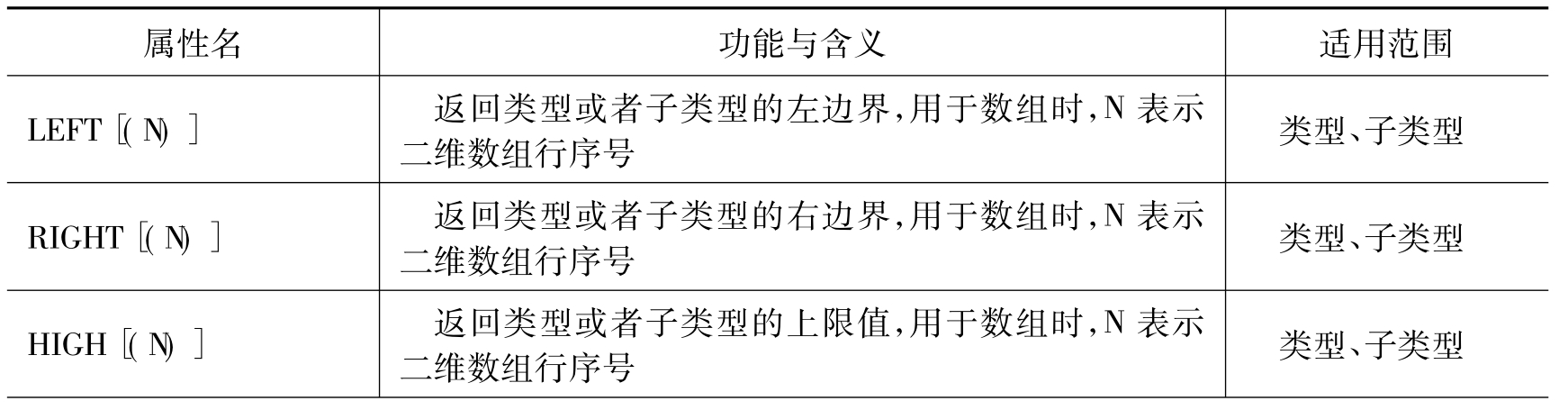

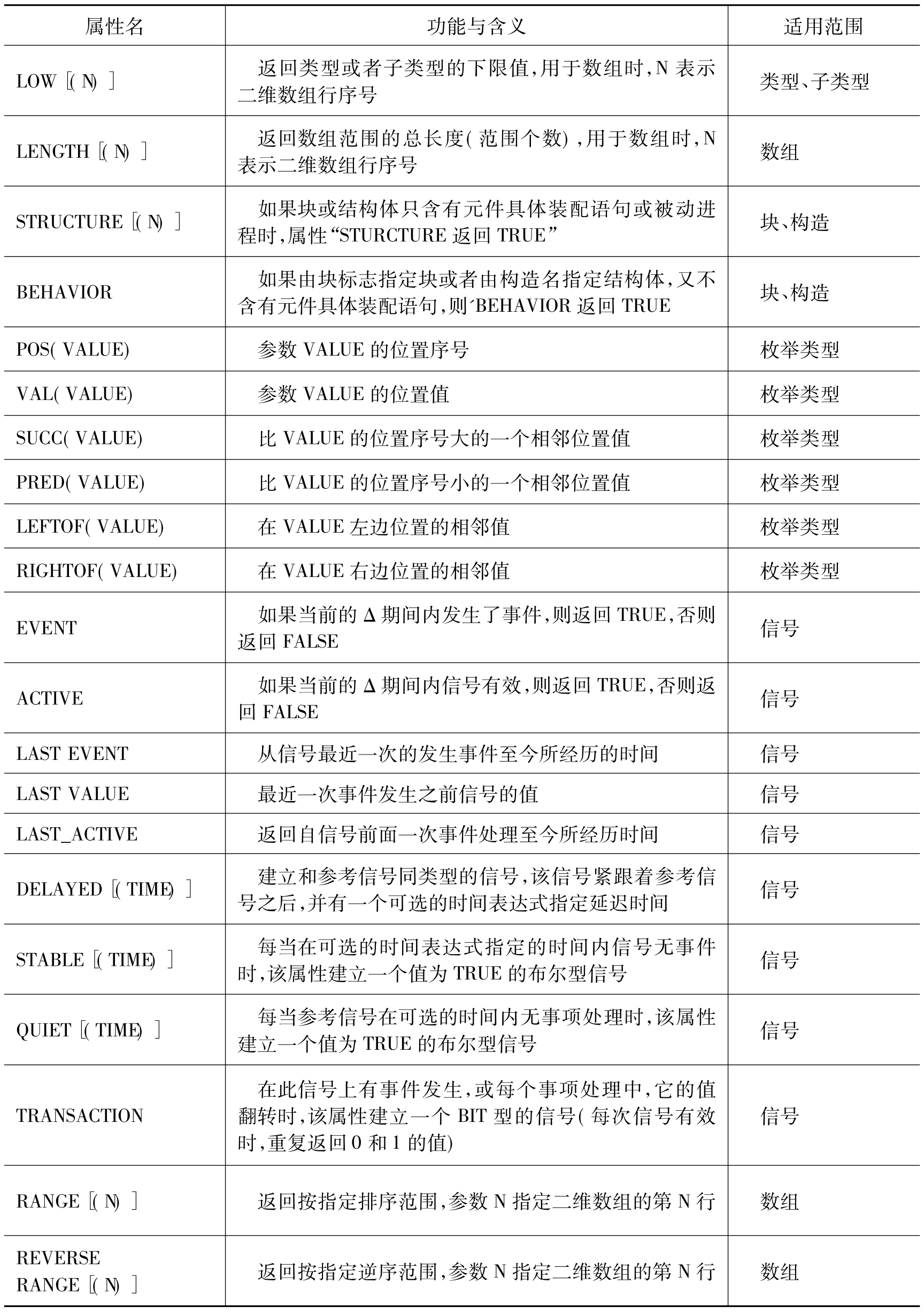

以上介绍了几种常用的预定义属性,其他预定义属性见表4.2。

表4.2 预定义的属性函数功能表

(续表4.2)

5)用户定义属性

属性与属性值的定义格式如下:

![]()

VHDL综合器和仿真器通常使用自定义的属性实现一些特殊的功能。由综合器和仿真器支持的一些特殊的属性一般都包括在EDA工具厂商的程序包里,例如Synplify综合器支持的特殊属性都在SYNPLIFY.ATTRIBUTES程序包中,使用之前加入以下语句即可:

![]()

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。