5.1.3 可编程模拟电路设计举例

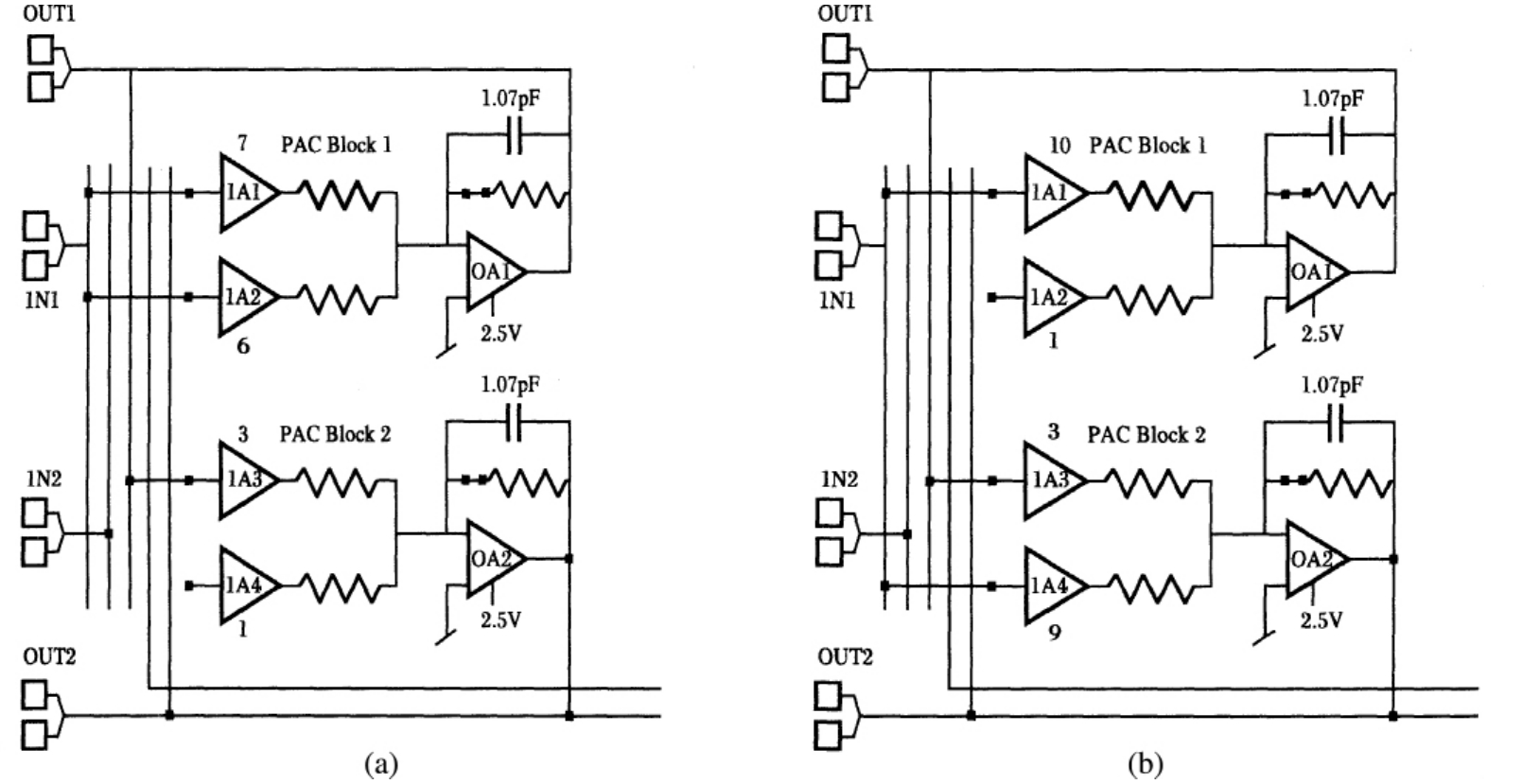

图5.1.33 增益为13的PAC连线图

1)增益的设置

图5.1.33所示的PAC块由一个差分输出的求和放大器OA和两个具有差分输入、增益在-10~+10按整数步长可调的仪表放大器IA组成。OA的反馈回路由一个电阻和一个电容并联构成,其中电阻回路有一个可编程的开关控制其通断,电容回路提供了120多个可编程电容值供选择。

(1)整数增益的设置

图5.1.33是增益为13的放大电路,其中IA1的增益设置为7,IA2的增益设置为6,经OA1求和放大器后,OUT1输出增益为13。很显然,单个PAC块的最大增益为±20。

如果要得到增益大于±20的放大电路,就要将几个PAC级联,如图5.1.34(a)所示为由两个PAC块构成增益为39的级联图。第一个PAC仍然构成增益为13的放大电路,其输出OUT1联到第二PAC的IA3输入,将IA3的增益设置到3,IA4悬空,于是PAC2的增益为3,这样总的增益就是13×3=39,从OUT2输出。

图5.1.34 增益为39的PAC连线图

当然,级联的方法并不是唯一的,增益为39的放大电路也可以用如图5.1.34(b)的方式级联。总的增益是10×3+9=39,从OUT2输出。

图5.1.35 整数比增益技术示意图

(2)整数比增益设置

运用整数比技术,ispPAC器件提供给用户一种无需外接电阻而获得某些整数比增益的电路,如增益为1/10,7/9等等。图5.1.35是整数比增益技术示意图。

在图5.1.35中,输出放大器OA1的电阻反馈回路必须开路。输入放大器IA2的输入端接OA1的输出端OUT1,此时,由输入放大器IA2引入新的反馈通路,并且IA2的增益需设置为负值以保持整个电路工作稳定。在整数比增益电路中,假定IA1的增益为GIA1,IA2的增益为GIA2,整个电路的增益为G=-GIA1/GIA2。若如图5.1.35中选取GIA1=7,GIA2=-8,整个电路增益为G=7/8=0.875。表5.1.5列出了所有的整数比增益值。

表5.1.5 IA2作为反馈单元的整数比增益

(3)分数增益的设置

除了各种整数倍及各种整数比增益外,配合适当的外接电阻,ispPAC器件也可以提供任意的分数倍增益的放大电路。

若想得到一个增益在0.1~0.9之间变化的增益,如:4.3倍,可以按图5.1.36电路设计。

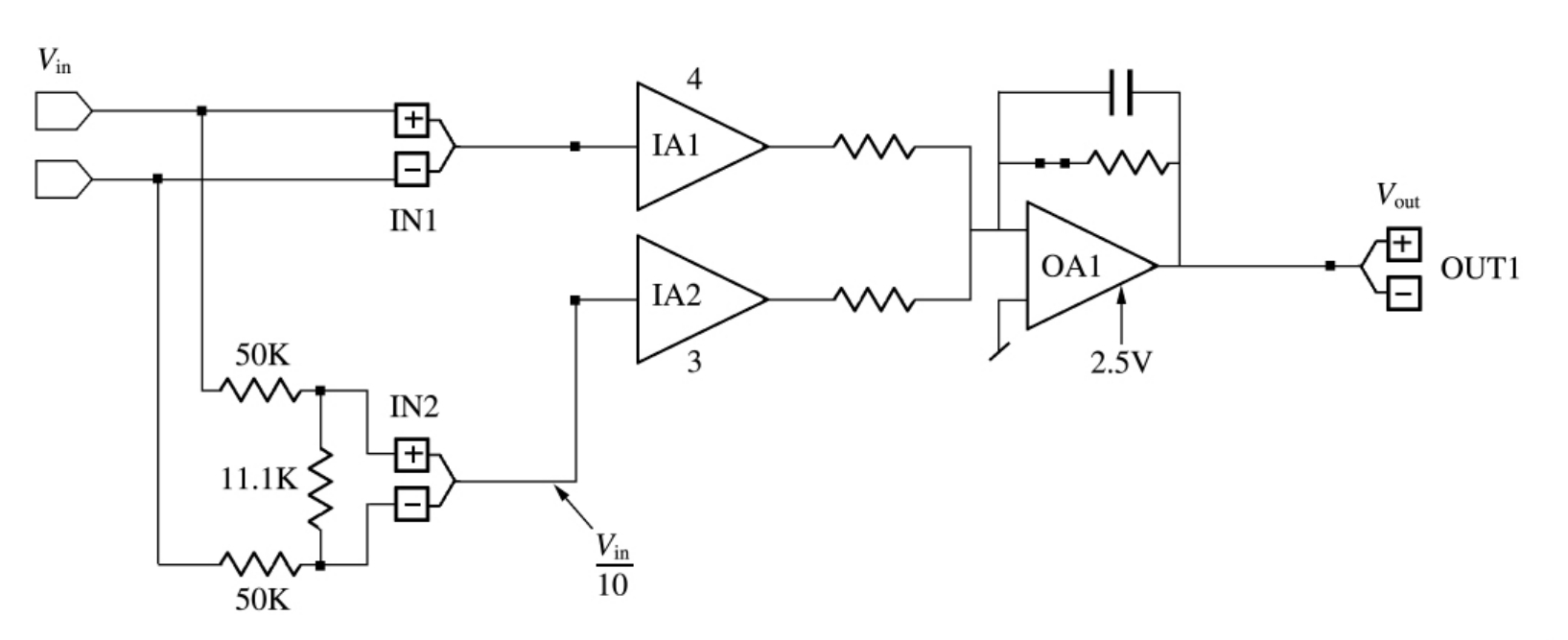

图5.1.36 增益为4.3的PAC块电路图

图5.1.36中,通过外接两个50kΩ和11.1kΩ的电阻分压,得到输入电压:

VIN2=[11.1/(50+50+11.1)]Vin=0.099 9Vin≈Vin/10

这样就相当于芯片之外接一个1∶10的电阻衰减

Vout1=4×Vin+3×VIN2=4×Vin+3×(Vin/10)=4.3Vin

因此 G=Vout1/Vin=4.3

若想得到一个增益在0.01~0.09变化的增益,可将外接的电阻衰减接成1∶100,如:要得到0.43倍的增益可按图5.1.37设计。

此时,VIN1≈Vin/10,VIN2≈Vin/100

所以,G=0.43

图5.1.37 增益为0.43的PAC块电路图

2)滤波器的设计

在系统可编程模拟器件可以实现各种双二阶滤波器,包括低通、高通、带通、带阻。双二阶滤波器的传递函数的一般表达式如下:

图5.1.38 用PAC块构成的双二阶滤波器的实际电路

T(s)=K

式中:c=d=0为高通滤波器;m=c=0为低通滤波器;m=d=0为带通滤波器;c=0、m=d为带阻滤波器。

改变上式不同的分子,可以得到各种滤波器,事实上,只要用两个PAC块就可以实现各种双二阶滤波器,理论推导参见有关ispPAC芯片使用说明。现给出一个实际使用电路图5.1.38所示。

图5.1.39 Run Macro对话框

适当调节电容的数值和放大器的倍数,可以调整滤波器的有关参数。

在系统可编程模拟电路的开发软件PAC-Designer中含有一个宏,专门用于滤波器的设计,只要输入f0(截止频率或中心频率),Q(品质因数)等参数,即可通过宏程序自动实现电路的连接以及电路参数的配制。利用开发软件中的一个模拟器,可以模拟滤波器的幅频和相频特性。

具体操作方法如下:

(1)运行File→New→ispPAC10Schematic,进入电路图设计窗口。

(2)运行Tools→Run Macro,得到如图5.1.39所示对话框。

该对话框中有三种Macro可运行:

ispPAC10_Biquad.exe——产生适用于ispPAC10的双二阶滤波器;

ispPAC10_Ladder.exe——产生适用于ispPAC10的巴特沃斯(Butterworth)、切比雪夫(Chebyshev)等类型的滤波器;

ispPAC20_Biquad.exe——产生适用于ispPAC20的双二阶滤波器。

选择ispPAC10Biquad.exe,点击OK。出现滤波器宏设计输入窗口,在这个窗口下设置参数,如频率f0=100kHz,f0选成优化(Optimize),PAC块选择1&2或3&4。如图5.1.40所示。

点击Generate Schematic,这时完成了线路的连接与参数的设置。同时,将所设计的滤波器电路的实际参数返回到输入窗口。如图5.1.41。可以看到频率f0=100.95kHz,与设计的频率有微小的差别,这是因为影响频率的电容CF1与CF2不连续可调所致。宏设计时,已经尽量将差别降到最小。至此,已完成了电路设计。退出参数设置窗口,只留下设计好的电路图。

图5.1.40 滤波器的宏设计设置

图5.1.41 电路的连接与参数

(3)模拟仿真

图5.1.42 模拟参数设置

设计好的滤波器电路可以直接下载到ispPAC10,也可以先模拟仿真,看看是否与设计的要求相符。

运行Options→Simulator,出现模拟设置参数窗口,选择F start,F stop,Input,Output(如果Output选择Vout1,则得到带通滤波器的特性,如果Output选择Vout2,则得到低通滤波器的特性)等,如图5.1.42所示。

点击Tools→Run Simulator,即启动模拟仿真,得到所设计电路的频率特性。如图5.1.43和图5.1.44所示。

图5.1.43 低通滤波器的幅频和相频特性

图5.1.44 带通滤波器的幅频和相频特性

3)比较器的应用

我们知道在ispPAC20中有两个比较器和一个D/A转换器,利用这两种器件可以构成过压或欠压控制电路,具体方法如下:

图5.1.45 3V过压控制电路

Vin是被监控电压,送入CPIN+,参比电压CPIN-可以是一个直流稳定电压,也可以是VREFOUT(pin2)2.5V,将CPIN连接到比较器CP1的正输入端,CP1的负输入端连接DAC的输出,双击DAC方框,可以改变DAC的输出使之接近CP1的正端值,一旦Vin超过监控值,CP1的正端值大于负端值,CP1输出高电位,产生告警信号。

图5.1.45中,给定的被监控电压是3V,即如果监控电压超过3V,则产生告警信号。将Vin=3V接在CPIN+,同时CPIN-接VREFOUT(2.5V),这时CPIN输入为0.5V,将CPIN连接到比较器CP1的正输入端,CP1的负输入端连接DAC,DAC设定为0.4922V(在DAC中,这个电压最接近0.5V),注意,此时DMODE引脚为0。当Vin超过3V时,CP1的输出为高电平,告警。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。