5.4 差分放大电路

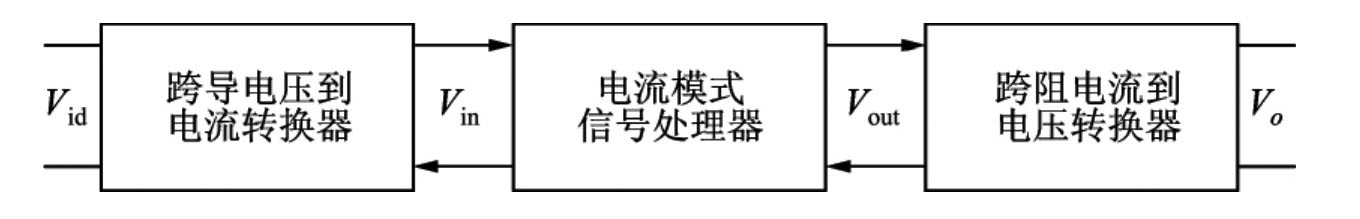

差分对是模拟集成电路中应用最广泛的一种基础线性单元结构,可视为一种特殊的组合电路。差分电路与普通组合放大电路的最大区别表现在对共模与差模信号的区分度上。普通的组合电路对差模与共模信号同样放大,共模抑制比小,限制了电路的应用范围。差分放大电路对差模与共模区别对待,理想情况下只放大差分信号,完全抑制共模信号,共模抑制比无穷大。差分对主要完成输入级V-I转换,即跨导作用,经过中间级的电流信号处理,在输出级完成I-V转换后获得电压输出,如图5-19所示。

图5-19 差分放大电路中的信号变换

差分结构对共模信号的抑制是依靠共模反馈电阻RS以及电路结构和参数上的完全匹配对称而实现的。全对称型的双端输入—双端输出即全差分结构对抑制共模信号十分有效,而单端输出结构对共模信号的抑制仅由交流负反馈尾电阻RS的反馈作用实现。对于差模信号,共源点电位交流接地,电阻RS因短路而不起作用,因此,RS反馈电阻对差模信号的增益没有抑制。差分对双端输出的差模增益与单级CS差模增益具有相同的约束关系。

5.4.1 差分输入级

差分结构保持了差分交流小信号的增益,而有效抑制了输入共模信号的增益,使得电路可以处理不同共模电平偏置下的差模信号。以NMOS差分放大为例,差分输入是在普通CS单级放大的基础上演化而来的。差模信号的动态范围将影响电路中各MOS管的工作状态,对电路增益产生影响,从而导致了电路信号处理的误差。因此,输入差分信号的幅度必须限定在一定的范围内,即动态范围,而线性范围则是包含在动态范围之内的一局部区域。线性范围的大小与非线性失真的容差定义有关。

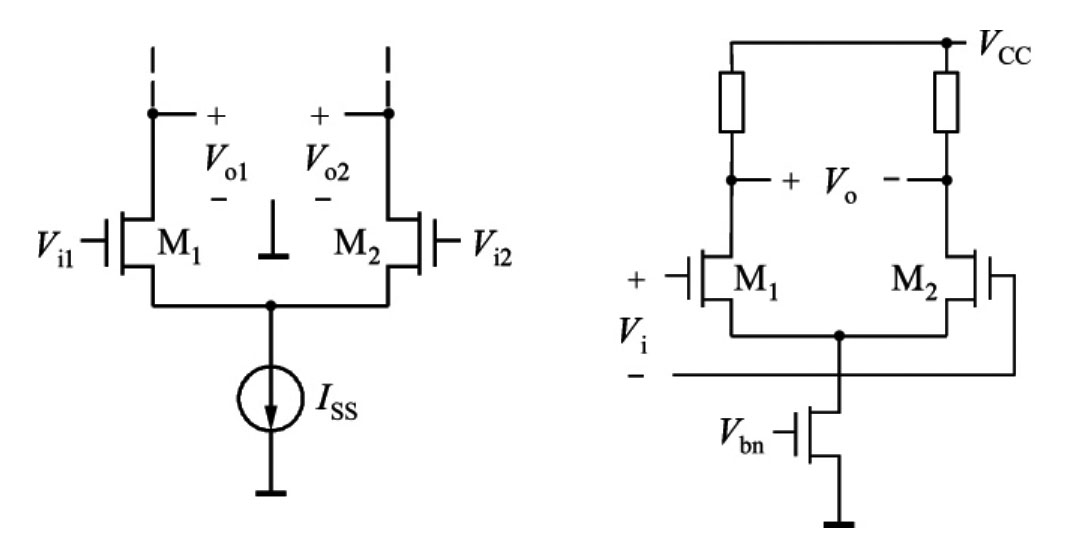

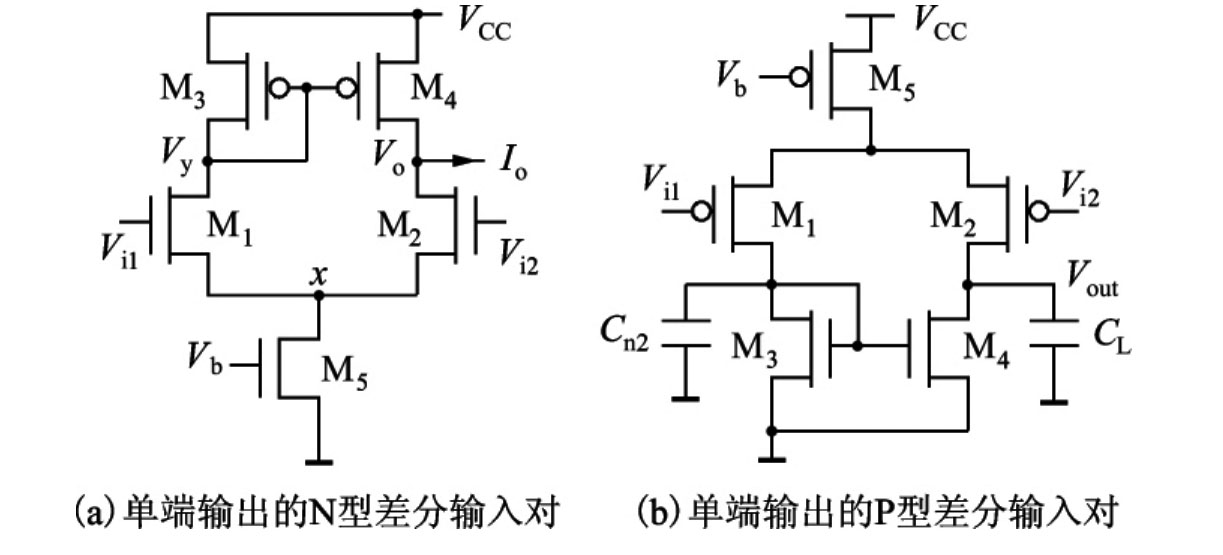

基本的差分电路如图5-20所示,匹配的输入差分对管其源端共接尾电流恒流源,在两对称支路相同的负载上取差分电压输出,构成全差分双端输出。尾电流源的主要作用是利用RS共模反馈电阻扩展输入信号的共模范围,降低共模增益并提高共模抑制比。在基本结构基础上,采用电流镜传输方式将互补变化的电流由MOS二极管传递到输出管高阻支路上,形成宽摆幅单端电压输出,电路如图5-21所示。

图5-20 输入差分对的基本结构

图5-21 单端输出的N/P型差分输入对

假设差分电路中的差模信号为Vid=Vi1-Vi2,共模信号为Vic=(Vi1+Vi2)/2,全差分电路中如果直接取半电路单端输出,则输出电压变化损失一半,全差分结构中的单端输出增益仅为差分增益的1/2。同时,在全差分双端输出电路中,其单端输入的差分信号为Vid/2,单端输出占双端输出电压变化的1/2,则其单管CS增益与输入差分对的增益完全相同。

在差分对的双端转单端输出结构中,由于负载电流镜的电流传输作用,差分对中一放大管的电流与电流镜负载电流极性相反,其差值为单个放大管电流的两倍。全差分输出与双

端转单端输出相比,高阻负载上的电流变化量相同,这种双端转单输出具有与全差分输出完全相同的电压增益。因此,差分电路的实质是以硬件资源和功耗增加为代价,实现共模抑制比性能的提高。根据两差分对管的饱和条件,输出电流与差分输入电压Vid的关系为

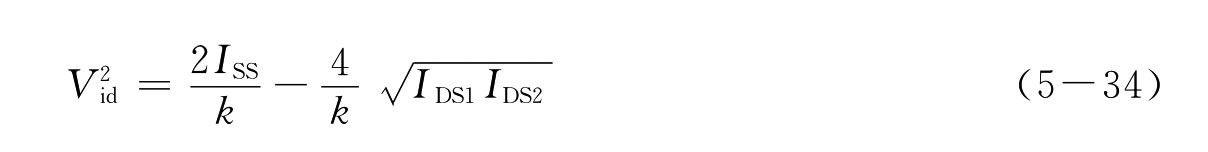

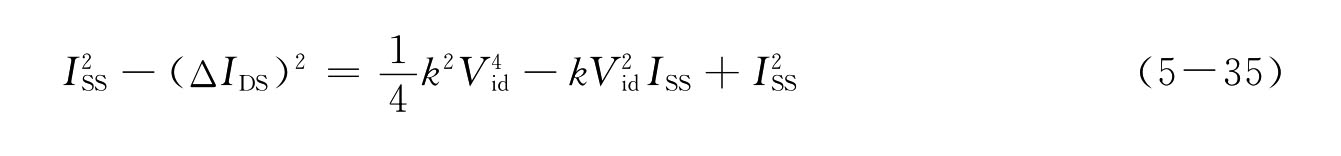

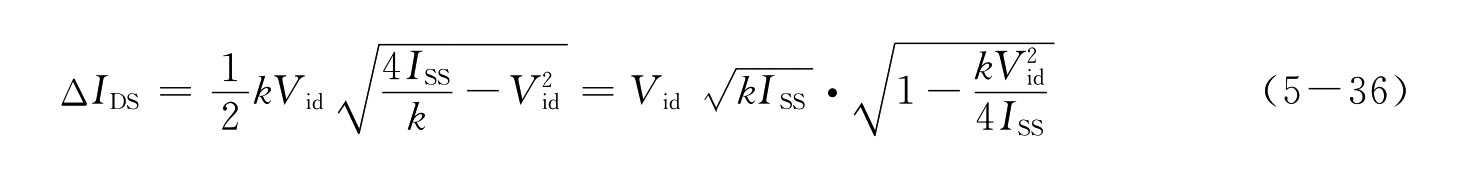

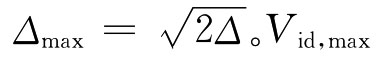

Vid=VGS1-VGS2=Δ1-Δ2,ΔIDS=IDS1-IDS2,IDS1+IDS2=ISS。又由于Δ1=(2IDS1/k)1/2、Δ2=(2IDS2/k)1/2,并得到Vid2与IDS1、IDS2的关系为

利用4IDS1IDS2=(IDS1+IDS2)2-(IDS1-IDS2)2=ISS2-ΔIDS2的数学关系,进一步整理后,得到

由此解出输出差分电流与差分输入电压之间的关系,即

图5-22 基本型差分对的传输特性

根据式(5-36)计算得到的差分放大传输特性曲线如图5-22所示。结果表明,差分输出电流与差分输入电压两者本质上是一种非线性关系。只有在小信号Vid下,输出与输入近似为线性放大关系,因此线性关系是有条件有范围的。线性范围与增益有关,减小增益可以增加差模信号的线性区域。在大信号下,当Vid增大到一定的程度时,一个放大管饱和,电流达到最大的ISS,而另一个放大管截止,处于典型的非线性工作状态。

由式(5-36)并根据ΔIDS=ISS的条件,解出输入的上限范围为Vid,max=(2ISS/k)1/2= 决定了差分输入的动态范围,其大小为ISS尾电流全部流过一个差分输入管而形成的栅过驱动电压。显然,当Vid>Vid,max时,差分对中的一条支路截止,另一条支路流过全部的尾电流,差分输入级进入非线性电阻工作区,增益下降。实际上,当Vid《Vid,max时,在接近最大动态临界范围的区域已呈现一定的非线性,只有在Vid很小的范围内,才具有良好的线性特性,差分信号的线性范围比最大动态范围明显要小。

决定了差分输入的动态范围,其大小为ISS尾电流全部流过一个差分输入管而形成的栅过驱动电压。显然,当Vid>Vid,max时,差分对中的一条支路截止,另一条支路流过全部的尾电流,差分输入级进入非线性电阻工作区,增益下降。实际上,当Vid《Vid,max时,在接近最大动态临界范围的区域已呈现一定的非线性,只有在Vid很小的范围内,才具有良好的线性特性,差分信号的线性范围比最大动态范围明显要小。

根据差分对输出电流与差分电压间的变化关系,如不考虑失调,在Vid<Vidmax的动态范围内为小信号放大的工作状态,起到线性放大器的作用;而在Vid>Vidmax动态范围以外为大信号非线性工作区,低电平输出VL=0,高电平输出VH=VCC,差分放大电路起到比较器的作用。

在动态小信号范围内的放大,信号处理的线性度或非线性失真是一个关键指标。当差分信号相对动态范围仍很小时,并且利用(1-x2)1/2≈1-x2/2近似关系,得到

式中gm为静态工作点下即Vid=0时差分输入对中任一单管的跨导参数。

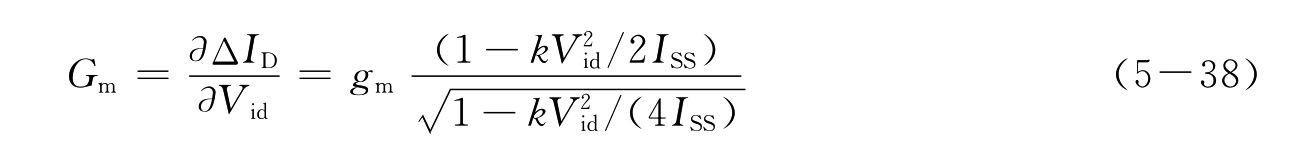

根据跨导参数的定义,基本差分对在整个动态范围内的跨导Gm可表示为

显然,Gm与差分输入信号密切相关,表现出的非线性关系为差分电压增大,跨导下降,同时增益也随之降低。只有在Vid趋近于零的很小线性范围内,跨导变为线性常数,即Gm=(ISSk)1/2=gm,与普通单级增益中的gm关系相同。由于差分放大存在同相与反相两个输入端,因此,同相端的小信号差模电压增益为Avd=GmRo≈gmRo。

基本类型差分放大器的差模增益与普通CS电压放大器相同。若差分放大器的输出为低阻,则输出电压摆幅降低,输出驱动电流增大,但差分对因电压增益性能变差而不实用。当输出为容性负载时,在低频下负载容抗很高,电路具有很高的电压增益。当频率增加后,负载容抗下降导致电压增益衰减,此时实现的是电流放大。这种实现电流线性驱动功能的差分放大器,通常又称为线性跨导放大器OTA。对OTA电路的基本要求首先是跨导gm值高,同时要求它的线性范围宽。OTA对负载电容的最大驱动电流为ISS,因此最大压摆率SR受到差分对尾电流的限制。

5.4.2 输入失调电压

失调影响电路的精度,形成固有偏差和失真,理想线性放大电路的输入失调电压为零。在一般应用条件下,需将失真降到最低。而在某些特殊场合,可利用运放的失调完成一些特殊的控制和信号处理功能。

当电路存在失调时,即使在输入信号匹配的条件下,差分电路输出级也可能偏离静态点甚至进入非线性饱和电阻区,就如同无失调的理想差分电路在Vid差分输入下,使输出级产生相应的变化而偏离静态工作点或进入线性电阻区。对于实际运放,将输出电压调节到静态工作点所需施加的差分输入信号Vid定义为输入失调电压,输入失调电压是各类不匹配源对电路整体影响的综合体现。

1)输入失调电压的形成

失配是引起运放失调的主要因素,下面将以差分对为例分析失配对输入失调电压的影响。电路中的失配根据其形成机制和特点,可分为随机失配和系统失配两大类,与此对应的失调分别为随机失调与工艺失调。随机失配主要由器件参数的不对称变化引起,如VTH、W/L的失配等,随机失配的重要特征是其大小和方向(正负)无法人为确定,与加工工艺的波动性有关。系统失真由电路工作点的失配引起,而系统中各结点的工作点可以人为设计确定或干预,因此其大小和方向都是可以控制的。

随机失调由受工艺影响的相关器件参数变化或失配而引起,主要包括VTH、k′、W/L等参数。

(1)阈值电压失配引起的失调

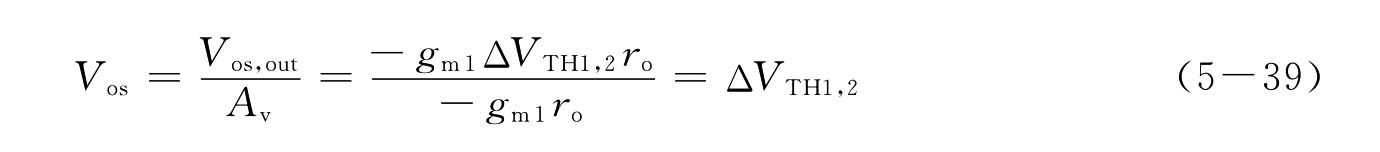

如图5-21,差分输入级要求输入对管M1与M2匹配,同时电流镜负载对管M3和M4匹配。输入差分对管VTH的失配直接导致输入电流误差,该误差电流经过负载变换到输出电压后,再折算到输入,有

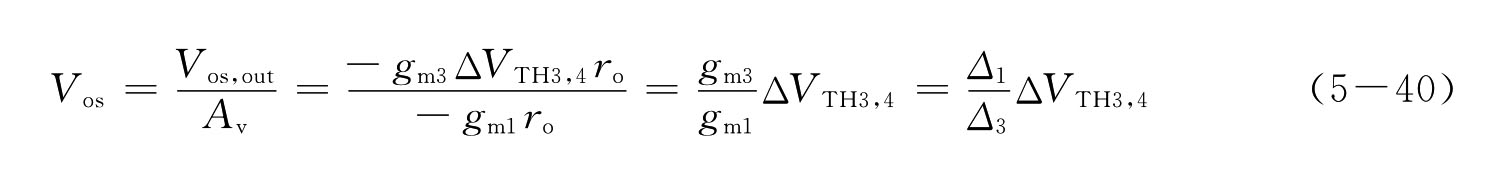

利用IDS/gm=Δ/2的关系,即在电流相同的条件下gmΔ为常数,则对于负载电流源对管VTH的失配,其等效到输入端的失调电压为

(2)工艺因子失调

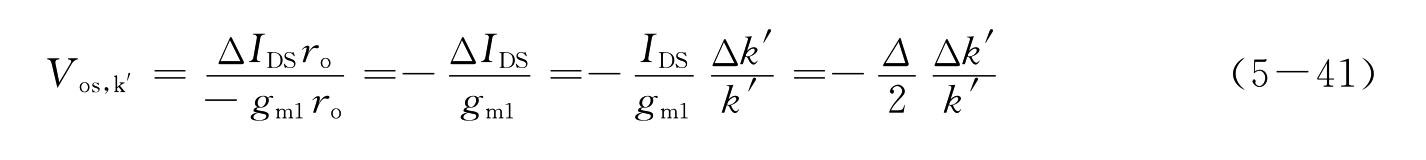

根据aIDS/ak′=(W/L)Δ2/2=IDS/k′定义,得到ΔIDS=(Δk′/k′)IDS关系,则

(3)MOS管W/L失配引起的失调

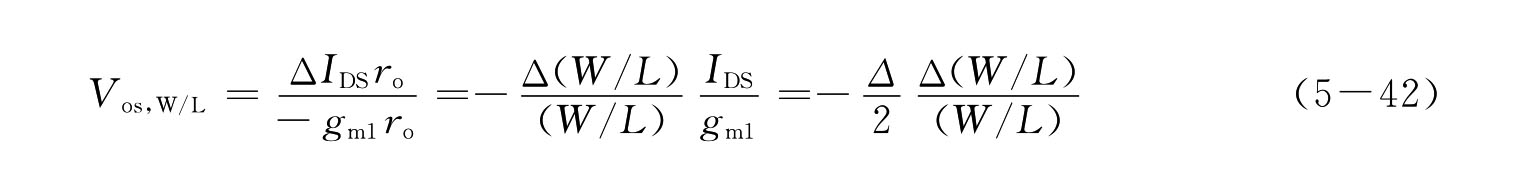

器件尺寸(W/L)变化同样会引起电流的变化,其变化规律与k′因子影响的规律相同,即aIDS/a(W/L)=IDS/(W/L),则W/L失配引起的失调电压为

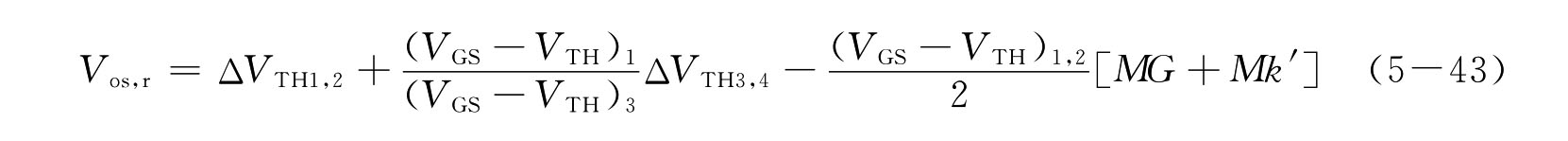

定义差分对图形失配因子MG=∑[Δ(W/L)/(W/L)]i。对于差分输入级,i=1对应于输入对管的相对尺寸偏差,i=2则对应为恒流源负载对管的尺寸偏差。同样,定义差分对工艺失配因子Mk′=∑[Δk′/k]i。对于差分输入级,i=1对应于输入对管的相对k′因子偏差,i=2则对应为恒流源负载对管的k′因子偏差。aVos,W/L/aVGS=-MG/2,aVos,k’/aVGS=-Mk′/2,得到总的随机失调电压为

降低MOS管开启电压VTH失配以及图形失配,成为降低随机失调的关键所在。同时,电路工作状态对随机失配也存在一定影响,应降低负载与输入差分对的跨导之比,同时降低输入差分对管静态工作点下的过驱动电压。

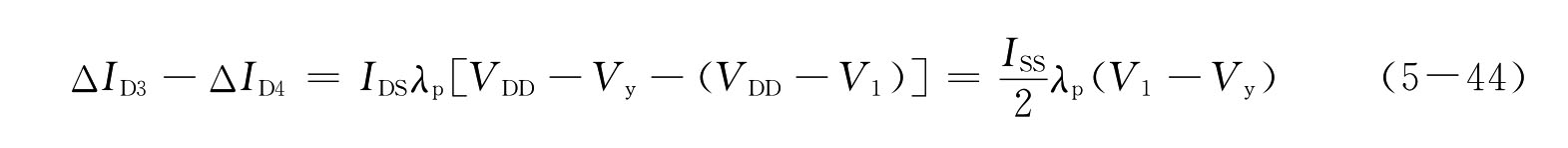

系统失调由静态工作点失配而引起。电路中电流镜的VGS电压匹配,系统失调主要由电流镜VDS电压的不匹配ΔVDS而引起,并导致电流在的传输过程中产生误差。电流镜ΔVDS电压失配引入的电流失配ΔIDS=gdΔVDS=λIDSΔVDS。如图5-21中所示,设差分对有源负载中的PMOS输出管漏电位V1=Vo,与之对应的电流镜漏电位为Vy。当电压V1与Vy失配时,产生的电流失配为

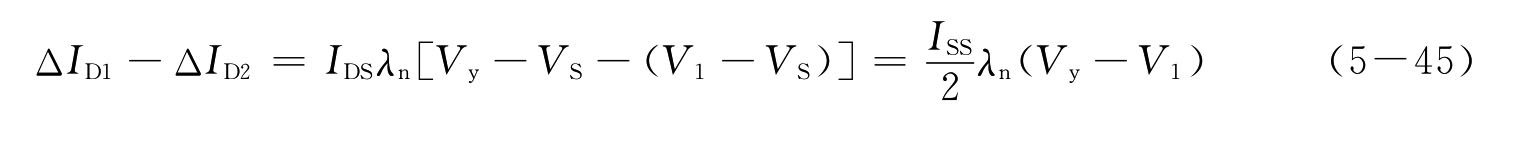

同理,输入差分对管漏电位失配带来的电流失调为

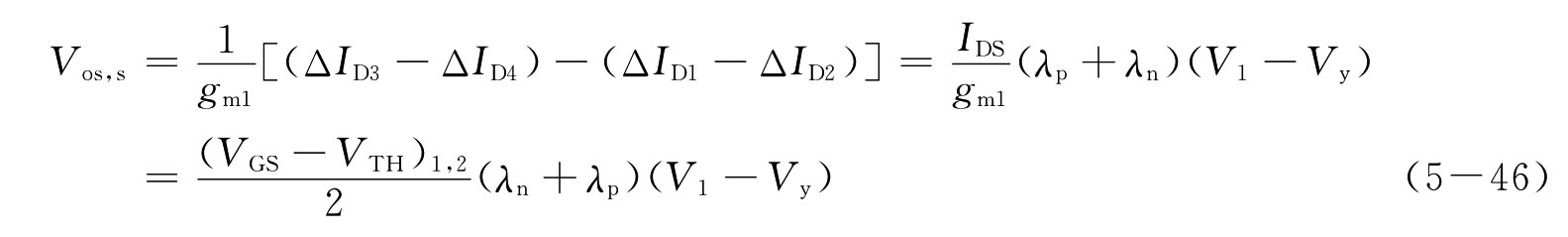

可见差分对与负载电流镜失调电流的变化方向相反,输出电流失配的净变化应为两者之差,因此它们对输出电压变化的影响相同,由此引入的系统工作点失配而产生的输入失调为

可见,减小系统失调的主要方法是降低V1和Vy的电位失配,可通过W/L与后级放大管的匹配设计使V1=Vy。此外,提高输出阻抗(降低λ值)、提高(W/L)1(以降低过压驱动)对降低系统失调也有一定作用。通常条件下,系统失调一般远低于随机失调。

2)输入失调的影响

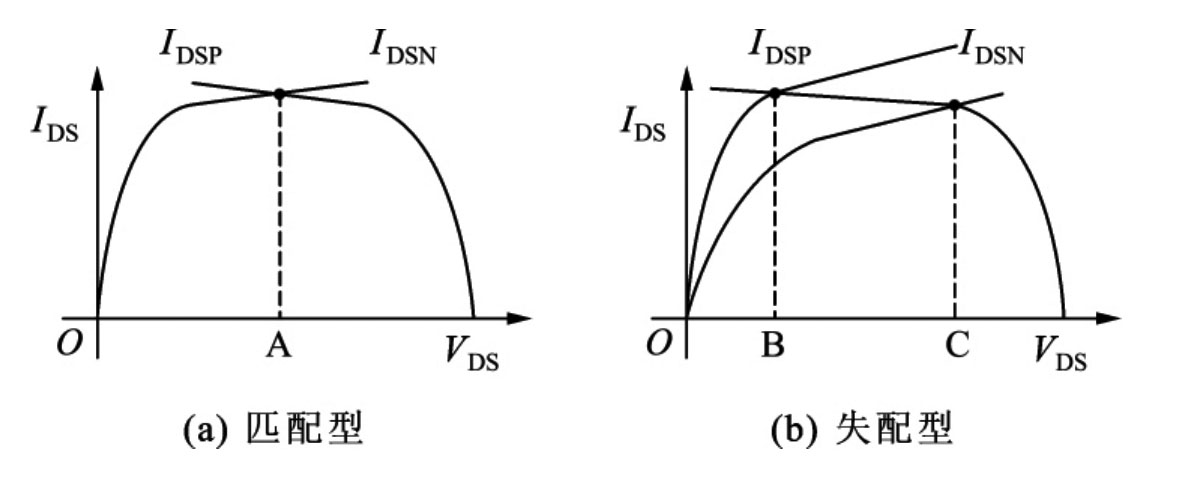

开环运放的高增益依赖于高的输出阻抗,而高的输出阻抗导致输出共模点难以精确控制。设输出级为NMOS放大管的CS增益,PMOS恒流源提供有源负载,在静态工作点VGSN0的偏置下,NMOS放大管同样表现为输出恒流特性。根据图5-23(a)显示的结果,当VGSN0设置恰当,即与PMOS恒流输出相互匹配,使输出静态工作点位于A,即Vo(A)=VCC/2,则当输入信号在此静态点有交流小信号输入时,IDSN饱和电流响应变化。Vi增加使IDSN增加,与IDSP的交点位置A左移,输出电压下降;同样,Vi下降使IDSN减小,与IDSP的交点位置A右移,输出电压增加。NMOS与PMOS源漏电压VDS满足临界饱和所对应的输出电压范围,即构成了线性放大增益电路输出电压变化的动态范围。由此得到如下结论,首先,放大管与负载管的恒流特性越强,即输入阻抗越高,达到动态范围内的输出变化所需要的输入电压变化越小,增益越高;其次,为使以上Class A模式下的放大电路输出信号具有正负对称的输出摆幅,静态工作点应当设置在电源电压的中点。

图5-23 高阻负载输出电位变化

因此,对于Class A放大器,输入增益管的静态偏置尤其重要。如果放大管与负载管的输出阻抗均无穷大,则两者饱和电流相同时的交点A为无穷多,则静态工作点VA无定义;当两管当中至少一个为有限阻抗,则可以获得一个惟一的VA交点,而当饱和电流略有变化时,VA电位有很大的变化。显然,输出阻抗越高,增益越大,则输出静态点的控制难度越高。

如果设置不当造成NMOS与PMOS恒流特性失配,则静态点可能偏离理想的位置。如图5-23(b)中,若VGSN0偏大导致静态点偏移到较低的B点位置;同样,若VGSN0偏小则静态点偏移到较高的C点位置。静态工作点偏离理想的A点位置后,在Class A的工作模式下,造成输出动态范围减小,失真增加。

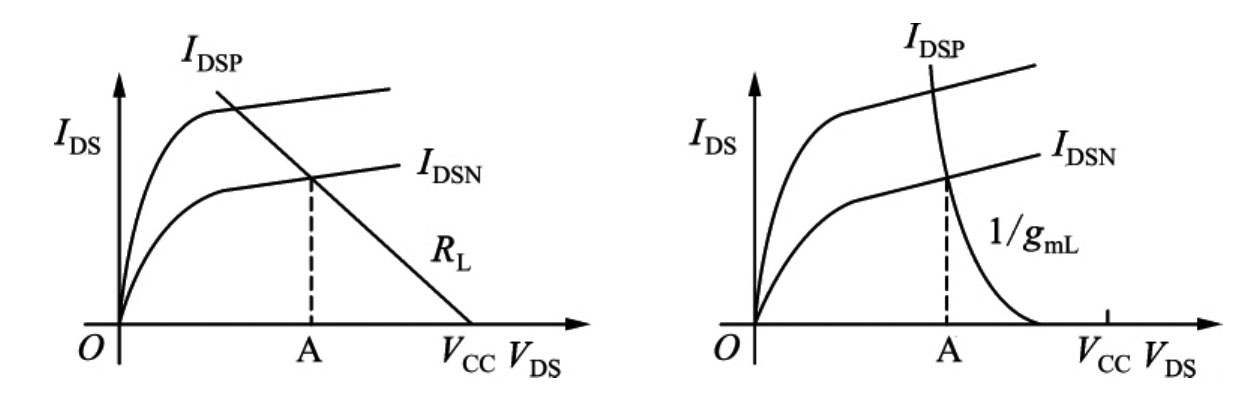

抑制输出共模静态点漂移的根本方法在于降低支路的输出阻抗,负载可采用无源线性电阻RL或非线性MOS二极管电阻。如图5-24所示,设置负载RL的大小可很方便地将A点设置在电源中点附近;而对于1/gmL的负载结构,由于MOS二极管的钳位作用,输出静态点钳制在距离VCC的VTP+Δp附近,动态范围和增益明显减小,但静态点的设置更为方便。

图5-24 低阻负载输出电位变化

在高阻负载下,当输出共模信号静态点发生漂移时,需要采取外部控制的方式使工作点设置到所需的位置。其控制的基本原理在于改变恒流源的电流值,具体有两种实现方式。一种是改变放大管的输入电压,调节放大管的电流使输出静态点改变,对于差分电路即需要施加一定的差分输入电压使输出定位在所需要的静态点,此差分输入电压即为运放的失调。另一种是改变负载恒流源的偏置,通过调节负载电流使静态点达到所需位置。在全差分电路中,通常是采用这种方式实现共模负反馈,稳定设置差分输出的共模静态点。

差分放大器一般用于闭环负反馈系统。以电压串联负反馈为例,若输出通过反馈网络反馈到运放的反相输入端,则运放输出电位由同相端输入信号定义。通常该输出点在运放理想静态点附近,则所需的输入差分电压为输出与静态点的变化量与增益的比,即输入分辨率;否则,当电路存在失调时,首先需要在输入端施加失调量的差分输入电压,使电路进入线性工作区,再叠加有效的差分输入电压后,将输出调节到所需的状态。显然,当运放输入失调远大于信号的分辨率时,将使运放的控制精度下降,引入较大的失真。

5.4.3 共模抑制比CMRR

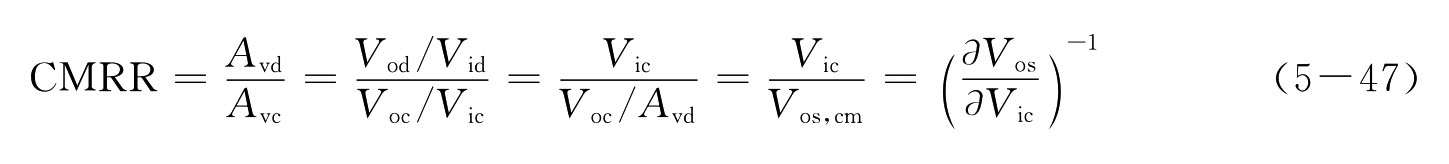

运放相对于普通组合放大电路的最显著优点是输入共模范围大,共模抑制比高,因此提高运放的共模抑制比至关重要。当共模信号从差分对管的栅极输入时,高的CMRR可争取到足够的差模信号摆幅空间。当共模信号从差分对管的漏或源感应输入时,高的CMRR即对应于高的PSRRVDD和PSRRVSS,可显著降低电源噪声的影响,提高电源和地的噪声抑制比。CMRR可定义为差模增益Avd与共模增益Avc之比。理想运放由于Avc=0则CMRR趋近无穷大。然而,实际运放中由于对称结构中存在的各种失配影响,Avc增加导致CMRR下降。因此,CMRR与运放失配的关系为

式中:Vic——输入共模信号;Voc——共模输出信号。

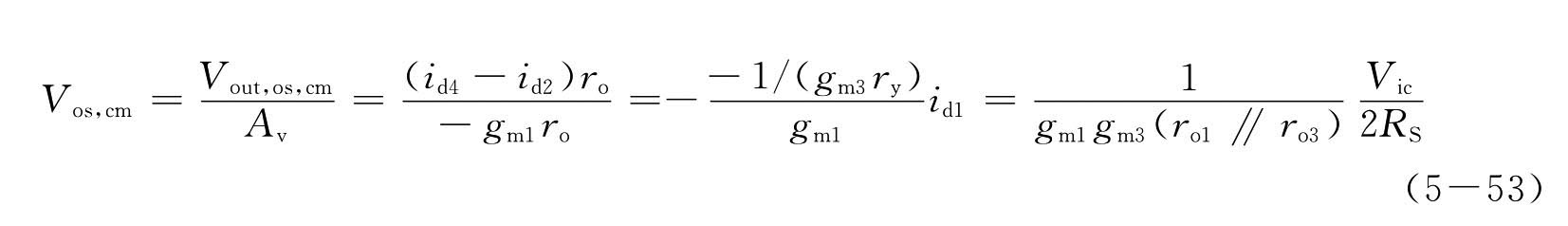

在输入Vid短路条件下,共模输出Voc由于是失调引起,则其等效到输入的差模失调电压Vin,CM=Voc/Avd,Vic与Vos,cm的比例关系决定了电路的CMRR特性。也就是说电路失配引入的输入失调,将大幅度降低电路的CMRR性能。根据不同的失配贡献,CMRR为各失配条件下CMRRi的并联求和,即

1)系统失配下的CMRRs

如图5-21(a)所示,根据M5管交流电阻RS对共模信号的交流负反馈控制作用,共模信号的有效跨导为Gm=gm1/(1+2gm1RS)≈1/(2RS),则由定义直接得到由系统工作点失配决定的CMRR为

从电流失配的角度分析,由差分对栅极输入的共模电压Vic引起尾电流的变化并传递到M1/M2差分对中,有id1=id2≈ix=Vic/(2RS)。id1和id2电流变化后,导致差分对管的VD漏电位即M3管的VG栅电位发生相应变化,而M3管栅压的变化又引起自身电流的改变。由于电流连续,电流变化的方向一致,即

gm3ΔVx+gyΔVx=(gm3+go1+go3)ΔVx=id1=id3(5-50)

而M4中的电流变化主要从M3的变化电流感应得到,设1/ry=gy=go1+go3,得

则差模输出电压ΔIDS=id4-id2=id4-id1=id1(id4/id1-1),代入上式后得

该失调电流在负载上形成的输出电压为Vout,os,cm=ΔIDro=(id4-id2)ro,输出失调电压等效到输入端后,得到的等效输入失调电压为

根据中低频率下共模抑制比与等效输入失调的关系,计算得到由系统失配引起的CMRRS=2gm1gm3RS(ro1∥ro3),得到与电压模分析方式相同的结果。

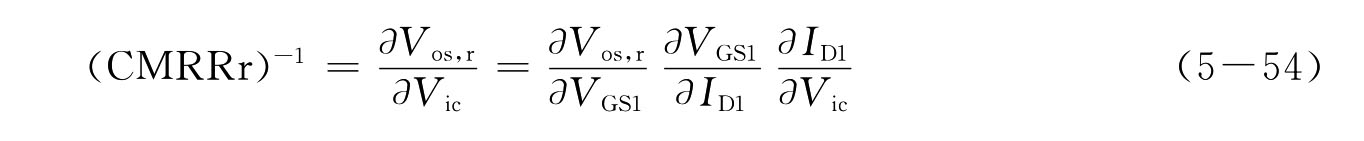

2)随机失配下的CMRRr

根据随机失调Vos,r与电路静态工作点状态和输入共模信号Vic的关系,即

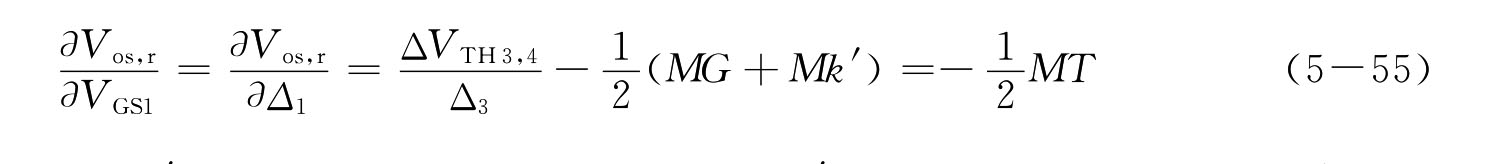

根据式(5-43)的失配参数关系,得到

式中,MT=MG+Mk′-2 MVTH为包含图形、工艺因子k′和开启电压VTH的总失配参数因

子,其中MVTH=ΔVTH3,4/Δ3。

由于失配因子的随机变化,MT可正可负,考虑最差状态下的失配因子并对其取绝对值,CMRRr=4gm1RS/|MTmax|。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。