10.10 设计规则检查(DRC)

设计规则检查(DRC)有两种方式,即实时DRC(On-Line DRC)和分批DRC(Batch DRC)。

1)实时DRC

实时DRC是在放置或移动图件的同时,系统自动利用规则进行检查,一旦发现违规(Violation),就会被标记出来(显示为高亮度)。同时,如果PCB浏览管理器设为违规浏览模式,其中会显示违规的名称和具体内容。

实时DRC只检查设置项目的规则,检查的项目可以调整,这种调整是通过执行“Tools\Design Rule check…”命令进行的,在“Design Rule check…”对话框的“On-Line”选项卡中完成。如图10.128所示。

图10.128 “On-Line”选项卡

2)分批DRC

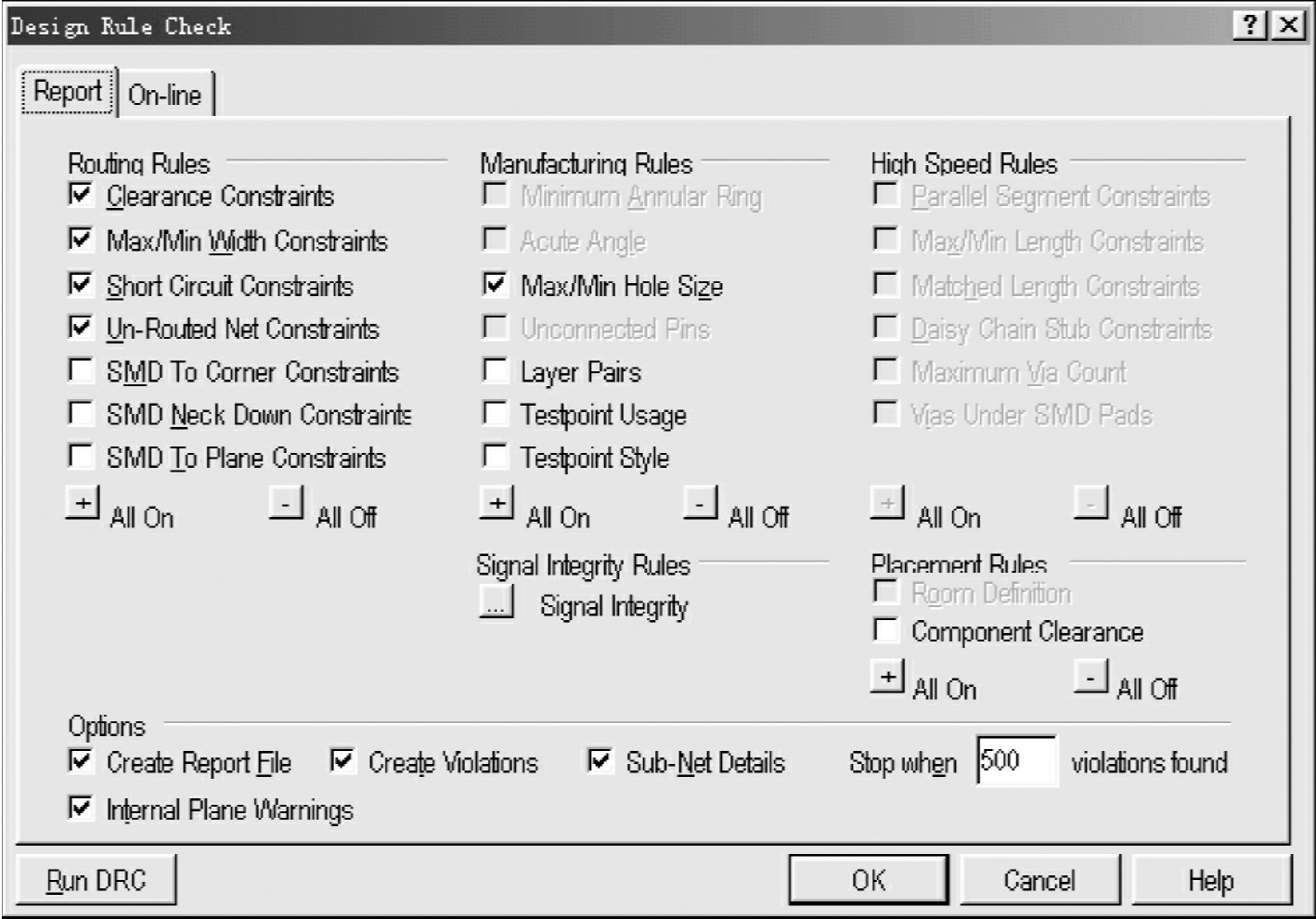

分批DRC的运行是用户控制的,其结果是产生一个报告文件。单击定义设计规则对话框中“Run DRC”按钮,或执行“Tools\Design Rule check…”命令,都会弹出如图10.129所示的对话框。设置分批检查项目是在该对话框的“Report”选项卡上进行的。

图10.129 “Report”选项卡

3)处理违规

当执行一次分批DRC后,如果发现DRC报告中有大量错误,就需要设法减少一次分批DRC中出现的违规个数,有以下两种方法:

(1)在“Design Rule Checking”对话框的“Report”选项卡中,减少“Stop when…violation found”栏的值,例如10个,这样报告文件中将最多出现10个违规说明。这就可以先解决这10个违规,然后再检查再修改,直到所有的违规被排除。

(2)在“Design Rule Checking”对话框中,一次只选取一项进行检查,这样检查报告中只出现1种类型违规的说明,于是就可以很迅速地排除所有的违规错误。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。