【摘要】:SystemVerilog有一个预执行步骤是细节构建。当子组件在其父构造函数中实例化时,构造函数就像链条一样连接在一起。每一个子组件实例化时,都会调用构造函数。构造函数的主体是一系列绑定的指令操作把组件与信号或子组件的端口连在一起,这些绑定的组件由构造器的初始化程序来实例化。这样一个完整的设计就由顶层的组件实例化下属组件而创建。

11.5 实例化与细节构建

SystemVerilog有一个预执行步骤是细节构建。所有的静态组件——模块、程序块和接口等都在这一步骤中创建和初始化。当第一个初始化模块执行的时候,整个设计便就位了。

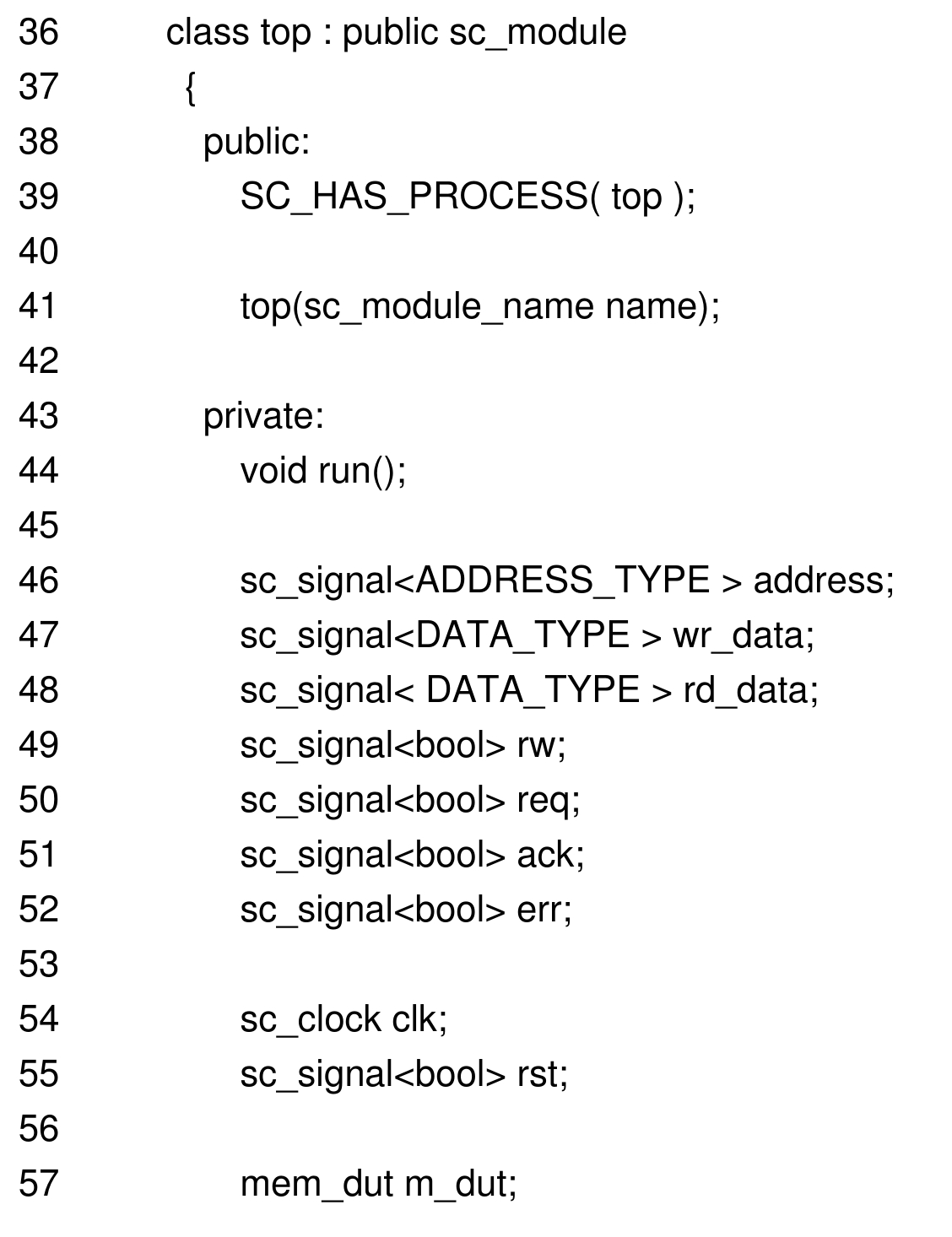

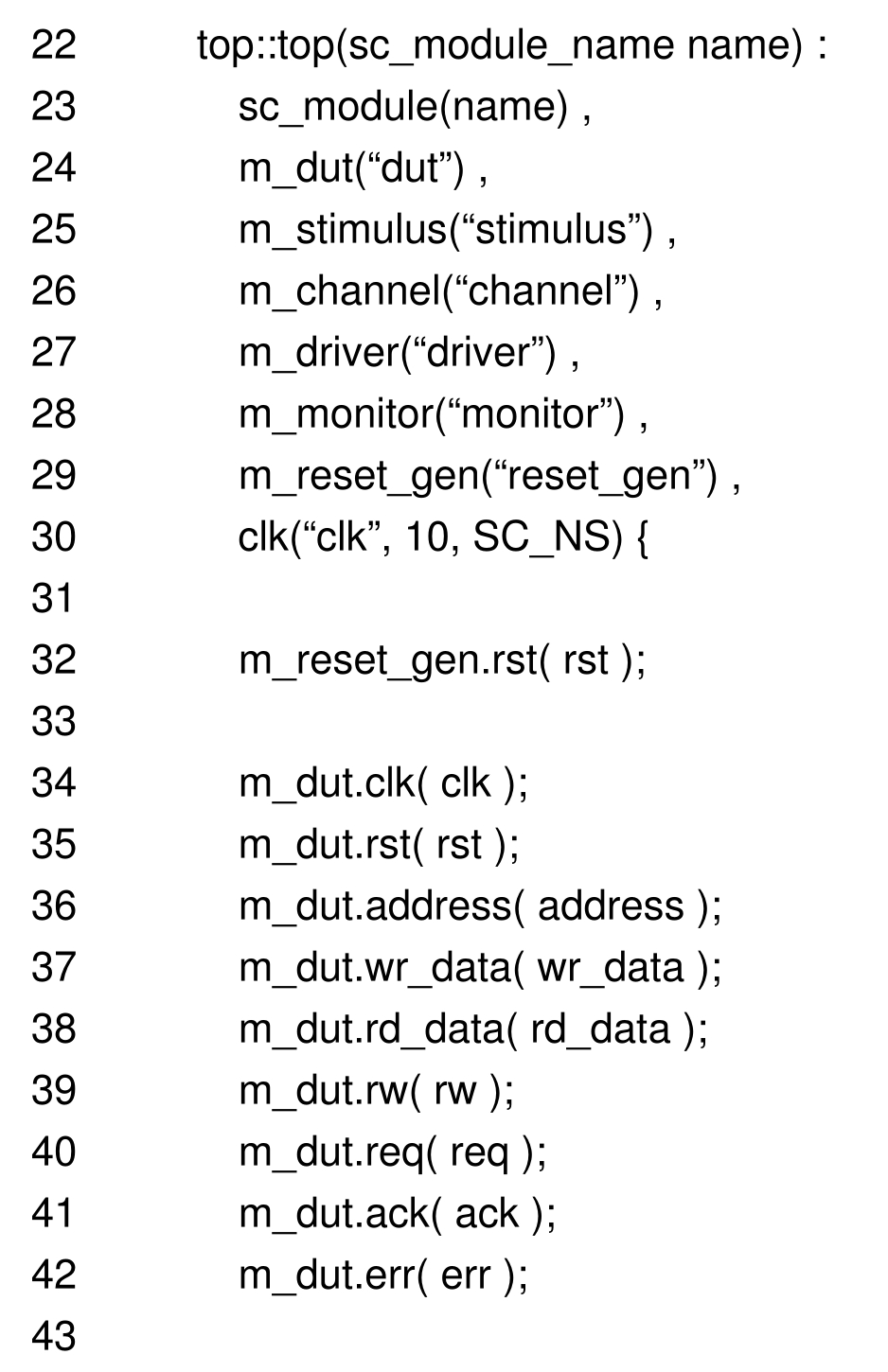

SystemC同样存在这个细节构建步骤。SystemC的构建同使用C++的动态库一样,所有对象是动态分配的类,因此创建这一步骤不像SystemVerilog那样是隐蔽的,而是由一系列构造函数完成的。当子组件在其父构造函数中实例化时,构造函数就像链条一样连接在一起。例如,第6章内存验证平台,其顶层模块定义了大量的连接众多组件的信号。

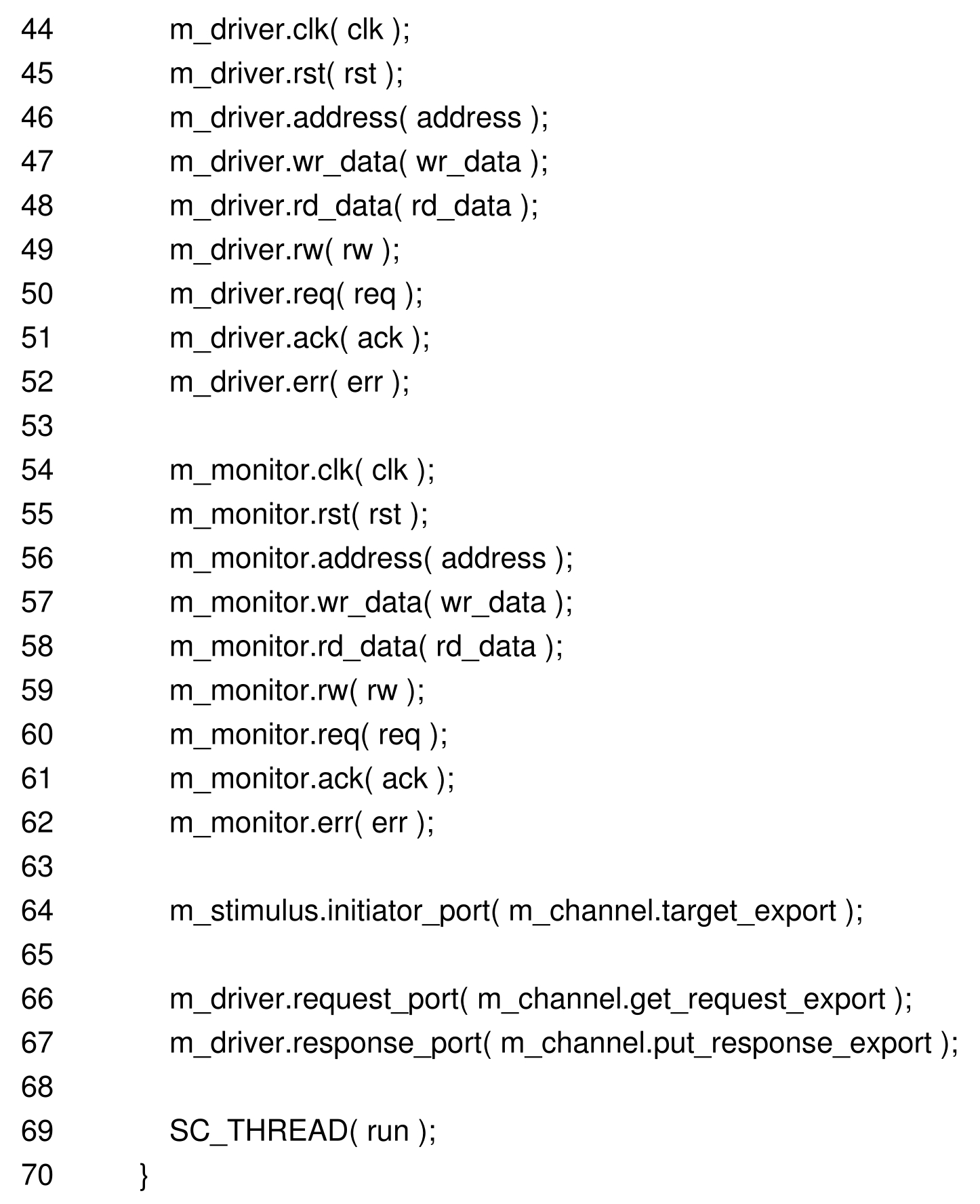

下面的构造函数做了两件基本的事情:实例化所有的子组件并连接它们,这些组件在上面类的定义中已经声明。每一个子组件实例化时,都会调用构造函数。这些构造函数也会实例化并连接组件。

构造函数的主体是一系列绑定的指令操作把组件与信号或子组件的端口连在一起,这些绑定的组件由构造器的初始化程序来实例化。

这样一个完整的设计就由顶层的组件实例化下属组件而创建。顶层组件自上而下依次实例化其各层子组件,这些组件由一系列绑定操作连接在一起。

在SystemVerilog中使用AVM时,组件使用同样的方法创建,即通过一系列构造函数和绑定操作来完成。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。