12.2 低压单元电路

目前,低功耗电路系统的电源电压一般在1~5V范围内变化。不同电压驱动的电子系统,其电路设计所关注的重点是不同的。对于低压电子系统,首先关注的是电路的最小工作电压。从理论上看,电路支路可正常工作但输入或输出动态范围却为零时所对应的电压,为各支路的最小工作电压。其次是低压系统信号处理的动态范围幅度。以VTN=0.7V的NMOS差分对为例,若NMOS尾电流恒流源VDS,sat饱和压降为0.2V,则输入驱动共模信号的最低值至少达到1V以上,占3V电源电压摆幅的1/3。对于普通源跟随器,同样在以上条件下,VTH电平移位将增加35%~40%输出动态电压范围的损失。当电源电压下降,特定结构类型电路的输入与输出动态范围损失的比重还将增大。

12.2.1 电路低压工作的VTH限制

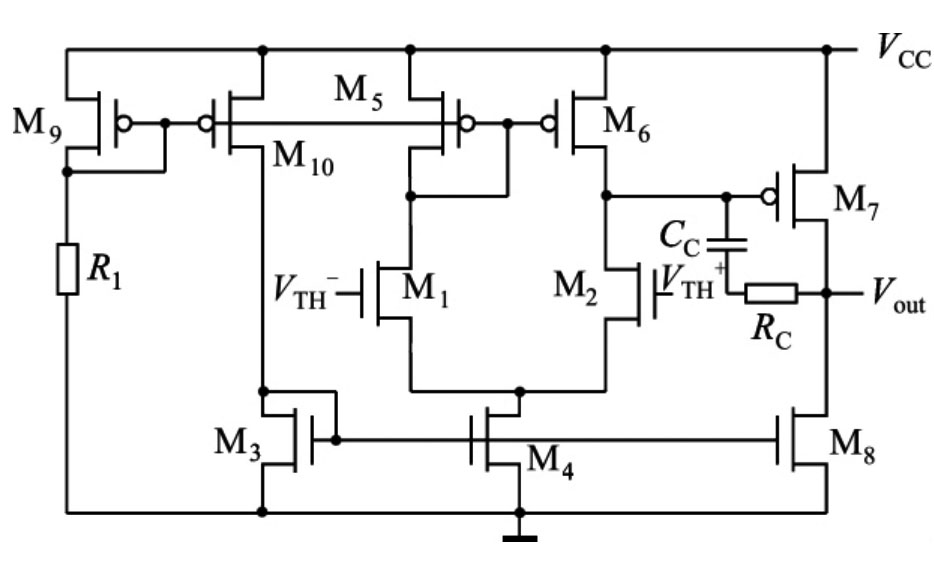

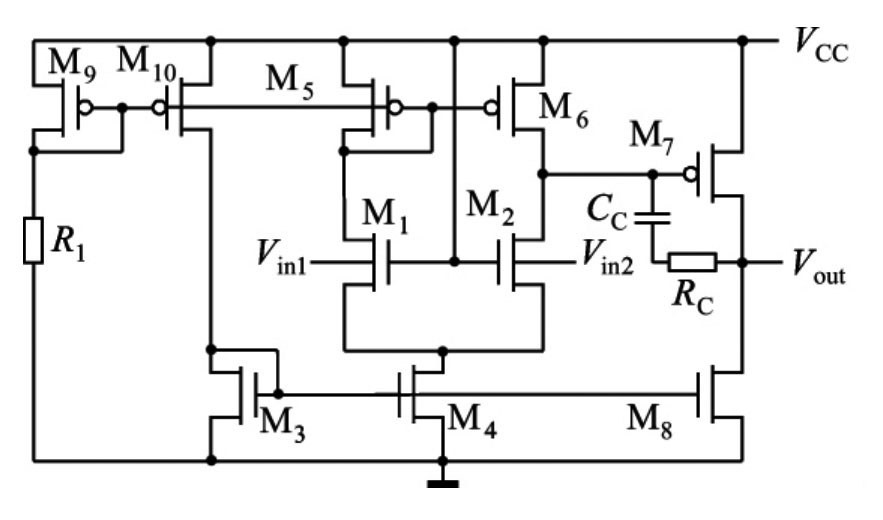

图12-1 NMOS差分输入二级运放的最低工作电压

在CMOS电路中,电路能够工作的最低电压一方面取决于具体的电路结构形式,另一方面则取决于CMOS器件的阈值电压及其过驱动电压。以图12-1所示的NMOS差分输入二级运放为例,从输入差分对的角度出发,最小工作电压至少包含一个VTN与两个NMOS过驱动电压;而从差分输入级的负载角度出发,最小电源电压近似为一个VTP与三个过驱动电压之和。实际的最小工作电压由电路中各支路最小工作电压中的最大值决定。通常,由于PMOS开启电压的绝对数值相比NMOS高,则最小电压由差分对的输出支路决定。若VTP=0.9V,过驱动电压即饱和压降VDS,sat=0.2V,则VCC,min≈1.5V。同样,对于PMOS差分放大器,采用类似的分析可得到近似相同的最小工作电压。

由于MOS管VGS和VDS值与器件的阈值电压和栅过驱动电压有关,因此低压极限值主要决定于所采用具体工艺中的VTH值。在常规情况下,只有降低阈值电压才能降低电路工作电压。当阈值电压减小后,最小电源电压可以持续降低。采用VTH=0.5V的MOS工艺,模拟OP的最小工作电压可降低到1V左右。然而,阈值电压的降低受到器件泄漏电流增大的限制,对于超大规模数字集成系统,静态功耗的限制使VTH无法持续按比例下降。因此,降低电路工作电压需要寻求其他技术路径。

1)亚阈偏置技术

将模拟电路中的MOS管偏置于亚阈工作区,有利于电源电压的适当降低。根据MOS管I-V的强反型模型,当VGS≤VTH时MOS器件关断使电流为零。实际情况则并非如此,即使当VGS略小于VTH时,在一定的VDS电压下MOS管中仍有导通电流,该电流受弱反型沟道区中载流子扩散机制的控制,这种状态就是“亚阈值区导电”。此时,只要VDS>3VT,则输出电流保持恒流所需的VDS饱和电压在常温下降低到80mV以内,同时过驱动电压可降低到-100mV左右。可见,以上两方面的特性使电源电压实现了不同程度的降低。

在器件尺寸较大的微米量级下,MOS管通常偏置于大电流的强反型工作区,且过驱动电压较大,以适合高电压高速模拟系统的应用。而在现代深亚微米级器件尺寸下,电路偏置电流已经降低到低功耗的μA量级甚至更低,偏置电流绝对数值的降低为弱反型漏电流偏置提供了方便。在亚阈值区,VGS低于VTH的最大范围可达到100mV,同时饱和漏电压的降低,使亚阈状态下的MOS电路更适合于低压工作。其低压、低功耗的优点使得这种技术在某些特殊领域,如内置心脏起搏器、BGR设计中得到广泛应用。

亚阈弱反型电路虽然跨导效率gm/IC高,但跨导gm的绝对值低,由此引起电流驱动能力弱、响应速度低、抗噪声干扰能力弱,这是此类电路设计必须解决的技术难题,这也从一个方面限制了该类型模拟电路更广泛的应用。

2)衬底偏置技术

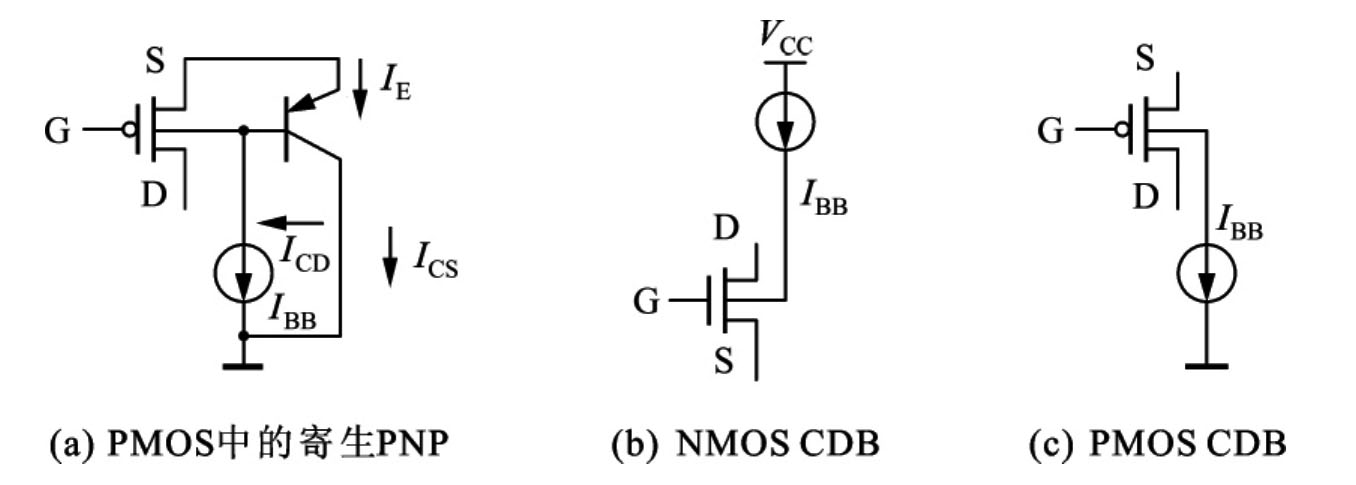

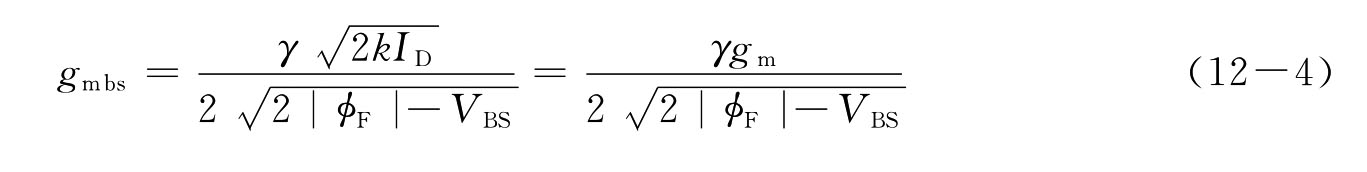

在前文讨论的VTH对电源电压的限制中,VTH通常是指工艺提供的本征VTH0,即没有考虑电路应用中衬底偏置效应对阈值电压的调制作用。MOS管作为一个四端器件,其衬底存在一个压控信号的控制,即衬底偏压会对原有阈值电压产生影响,即

式中:γ——衬偏系数;

φF——体费米势;

VBS——衬底偏压。

可见,电路中MOS器件实际的开启电压VTH是衬底偏压VBS的函数。以NMOS为例,VBS>0的衬底正偏可使VTH下降,而VBS<0的衬底反偏则使VTH增加;对与PMOS同样如此,VBS>0的衬底正偏使VTH的数值下降。在常规的模拟电路设计中,衬底设为零偏或反偏以抑制衬底泄漏电流对系统功耗的影响。反偏引起VTH的增加不利于工作电压的降低。相反,衬底正偏则有利于工作电压的降低。通过衬底偏置电压的极性和大小控制MOS管有效开启电压的技术称为驱动电压衬底Voltage Driven Bulk(VDB)技术。与VDB相对应的是驱动电流衬底CDB技术,通过衬底电流来驱动调制MOS管的有效开启电压。

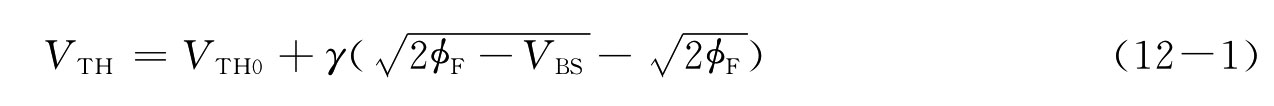

无论NMOS还是PMOS,衬底正偏引起VTH数值的下降将受到衬底泄漏电流的制约。标准CMOS工艺生成的MOS管都存在由源、阱、衬底构成的寄生BJT管。如图12-2(a)所示的PMOS管中,当衬底正偏增大到一定程度后,寄生PNP管的发射结因正偏置而导通,形成的发射极电流IE一部分流入MOS管漏极,另一部分则注入衬底。为了防止泄漏电流超出容许范围,衬底正偏电压不能过高,因此VTH的下降范围有限。由VDB还可推广得到下节重点讨论的背栅驱动低压电路结构。

图12-2 电流模衬底驱动结构示意图

Current Driven Bulk(CDB)结构则克服了VDB中衬底电压驱动的不足,通过强加一个IBB电流流过衬底与源端之间的PN结,以控制最大的衬底正偏电压。在图12-2(b)和(c)的CDB驱动中,控制衬底偏置电流IBB的大小为

式中:βCS、βCD为分别是横向与纵向两个寄生BJT管基极—集电极间的电流增益;Imax为衬底漏电流的上限范围。

已知Imax,可由式(12-2)设计IBB。由于IBB的限流作用,衬底电流被限定在一定的范围内,避免了VDB结构中衬底过流的发生。

CDB技术的优点是无需特殊工艺支持即可获得较低的VTH,使低压Cascode结构应用成为可能。但是,CDB也存在寄生BJT噪声被耦合进电路、MOS管输出阻抗减小等缺陷。

3)浮栅控制技术

浮栅技术(Floating-Gate)在数字电路中已获广泛应用。在标准CMOS工艺下,一个MOS管的栅被分为两个或多个部分,并实现独立控制。初始情况下浮栅电位悬浮,栅下可储存电荷且泄漏缓慢,只有被紫外线照射或高压隧穿控制才能消失。此特性常用于存储器,作为存储信号“1”或“0”的标志。

浮栅技术同样可用于模拟电路的低压设计。设MOS管的栅共分为两块,首先通过紫外线照射使栅下储存的电荷全部泻放,此时对应的原始开启电压为VTH。将MOS管两输入栅中的一个接偏置电压,另一个接输入信号,这时由于栅上的偏置电压不同,则MOS管的VTH就会根据Vb电压的大小调整到一个新的有效开启VTHequ值,即

式中:CT——MOS管总的栅电容;

Cin——接信号的栅电容;

Cb——接偏置的栅电容;

Vb——偏置电压。

图12-3 采用浮栅MOS管的基本单元电路

可见,给出适当的Vb和栅面积划分比例,就可以得到很低的等效阈值电压VTHequ。图12-3为浮栅控制的两个具体应用。与前几种低压技术不同的是,浮栅技术需要特殊工艺的支持,而且由于有效栅面积的减小,其单位面积有效跨导也相应减小。

因此,降低电源电压,既可从工艺的角度出发,也可以从设计的角度出发,通常是结合工艺与设计两方面来实现电路结构的低压工作。

12.2.2 低压单元结构的性能改善

当电路在低压下能够正常工作时,还需要考虑低压电路性能的改善。由于电源电压降低给数字电路带来的好处远远胜于模拟电路,因此必须通过有效的设计来抑制低压模拟电路性能的退化。对低压模拟电路性能的限制主要表现在I/O摆幅减小和增益下降。以下各种结构设计主要针对这两方面性能的改善。

1)低压宽摆幅电流镜

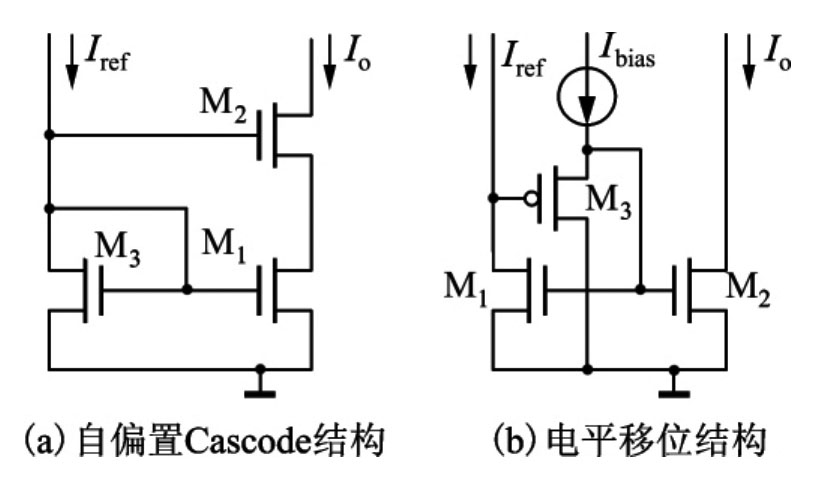

信号处理中除动态范围外,足够大的增益同样重要。由于低压电路中常规Cascode这种高增益结构难以使用,只有采用适合低压的高阻电流镜。自偏置Cascode和电平移位(Level-Shift)结构可在一定程度上缓解传统结构的不足,并用于低压电流镜结构中的高阻负载。

Self-Cascode结构是通过增大负载阻抗以提高增益,此外还可采用横向级联的方式获得高增益。Cascode是一种VCC到GND垂直方向的级联,受电源电压、摆幅影响巨大。而级联多级运放,则是横向级联,受电源电压影响小,但系统稳定性要求将级联的数目限定在一定范围内。

忽略过驱动电压的影响,普通Cascode电流镜在电流输入侧至少需消耗两个阈值电压,而在图12-4(a)的自偏置Cascode 1∶1线性电流镜中,电流的输入端由于删除了一个MOS管,因而仅消耗一个阈值电压,而在电流输出一侧仍为两个共栅MOS管。为保持输出一侧的高阻抗,M1管需工作在临界饱和区。此时,由于M1管饱和电压所消耗掉的是过驱动电压,则M2管的过驱动电压近似为零,M2管便进入临界亚阈值工作区。为维持M1和M3管相同静态电流的线性传递性质,需适当提高M2管的W/L。实际上,M2管的W/L越大,M1管的饱和工作条件越充分,M1管的输出电阻越接近其最大值。由于M2管进入临界亚阈值区,在同样的电流偏置下gm2跨导增加,更有利于输出阻抗的提高。显然,Self-Cascode电流镜以增加大M2管面积以及结构参数设计的复杂化为代价,换取了低压电路性能的提高。

图12-4 低压电流镜单元电路

常规电流镜的电流输入由于采用MOS二极管结构,消耗至少一个阈值电压。图12-4(b)中的电平移位电流镜结构,由于采用电平移位技术,可适当降低输入一侧的漏电压。设NMOS管的栅压为VGSN,而PMOS偏置电流驱动的栅源电压为VGSP,根据图中电流镜及偏置的连接关系,M1输入管的VDS1=VGSNVGSP,即电流输入侧需消耗NMOS管与PMOS管阈值电压值的差。该结构要求VGSN>VGSP,此时应有VTN>VTP。对于常规CMOS工艺,通常VTP的绝对数值比VTN略大,无法满足以上要求,此时需要提高NMOS管的过驱动电压,因此适合大电流的线性传输,同时需降低PMOS管的过驱动电压,即针对PMOS采用亚阈偏置或衬底正偏控制。与此相对应,PMOS电流镜采用NMOS的电平移位,输入端实现的VDSP=VGSP-VTN,由于VTP>VTN,所以可适合低电流驱动的线性电流镜结构。

以上控制技巧不仅可用在低压线性电流镜电路设计中,还可以在当电路中需要降低或抬升某一点的直流电平时,能用另一种互补类型的MOS管进行电平移位,只是其代价需多消耗一个支路的偏置电流。

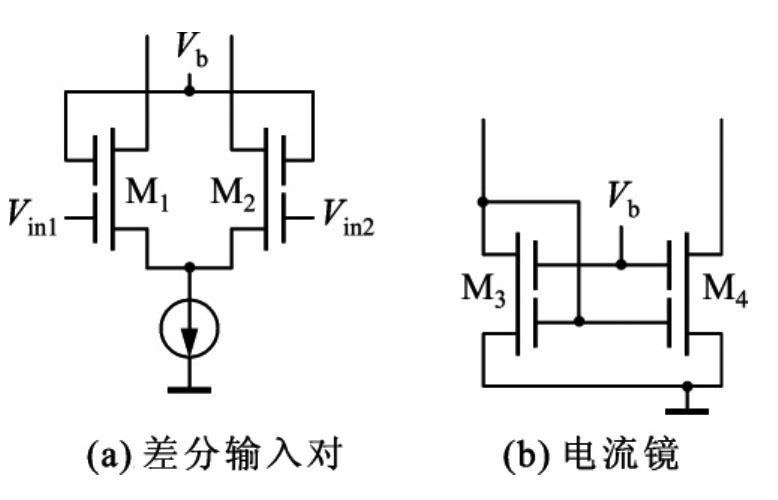

2)衬底驱动(Bulk-Driven)低压运放

在电路系统中,如果存在数字与模拟信号的传递时,必然要求较宽的输入共模电压范围ICMR(Input Common Mode Range),而且该共模范围要尽量位于电源的中间区域,以使小信号放大过程中的非线性失真降到最低。以NMOS电流镜作负载的PMOS差分输入单元为例,输入共模电压范围VICMR=Vin(max)-Vin(min)=VCC-VTN-|VTP|-3VDS,sat。假设VCC=1.4V,VDS,sat=0.1V,VTN=0.5V,VTP=-0.6V,可见VICMR几乎为零。因此,低电源驱动下的ICMR范围扩展需要采用非同常规的电路结构。

四端口MOS器件在电路中的应用,通常是PMOS管衬底接最高电位VCC,NMOS管衬底接最低电位GND,以确保衬底零偏或反偏,而输入信号则从栅端接入。在特殊的Bulk-Driven应用中,其输入驱动电压的设置与常规应用完全相反,当PMOS其栅接GND,NMOS栅接VCC,则器件始终导通,而信号输入则接衬底驱动,通过衬底效应调制开启电压的大小以改变输出电流。

以反相驱动的PMOS放大管为例,输入信号的变化将导致PMOS衬底与源端形成的PN结反偏或正偏,PN结反偏将使耗尽层展宽,沟道表面可移动电荷数减少,即源漏电流减小。如果反偏达到一定程度,加宽的耗尽层能够夹断导电沟道。同理一定程度的正偏将减小耗尽层宽度,从而增大输出电流和衬底跨导,正偏的限度为衬底漏电流相对于源漏沟道电流可以忽略不计。既可正偏又可反偏的输入驱动方式使衬底输入端的变化范围增大。反偏时输入可高于其源端电位直至VCC以上,正偏时输入也可低于源端一个PN结导通电压Vd内的限定范围。同样对于NMOS,反偏时输入端可以低于其源端电位直至GND以下,正偏时输入也可以在高于源端一个Vd导通电压以内的限定范围。

衬底驱动输入信号与栅驱动的效果基本相同,将衬偏调制的开启电压代入源漏电流关系中,得到的背栅跨导为

式中:VBS体现了输入信号的调制作用,而VGS则成为传统意义上的固定偏置电压。

一个具体应用实例,就是将图12-1的VBD结构改成Bulk-Driven输入形式,如图12-5所示。在此条件下,ICMR约为GND到VDS,sat+Vd的范围,在低电源电压VCC驱动下,若VCC≈VDS,sat+Vd,则ICMR近似为满电源量程输入摆幅。

图12-5 输入端采用衬底驱动技术的二级运放

Bulk-Driven技术虽然对改善电路的ICMR性能非常有效,但同时也存在明显的缺陷。首先是噪声较大,大量的衬底噪声将与输入信号一起耦合进电路,信号对噪声更为敏感;其次由于衬底寄生效应的存在使输入电容增大,电路的频率特性受到严重影响。因此,衬底输入型驱动放大电路的应用,有待于工艺和设计水平的发展与提高。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。