6.4.2 连续3层成膜

我们下面分别来讨论。

1.低速a-Si膜厚的影响

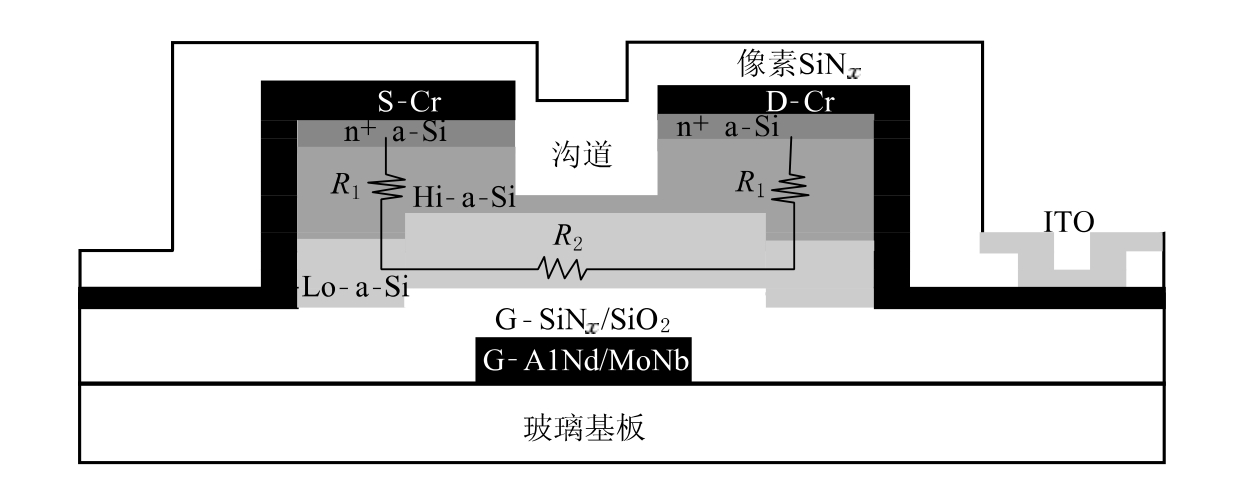

图6.19所示是TFT器件的精细结构。栅极由铝钕/钼铌/MoNb两层合金膜组成,栅极上面的绝缘层由二氧化硅和氮化硅组成,而非晶硅层则由低速非晶硅(Lo-a-Si)、高速非晶硅(Hi-a-Si)和重掺杂n+非晶硅(n+a-Si)组成。然后是金属电极源极和漏极、像素保护层氮化硅和像素电极ITO,像素电极ITO要在像素保护层氮化硅上打一个孔和漏极接触。

图6.19 TFT器件的精细结构

低速a-Si层结构致密是导电的主要通道,随着它的厚度增加,导电沟道变宽,电阻R2变小,电子迁移率变大,电流整体上升。导致开态电流变大,对TFT开态性能有帮助,同时关态电流也变大,即像素电压保持阶段产生较大的漏电流,可能引起显示不均,即所谓的L姆拉(Mura)。这种姆拉随Vg-off电压绝对值变小,表现更加明显。使器件质量变坏。

同时低速a-Si层成膜很慢,还需要考虑到工艺节拍的问题,需要设计合理的低速a-Si层的厚度,一般控制在300~600 比较合适。

比较合适。

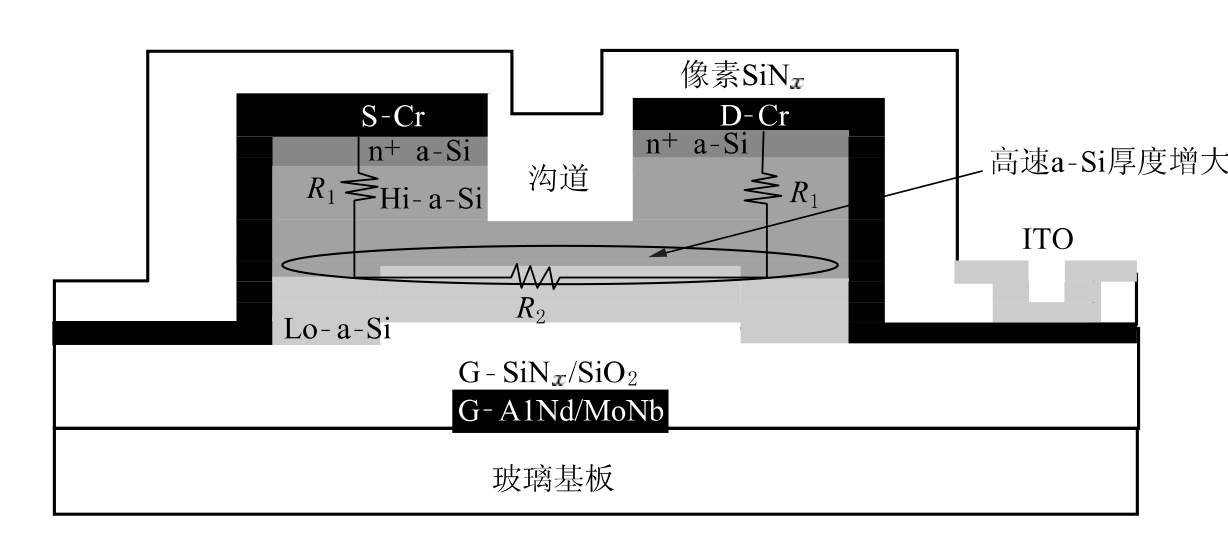

2.高速a-Si厚度的影响

高速a-Si层膜的致密性较差,电阻也比低速a-Si大,所以它的厚度变大之后,沟道两侧的电阻也变大,沟道电流变小。虽然高速a-Si成膜速度比较快,但是如果不适当地增加它的厚度,将会影响TFT的特性,如图6.20所示。一般高速a-Si层膜的厚度控制在2 000比较合适。如果太薄,会给刻蚀带来影响,容易出现过刻蚀。

图6.20 高速a-Si层厚度影响TFT电流

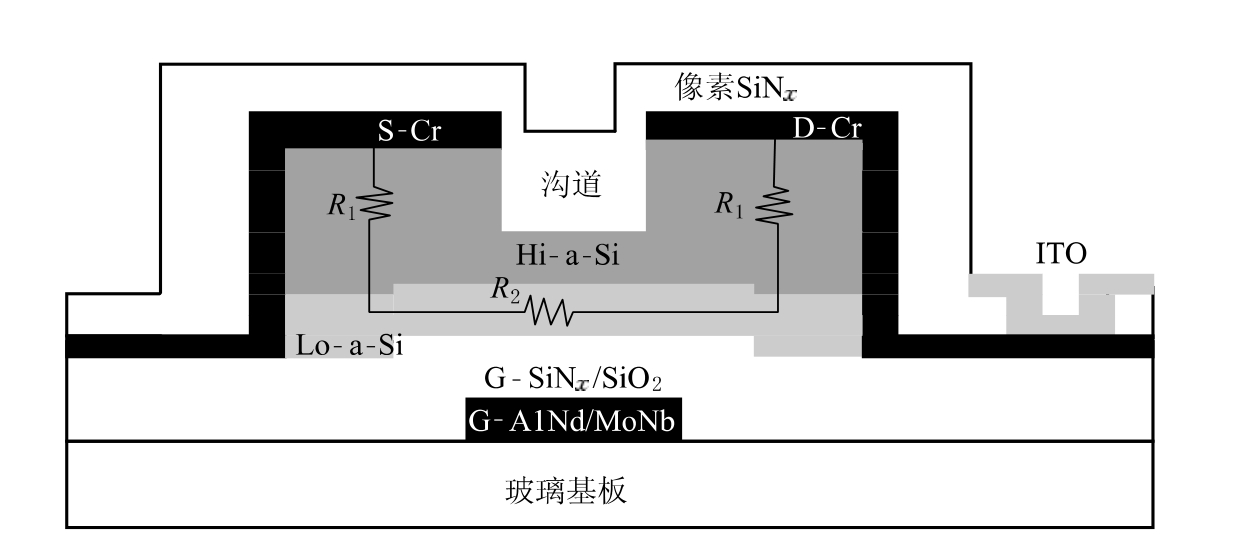

3.n+a-Si层的影响

如果没有n+a-Si层,如图6.21所示,则漏极层/源极层与非晶硅之间为肖特基接触,电阻R1非常大,出现了很高的势垒,电子需要很高的能量才能越过这个势垒,这是非常困难的,于是造成电流急剧下降,使信号写入不足,在器件特性上表现为K姆拉。在加上了n+a-Si层之后,层间接触接成为近欧姆接触,势垒基本可以忽略,TFT的电流特性得到改善。n+a-Si层的厚度一般控制在300左右。

图6.21 没有n+a-Si层的TFT结构

4.PA-CVD前高温放置的影响

随着高温放置时间的增加,Si—H中的H脱离,膜质偏于绝缘体,电流下降,TFT电流特性比较差。

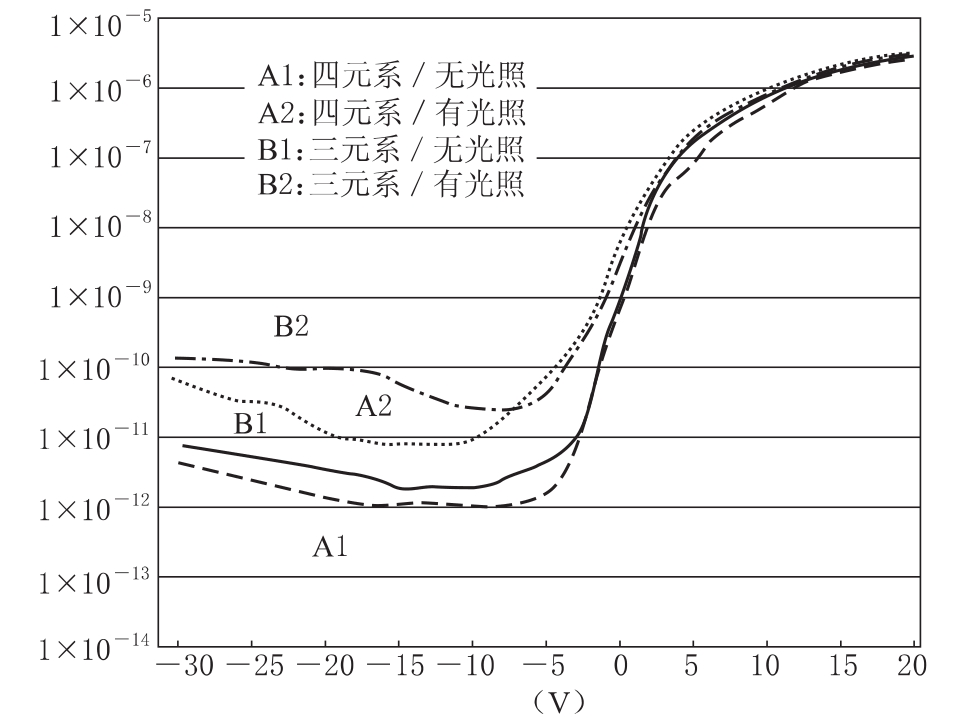

5.G-SiN成膜采用三元系的影响

TFT栅极绝缘层可以采用硅烷、氨气、氮气(N—H/Si—H=3)三元系材料合成,也可以采用硅烷、氨气、氮气、氢气(N—H/Si—H=1)四元系材料合成。

采用三元系之后,膜质氨化,向半导体方向发展,电流上升。关态电流上升的比较明显,如图6.22所示,容易导致L姆拉。

6.氢气等离子体的影响

假如不使用氢气等离子体,在沟道表面会有残留的氟,在关态时这些氟离子会在外加电场作用下定向移动,形成电流。这也是背沟效应的一种。所以需要在CVD工艺中使用氢气等离子体,在干刻工艺中使用氧等离子体,除去这些杂质。除了以上原因,出现背沟效应还可能是由于液晶中含有的钾、钠等离子产生了定向移动,这个问题在阵列部分很难解决。

图6.22 采用三元系关态电流明显上升

7.G-SiN膜厚的影响

随着G-SiN膜厚增加,吸出电子能力变强,TFT特性曲线变好。考虑到制作节拍的因素,G-SiN膜不宜太厚,一般控制在2 000~4 000。

通过上面的讨论,可归结如下:

●低速a-Si膜厚增加时,整个TFT电流上升。

●高速a-Si膜厚增加时,整个TFT电流下降。

●n+a-Si层不存在或接触不好时,电流值急剧下降,TFT表现为一种断路。

●在像素电极-氮化硅层成膜前不进行氢气等离子体处理,关态电流上升。

●在栅极-氮化硅成膜中不加入氢气,电流值上升,关态特性变差。

●在像素-氮化硅层成膜前高温放置,电流值下降,开态电流下降较明显,开态变差。

●栅极-氮化硅膜厚增加时,整个TFT电流下降,尤其是开态电流。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。