10.4 不同抽象级别的Verilog HDL模型

Verilog HDL是一种用于逻辑电路设计的硬件描述语言。用Verilog HDL描述的电路称为该设计电路的Verilog HDL模型。

Verilog HDL具有行为描述和结构描述功能。行为描述是对设计电路的逻辑功能的描述,故不用关心设计电路使用哪些元件及这些元件之间的连接关系。行为描述属于高层次的描述方法,在Verilog HDL中,行为描述包括系统级(system level)、算法级(algorithm level)和寄存器传输级(register transfer level,RTL)等三种抽象级别。

结构描述是对设计电路的结构进行描述,即描述设计电路使用的元件及这些元件之间的连接关系。结构描述属于低层次的描述方法,在Verilog HDL中,结构描述包括门级(gate level)和开关级(switch level)两种抽象级别。

在Verilog HDL的学习中,应重点掌握高层次的描述方法,但门级描述在一些电路设计中也有一定的实际意义。

10.4.1 Verilog HDL门级描述

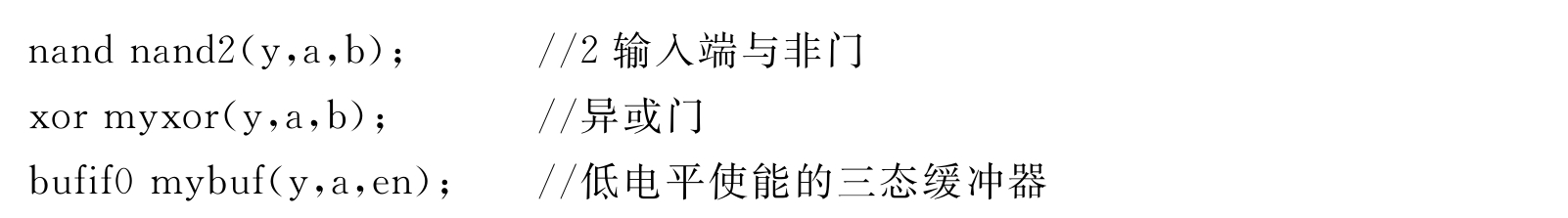

用于门级描述的关键字包括NOT(非门)、AND(与门)、NAND(与非门)、OR(或门)、NOR(或非门)、XOR(异或门)、XNOR(异或非门)、BUF(缓冲器),以及BUFIF1、BUFIF0、NOTIF1、NOTIF0等各种三态门。

门级描述语句的格式为

门类型关键字<例化门的名称>(端口列表);

其中:“例化门的名称”是用户定义的标识符,属于可选项;端口列表按输出、输入、使能控

制端的顺序列出。

例如:

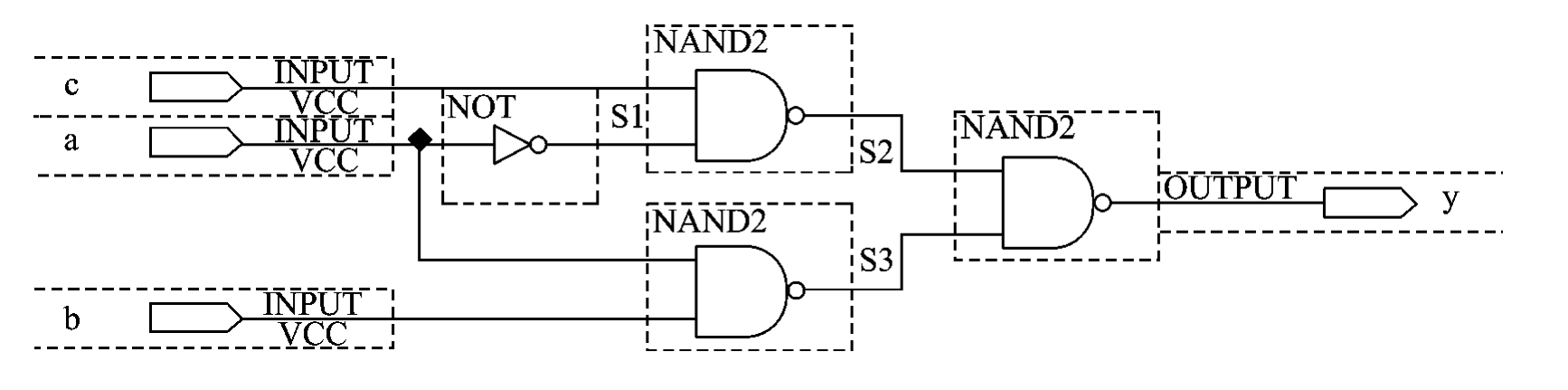

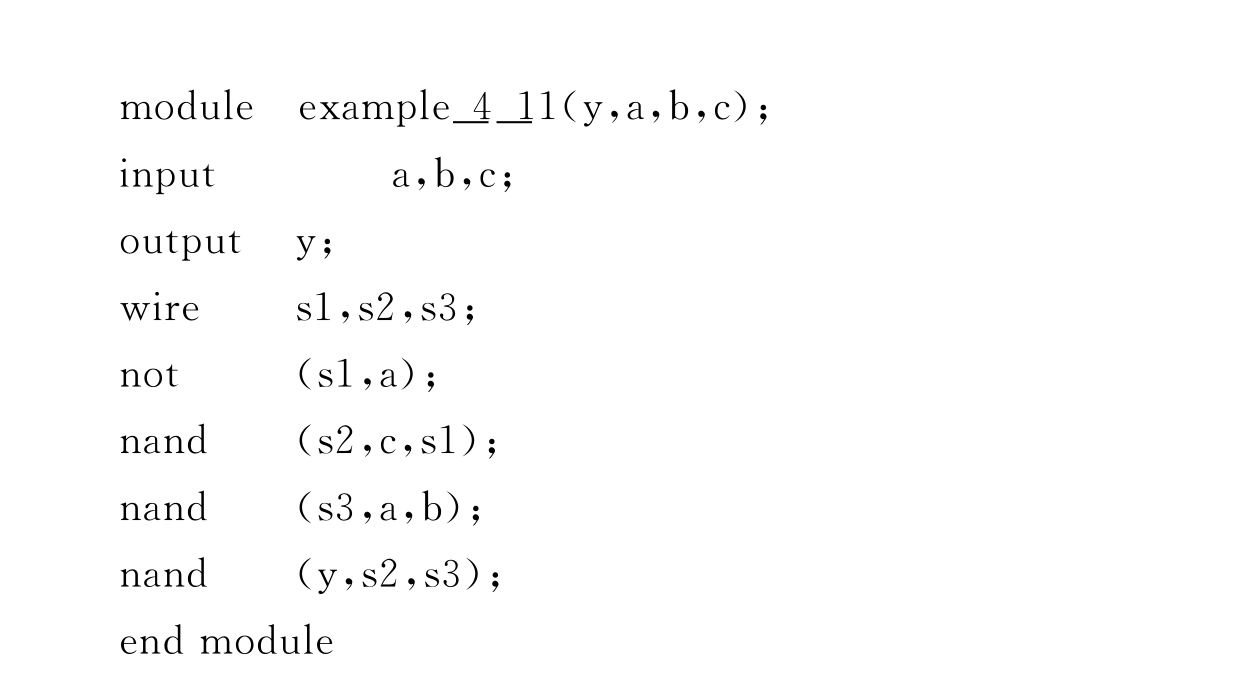

【例10.4.1】 采用结构描述方式描述图10.4.1所示的硬件电路。

图10.4.1 硬件电路

10.4.2 Verilog HDL的行为级描述

Verilog HDL的行为级描述是最能体现EDA风格的硬件描述方式,它既可以描述简单的逻辑门,也可以描述复杂的数字系统乃至微处理器;既可以描述组合逻辑电路,也可以描述时序逻辑电路。

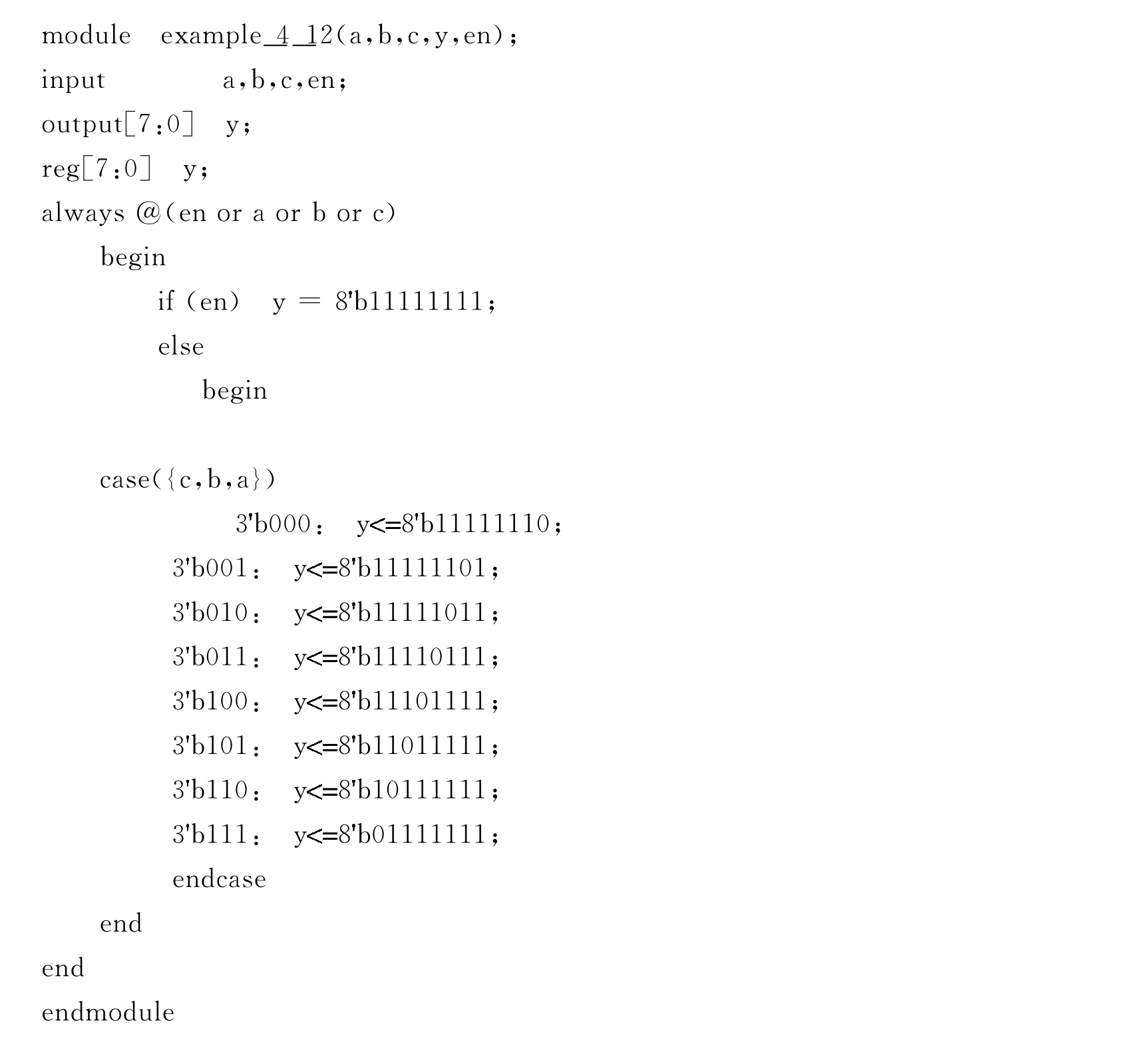

【例10.4.2】 3-8线译码器的设计。

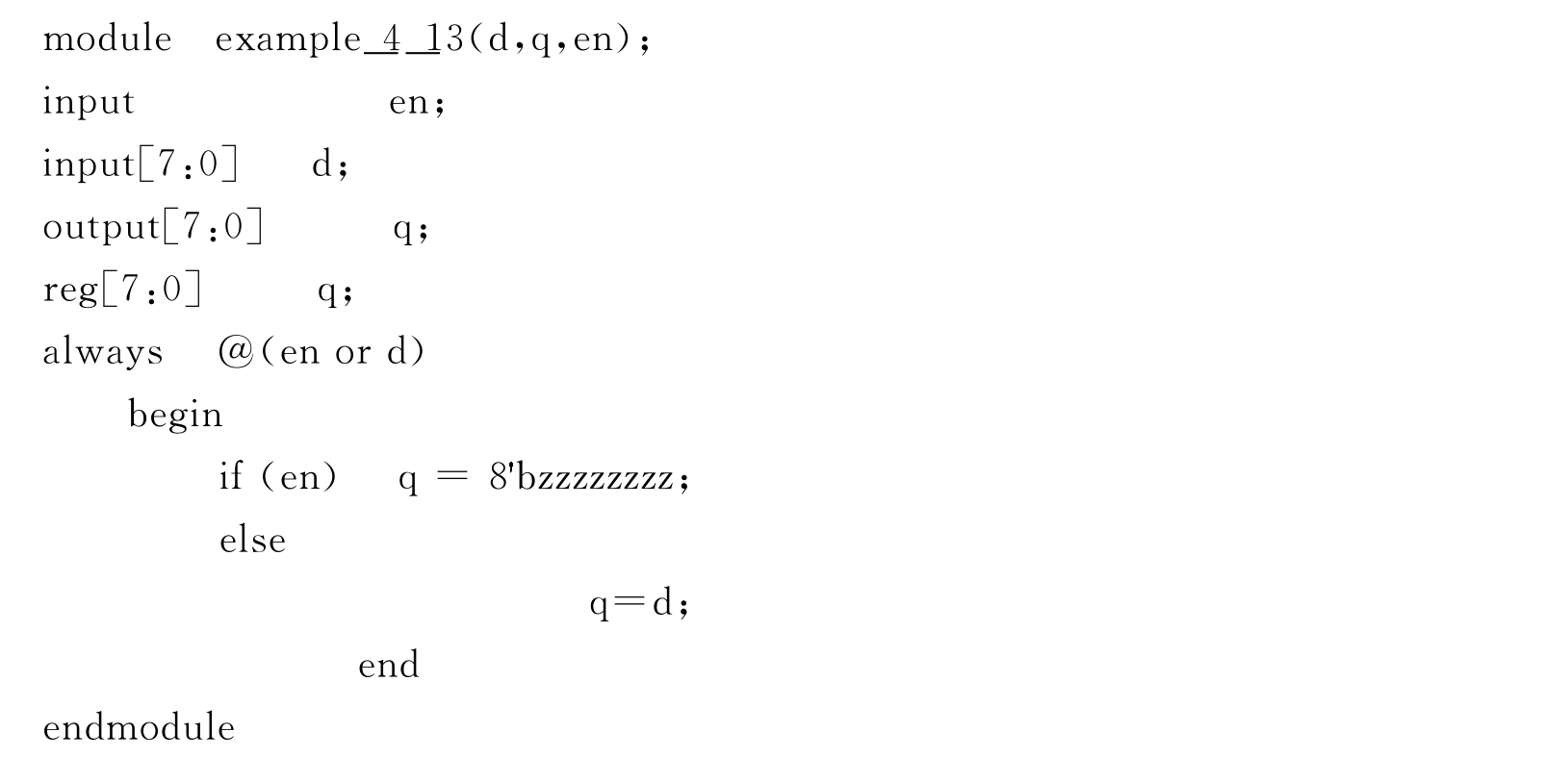

【例10.4.3】 8D锁存器的设计。

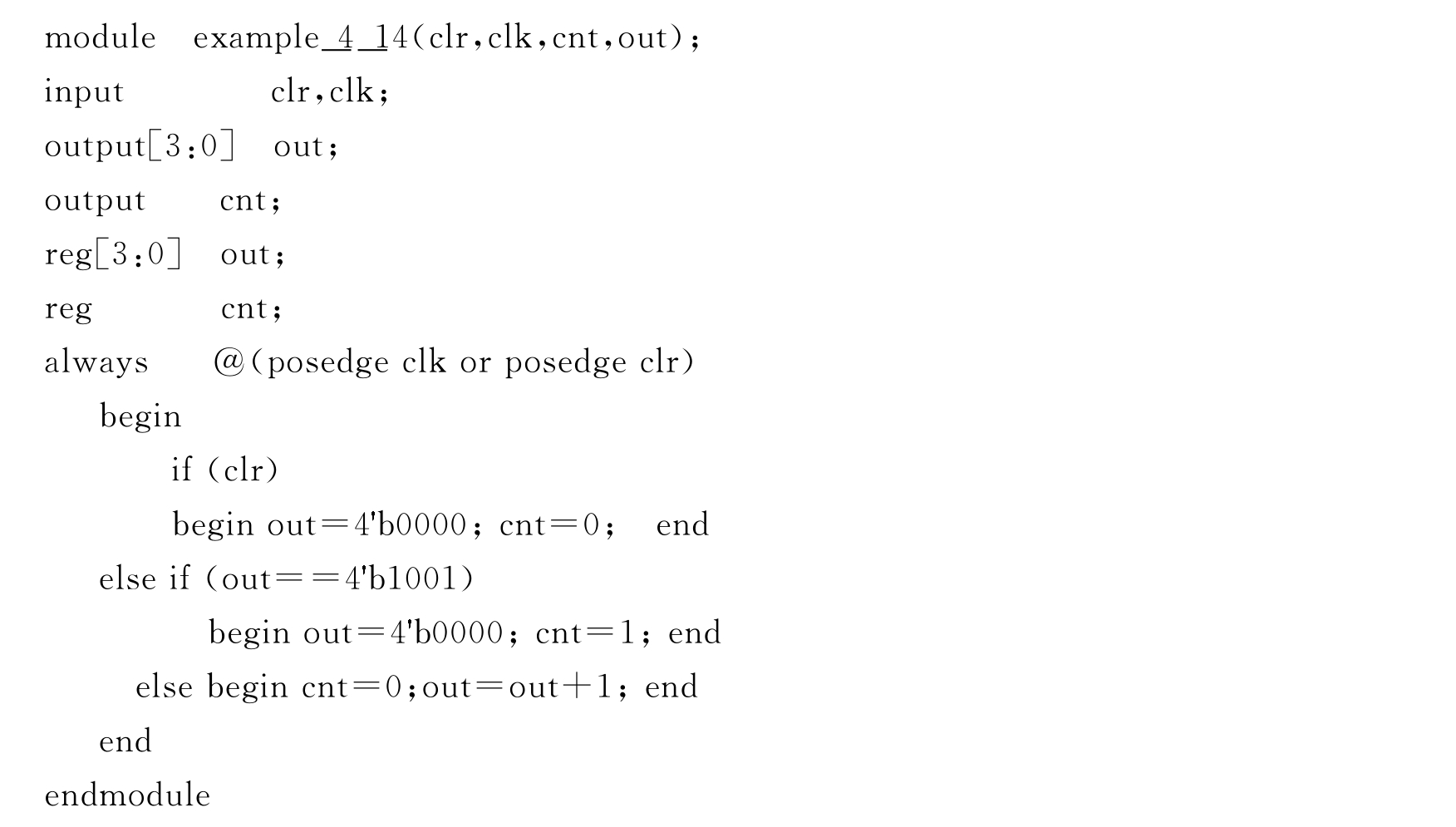

【例10.4.4】 异步清除十进制加法计数器的设计。

10.4.3 用结构描述实现电路系统设计

用Verilog HDL描述的电路设计模块均可用模块例化语句例化一个元件,来实现电路系统的设计。

模块例化语句格式与逻辑门例化语句格式相同,具体如下。

设计模块名<例化电路名>(端口列表);

其中,“例化电路名”是用户为系统设计定义的标识符,相当于系统电路板上用来插入设计模块元件的插座,而端口列表相当于插座上的引脚名表,应与设计模块的输入/输出端口一一对应。

【例10.4.5】 用模块例化方式设计8位计数译码器电路系统。

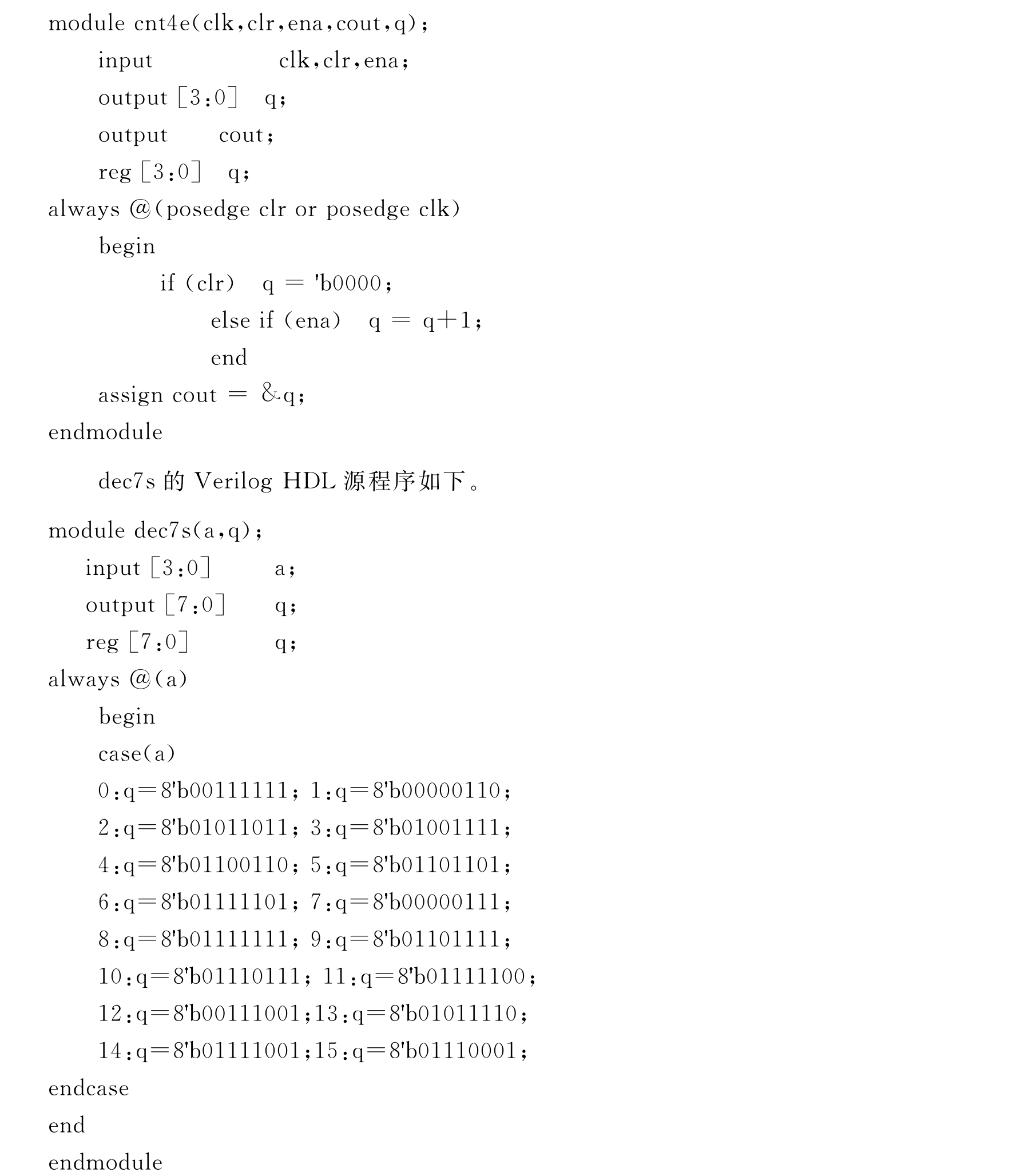

第一步:设计一个4位二进制加法计数器cnt4e模块和一个7段数码显示器的译码器dec7s模块。

cnt4e的Verilog HDL源程序如下。

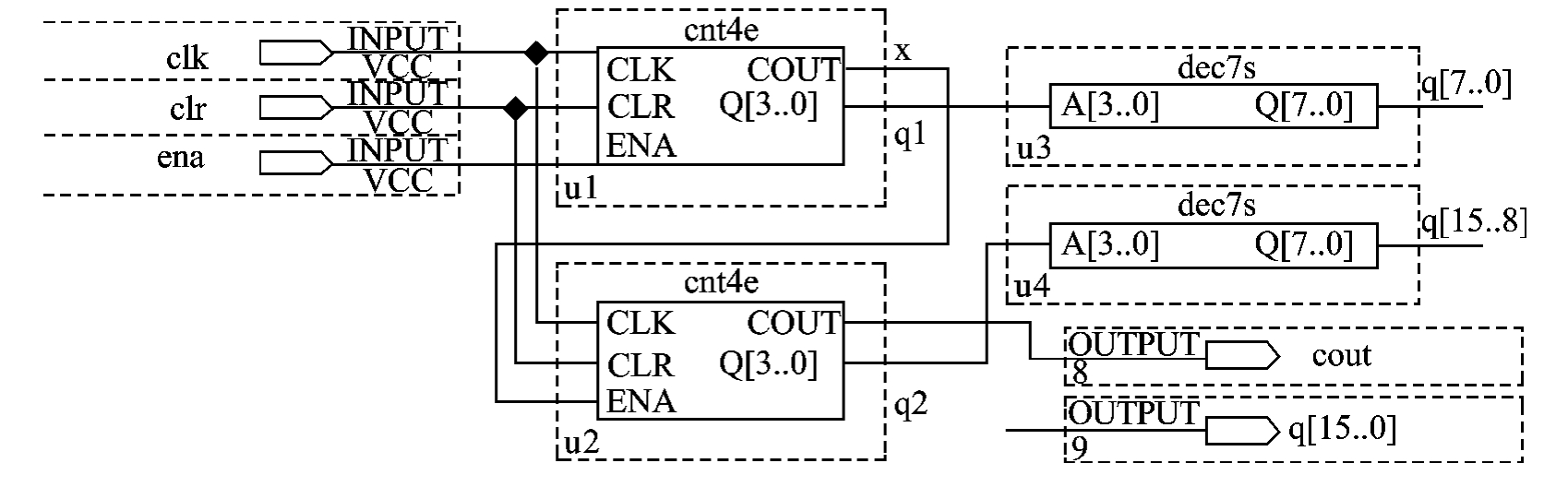

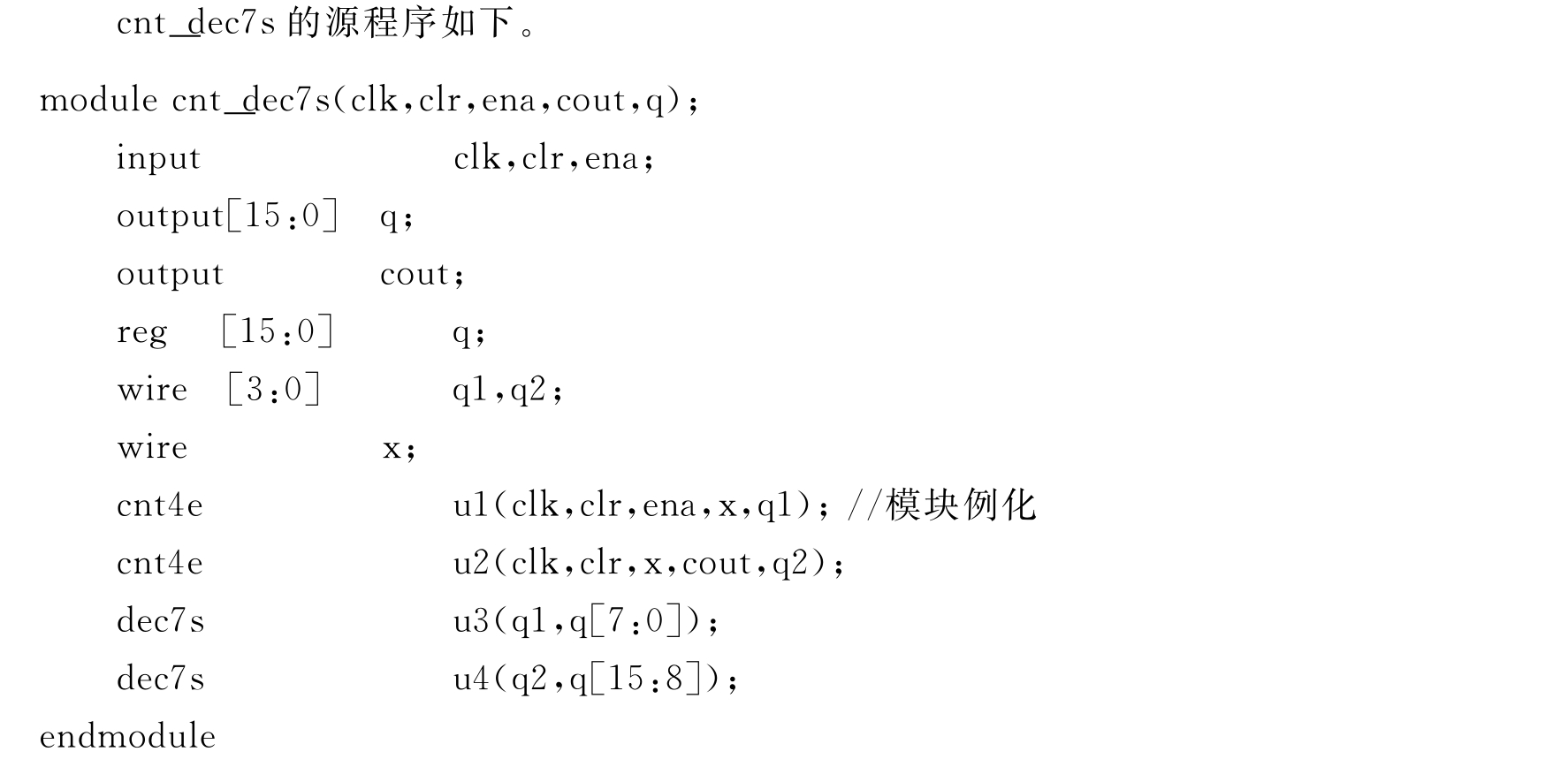

第二步:设计计数译码系统电路。计数译码系统电路的结构图如图10.4.2所示。其中:u1和u2是两个cnt4e元件的例化模块名,相当于cnt4e系统电路板上的插座;u3和u4是dec7s元件的例化模块名,相当于dec7s在系统电路板上的插座;x、q1、q2是电路中的连线。

图10.4.2 计数译码系统电路的结构图

Verilog HDL设计流程与前面章节叙述的VHDL设计流程基本相同,这里不再重复。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。