4.4.4 动态RAM的刷新

1.刷新周期位置的安排

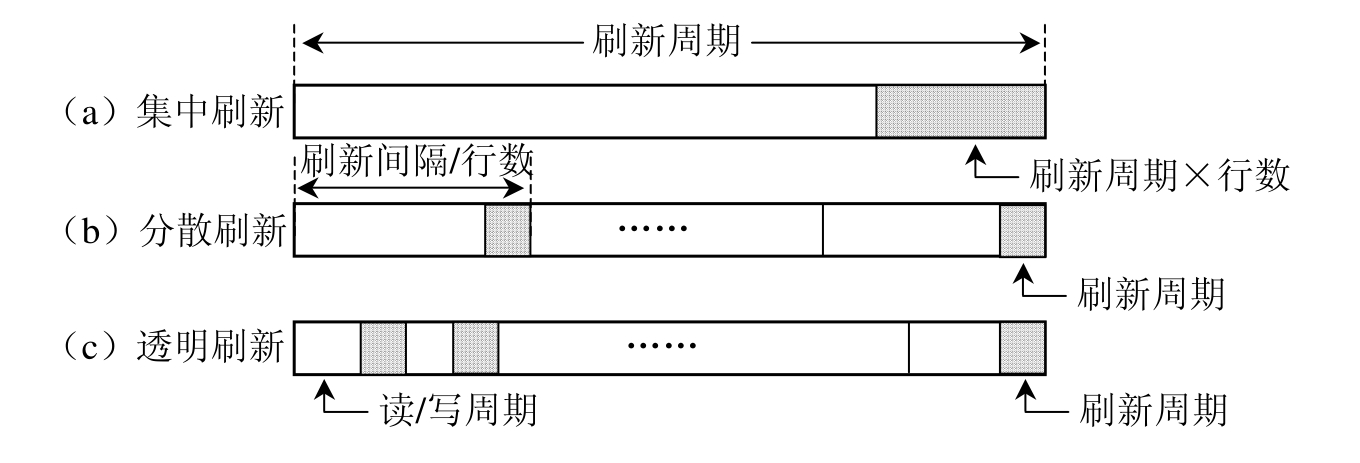

动态RAM需要周期地进行刷新操作,刷新通常是以行为单位进行。每刷新一行的时间称为刷新周期。在一定的时间内需要将存储芯片内的所有行都刷新一遍,某一行本次刷新到下一次刷新的时间称为刷新间隔,刷新间隔小于2 ms。按照刷新周期的位置分配不同而不同,有三种方式,如图4.14所示。

(1)集中刷新在每一个刷新间隔的时间内,前一段进行正常的读/写操作,后面集中进行所有行的刷新。在刷新期间CPU不能进行总线操作,因为地址线被占用。

(2)分散刷新将刷新间隔平分(除以行数),每个时间段执行一次刷新(刷新一行)。这种方式可避免CPU连续长时间的等待,其用于刷新的总的时间开销和集中刷新一样。目前,微机中的DRAM刷新就采用这种方式。

(3)透明刷新周期安排在CPU进行某种内部操作、访问存储器所用的总线处于空闲的时间进行。这也是一种分散刷新,但不占用CPU时间。

图4.14 动态RAM刷新周期安排

2.刷新控制器

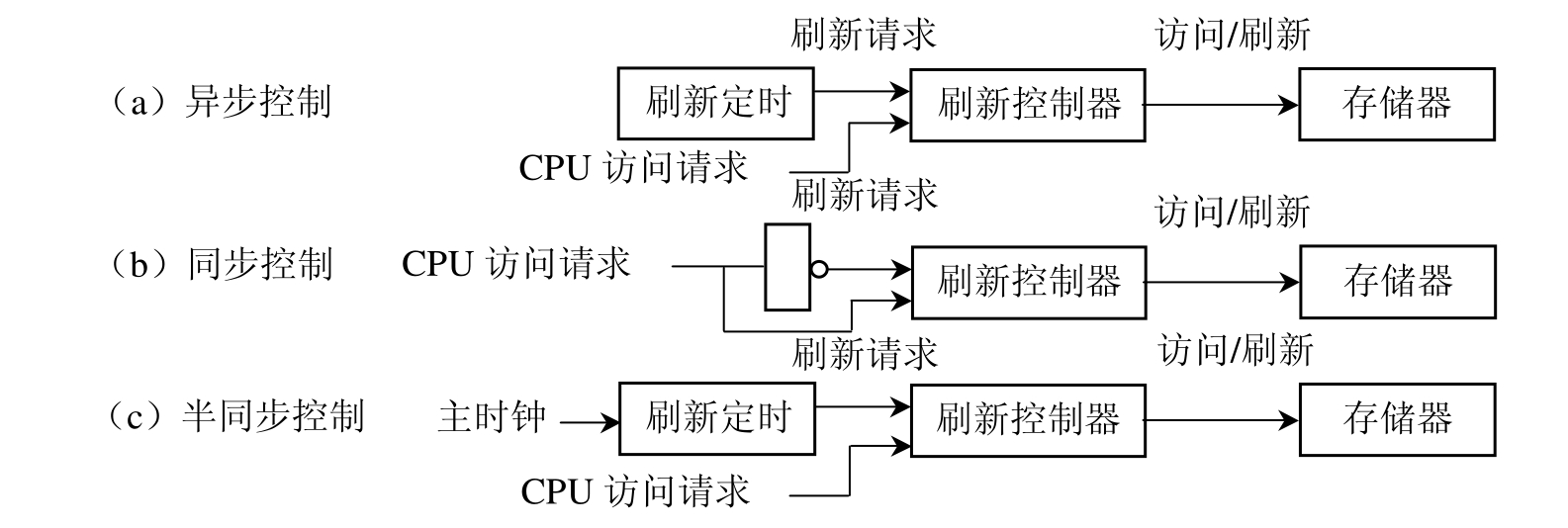

刷新和CPU访问存储器有时会发生冲突,这需要用刷新控制器来协调。刷新控制器的控制方式通常有三种,如图4.15所示。

(1)异步控制方式 CPU访问存储器的请求和刷新请求相互独立,刷新控制器以“先入为主”的原则为它们服务,当二者同时请求时,以刷新优先,因为不及时刷新将会导致信息丢失。用这种方式,CPU应允许等待。在当前的微机中,就采用了这种刷新控制。

(2)同步控制方式刷新请求是CPU访问的“非”,即CPU不访问存储器的时间进行刷新。显然,这种方式要求CPU应有确定的不访问存储器的时间,以保证刷新的周期性。

图4.15 刷新控制方式

(3)半同步控制方式建立一个时钟信号,用时钟信号的上升沿、下降沿来同步CPU的访问和刷新。例如,用同步时钟的上升沿同步CPU的访问。所谓同步,是指CPU访问存储器的请求在时间上可以是随机的,但是必须等待时钟的上升沿到来,才能访问存储器,而时钟的下降沿则进行存储器的刷新。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。