1.3 第二个验证平台

前面的例子采用一个组合逻辑设计(一个与门),说明了基本的验证概念。很自然,组合逻辑设计并不固定在某一个状态上。在我们的第二个例子中,我们看一个稍微复杂的设计,它能够维持其状态并用了一个时钟去触发状态之间的变换。

与同步时序设计相关的验证问题和组合逻辑相比还是有些差异。对于组合逻辑你需要知道的就是它的每个输入管脚。针对组合逻辑的参考模型只需要计算f(x),其中x表示这个器件的输入,而 f 是这个函数的实现。一个时序器件的输出是它的输入和内部状态的一个函数。进一步的运算可能会改变内部的状态。记分板必须记录DUT的内部状态和比较其输出。

组合逻辑可以通过穷举的方法来验证,通过执行所有可能的输入。对于一个带有N个输入管脚的器件,我们必须采用2N个输入向量。2N个可能是很大一个数目,但是提供这些输入是很容易的。我们只需要一个N比特的计数器,并把计数器的每个数值作为器件的输入。

对于时序器件,验证完成就是指不仅全部覆盖所有可能的输入,而且所有可能的内部状态。对于一个有N个输入、M个内部状态的器件,你必须覆盖2N(输入)×2M(状态),也就是2N+M个内部状态和输入管脚的组合。对于64个输入管脚的和一个32比特内部寄存器的器件,这个状态和输入组合将是296,一个相当巨大的数字!

即使对于非常大的组合数目,如果能够简单地用一个增量的计数器来获得所有的组合,这个验证问题也不会太难。很不幸,这是很难实现的。内部状态是不可以在器件外部直接操作的。只能通过操作输入管脚来实现状态的改变。现在的问题就变成了,如何通过操作输入管脚来获得器件的所有状态。这是一个很有难度的问题而且需要对器件要有深入的了解,才可以生成足够的输入序列,得到所有的内部状态。

既然很难得到所有的状态,这个问题明显地变成了,“我们可否通过减少我们需要得到的状态数目,同样可以证明器件也能正常工作,从而把这个问题简单化?”答案是肯定的。现在问题变成了:“我们如何确定哪个状态可以不需要测试?”。

这个话题就比较复杂了,而且对此处理方法也超出了本书讨论的范围。但是我们可以给出一个直接的回答。通过形式验证或者其他技术,仍不可能达到的状态是可以不测试的。设计者应该思考简化设计,从而去除不必要的或不可达到状态,因为它们没有什么作用。出现概率比较小的状态也可以从验证计划中划去。确定概率的限度并给每个状态分配一定的概率也是像科学一般的需要一定的技术,其中包括了对设计使用和期望输入的理解。

消除功能等同的状态也是可行,就如前面提到的基于数据包通信器件。理论上,每个通过设计的,可能出现数据包的净荷表示了一个独立的状态(或者是一系列状态),它都应该在验证的过程中覆盖到。然而,认为任何一个非零的净荷对于设计期望来说都是等价的,这或许是可以接受的。当然,其中可能出现一些边界情况可能需要检查的就如全“0”和全“1”,可能影响纠错检查算法的特殊值等等。

对于复杂的时序逻辑设计,确定一下哪个状态需要覆盖(哪个状态不需要)并且如何以最小的代价去覆盖这些状态就是需要解决的问题,这也是验证工程师获得工作的重要原因。在这一节我们将考虑一个较小的、内部状态可以容易被覆盖的时序器件。

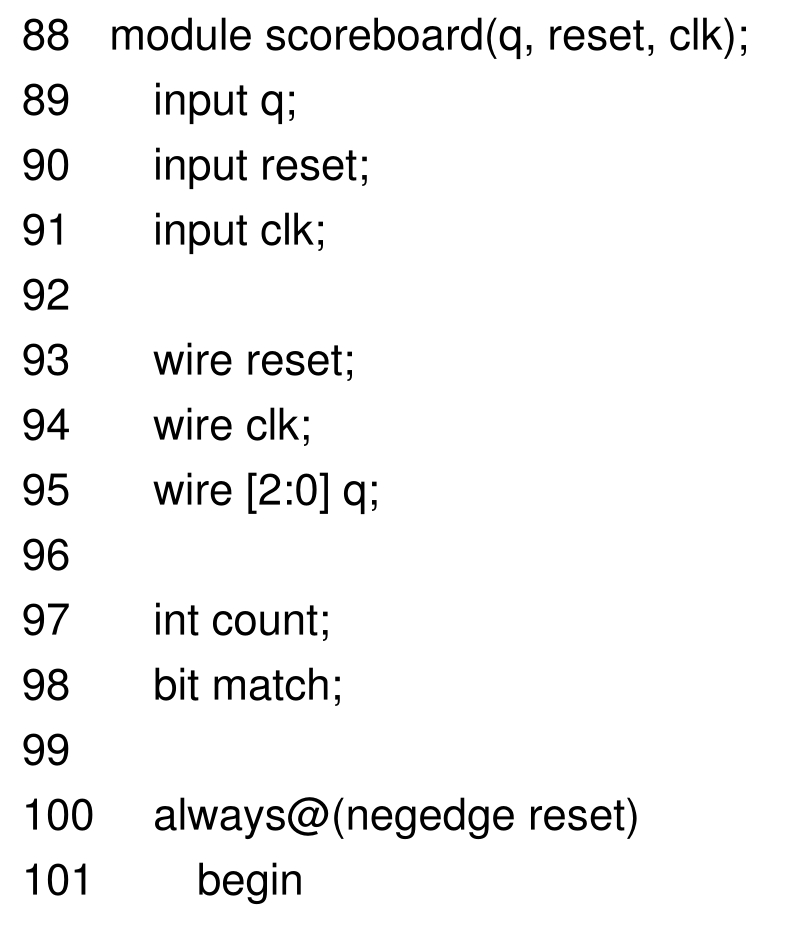

3位计数器

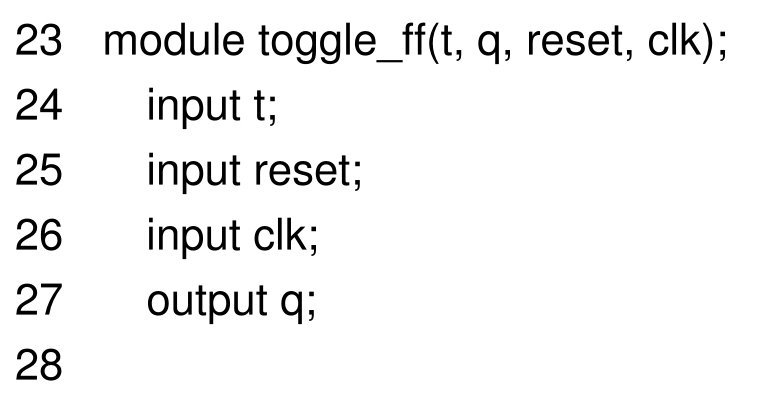

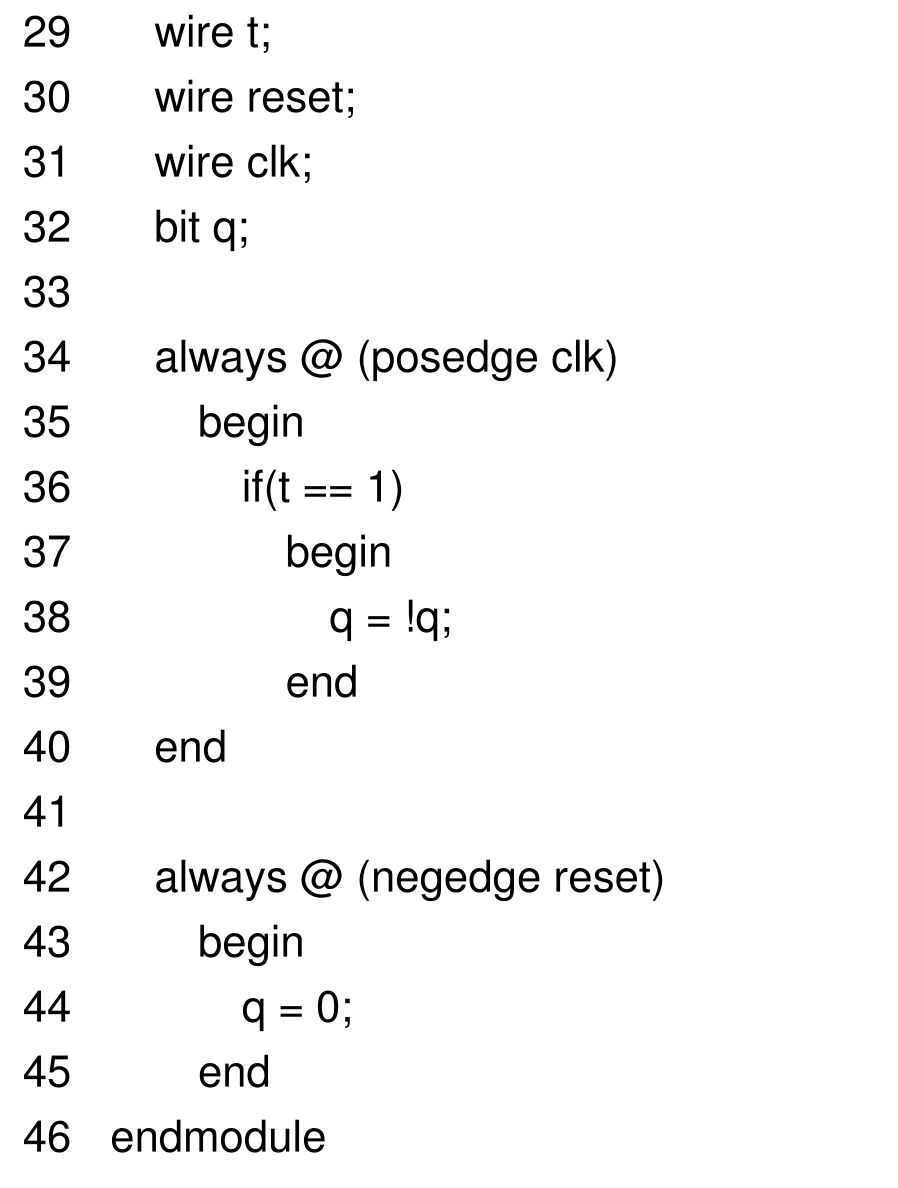

图1-5所示的设计,是一个3比特的带有异步复位的计数器。每次时钟脉冲为高时,计数就增加。这个设计由3个触发器组成,每个触发器代表一个比特。触发器由一些组合逻辑连接在一起形成一个计数器。当T输入高时,每个触发器就翻转;当T输入低时,触发器就保持一个当前状态。当把异步复位设置到0,则触发器恢复到0状态。

图1-5 3位计数器

计数器的代码包含2个模块:一个是简单的触发器,另一个是必须的胶合逻辑(Glue Logic)将触发器连接在一起形成一个计数器。

计数器包括3个触发器和一个与门。

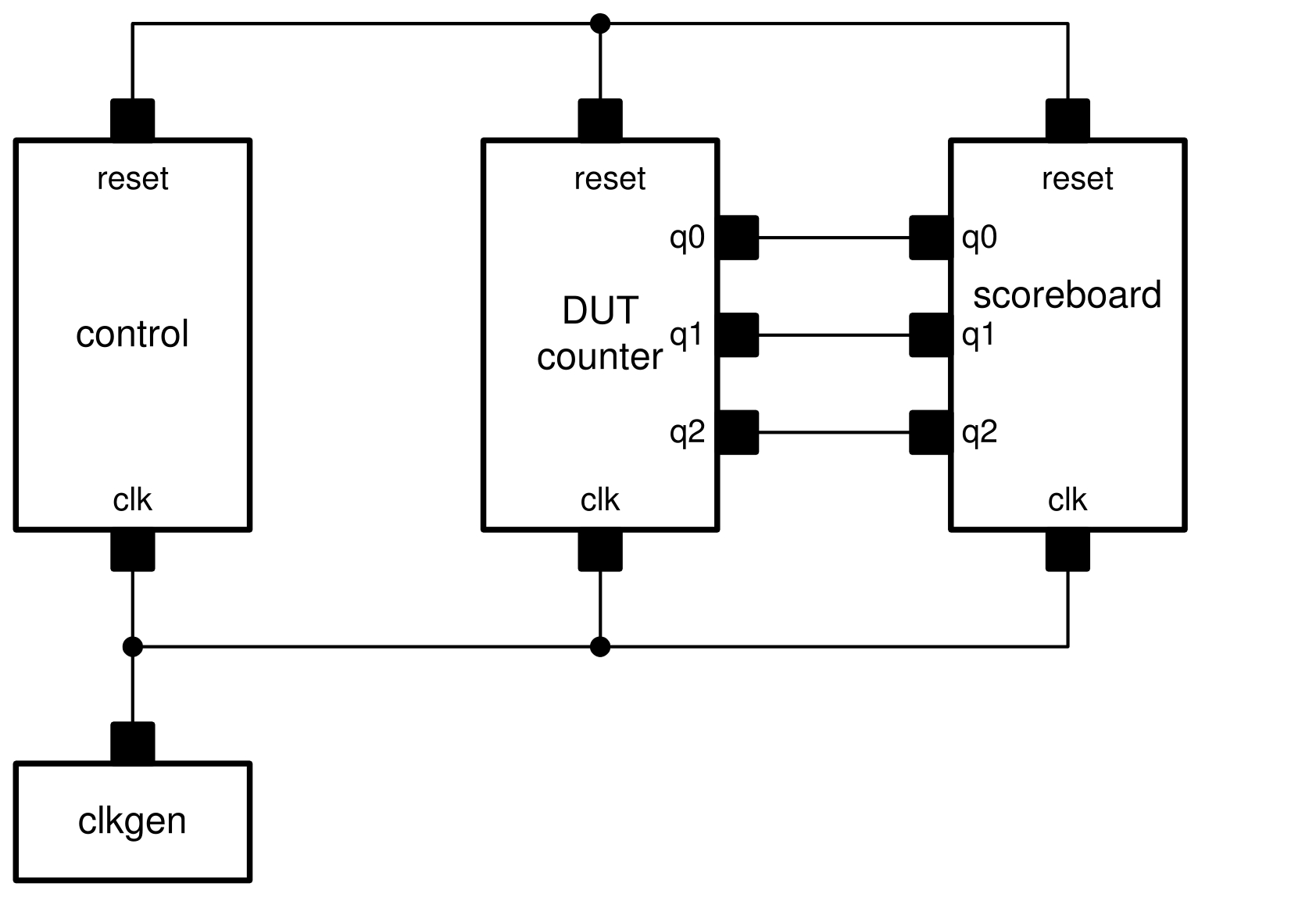

这个设计非常简单,但具有实际设计中的一般特点,为此在验证其正确性的过程中必须注意这些特点。最主要的特点就是这个设计是由时钟驱动并能够保持内部状态。而前面那个例子中的与门则不保持任何状态。设计正在运行的所有信息都可以从管脚收集,除了设计内部的数据。这个差别体现在记分板的设计上。图1-6展示了3位计数器验证平台的结构。

图1-6 3位计数器验证平台的结构

在许多方面,3位计数器的验证平台和与门的验证平台很相似。两者都有用来观察设计的运作并确定其是否是正确的记分板,都有一个驱动DUT的器件。但是,我们对它们采用了不同的操作方法。针对与门我们使用了激励生成器,而针对3比特计数器则采用了控制器(controller)。

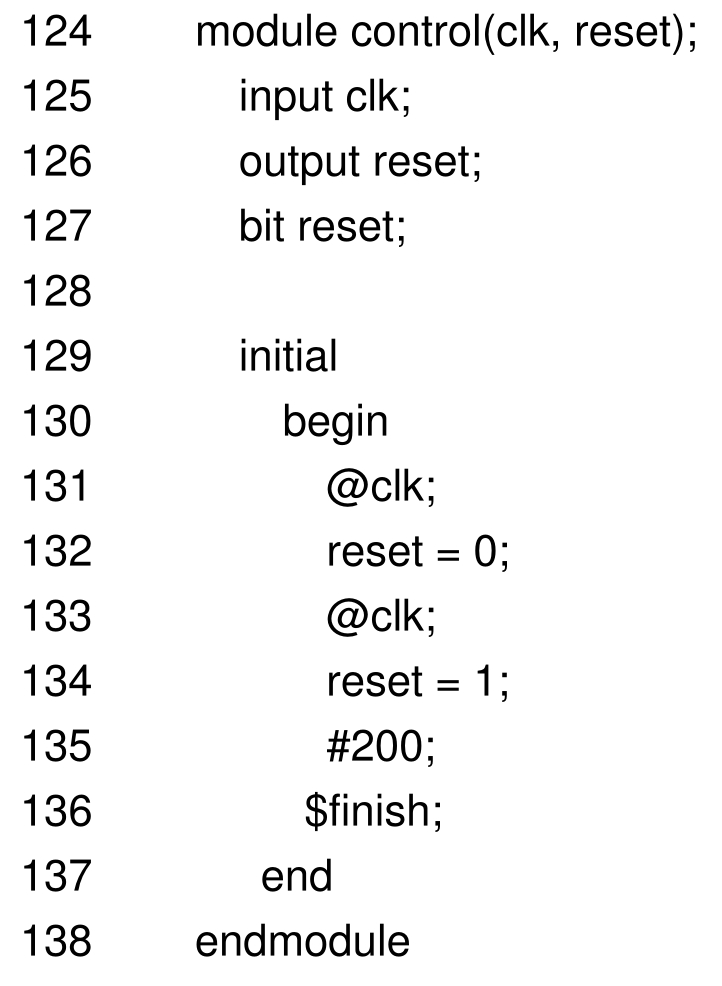

3比特计数器是一个自由运行的器件。只要它与时钟相连,它就会一直计数。因此无需激励生成器,而是由控制器来管理运行DUT和验证平台。控制器提供初始复位让计算器可以在一个确定的数值开始计数,它也能够在适当的时候控制停止仿真。

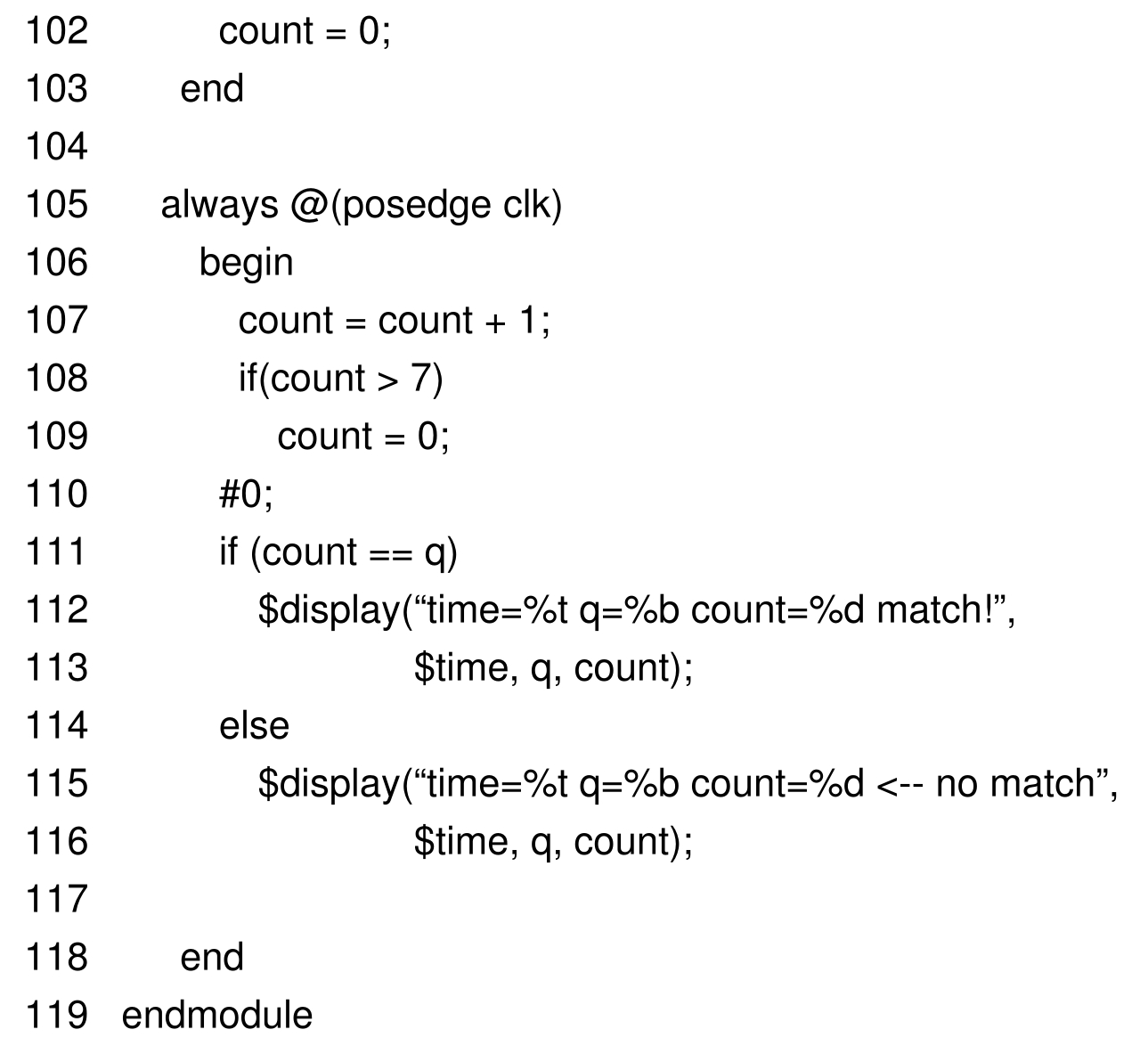

记分板必须记录DUT的内部状态。这是由变量count完成的。就如DUT一样,当reset进行复位的时候,count被置为0。每一个时钟循环count就加1,这个新数值与来自DUT的计数进行比较。

记分板有一个计数器的高层次的模型。它用整型变量和加法(+)运算符组成计数器,而不是使用触发器和与门。每一个时钟脉冲,计数增加,就像RTL计数器。它也进行比较,看其内部计数与计数器DUT的输出是否一致。

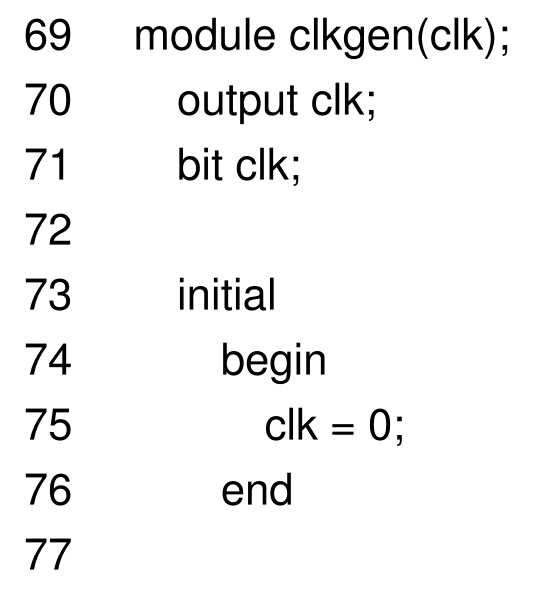

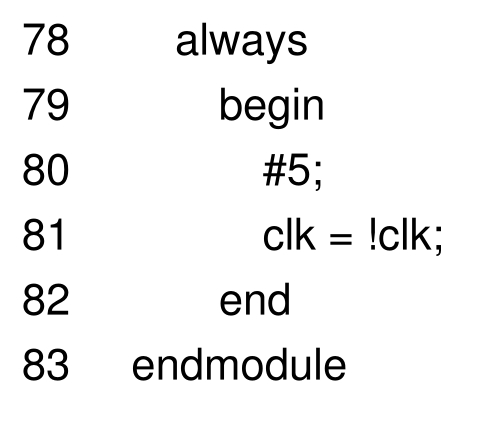

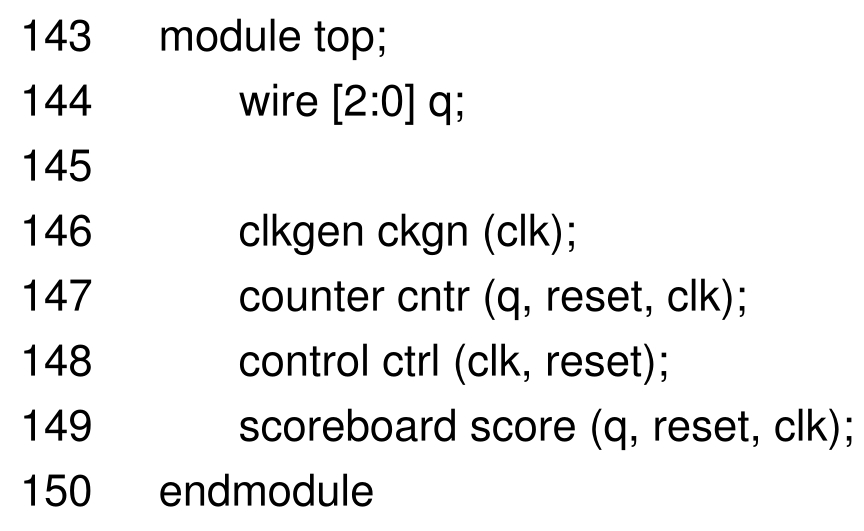

为了更全面地了解,我们给出了时钟生成器和顶层模块。时钟生成器简单地将时钟初始化为0,然后每5ns翻转一次。

顶层模块是一个典型的验证平台。它把DUT和验证平台的组件连接起来。

我们说明了一个简单的验证平台,它包含使用在更为复杂的验证平台中的基本部件。可维持内部状态的时序逻辑设计要求一个与DUT同时运行的记分板。它和DUT执行相同的计算,但是在更高的抽象层次上。记分板也将它自己的计算结果与来自于DUT的输入进行比较。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。