2.6.2 JTAG边界测试技术

JTAG边界测试技术是20世纪80年代由联合行动测试组(Joint Test Action Group,JTAG)开发的IEEE 1149.1-1990规范中定义的测试技术,是一种边界扫描测试(Board Scan Test,BST)方法,该方法提供了一个串行扫描路径,能够捕获器件中核心逻辑的内容,也可测试器件引脚之间的连接情况。

设计人员使用BST规范测试引脚连接时,再也不必使用物理探针了,甚至可在器件正常工作时捕获功能数据。器件的边界扫描单元能够从逻辑跟踪引脚信号,或是从引脚或器件核心逻辑信号种捕获数据。强行加入的测试数据串行地移入边界扫描单元,捕获的数据串行移出并在器件外部同预期的结果进行比较。

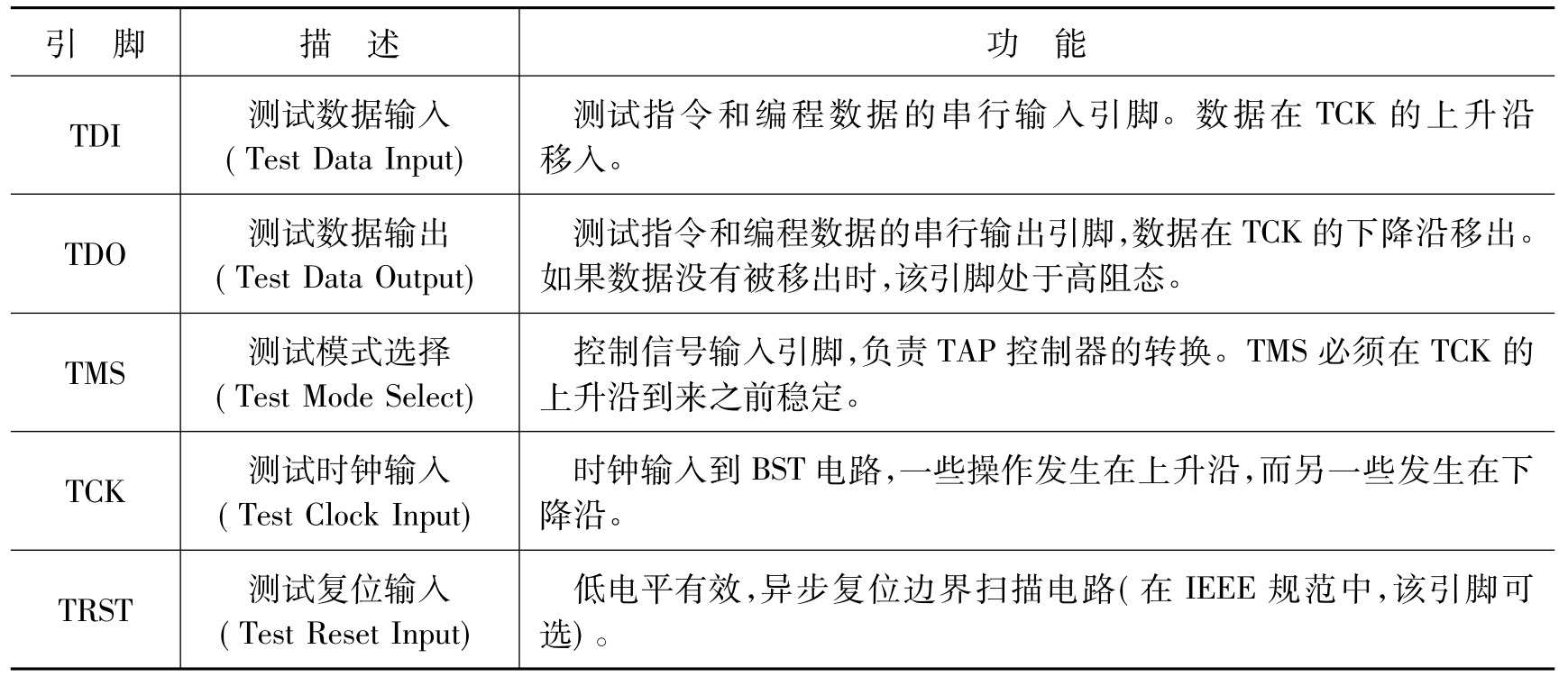

IEEE 1149.1-1990规范中定义了5个引脚用于JTAG边界测试,表2.1列出了这些引脚并概括了这些引脚的功能。

表2.1 边界扫描I/O引脚功能

为了实现边界扫描测试,芯片内还必须有BST电路,JTAG BST电路由TAP控制器和寄存器组组成,内部结构如图2.21。

TAP控制器是一个16位的状态机,它的作用是接收TCK、TMS、TRST输入的信号,产生UPDATEIR、CLOCKIR、SHIFTIR、UPDATEDR、CLOCKDR、SHIFTDR等控制信号,控制内部寄存器组完成指定的操作。内部寄存器组包括以下寄存器:

(1)指令寄存器(Instruction Register)

指令寄存器用于控制数据寄存器的访问以及测试操作。指令寄存器接收TAP控制器产生的UPDATEIR、CLOCKIR、SHIFTIR信号,产生控制指令经译码器输出给数据寄存器组。

(2)旁路寄存器(Bypass Register)

旁路寄存器是个1位的寄存器,是用于TDI引脚和TDO引脚之间的旁路通道。

(3)边界扫描寄存器(Board Scan Register)

边界扫描寄存器是一个串行移位寄存器,由所有边界扫描单元构成,利用TDI引脚作输入,TDO引脚作输出。

(4)器件ID寄存器

图2.21 JTAG BST电路内部结构图

(5)ISP/ICR寄存器

(6)其他寄存器

上电后,TAP控制器处于复位状态,指令寄存器初始化,BST电路无效,器件正常工作。利用TMS引脚输入控制信号,TAP控制器可完成状态转换,当TAP控制器前进到SHIFT-IR状态时,由TDI输入相应指令,进入TAP控制器的相应命令模式,并以SAMPLE/PRELOAD、EXTEST、BYPASS三种模式之一进行测试数据的串行移位。

TAP控制器的命令模式有:

(1)SAMPLE/PRELOAD模式。该指令模式允许在不中断器件正常工作状态的情况下捕获器件内部数据。

(2)EXTEST模式。该指令模式主要用于器件外部引脚的测试。

(3)BYPASS模式。该指令模式是TAP控制器缺省的测试数据的串行移位模式,数据信号在TCK上升沿进入,通过Bypass寄存器,在TCK下降沿输出。

(4)IDCODE模式。该指令模式用来标识IEEE Std1149.1链中的器件。

(5)USERCODE模式。该指令模式用来标识IEEE Std1149.1l链中的用户器件的用户电子标签UES(User Electronic Signature)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。