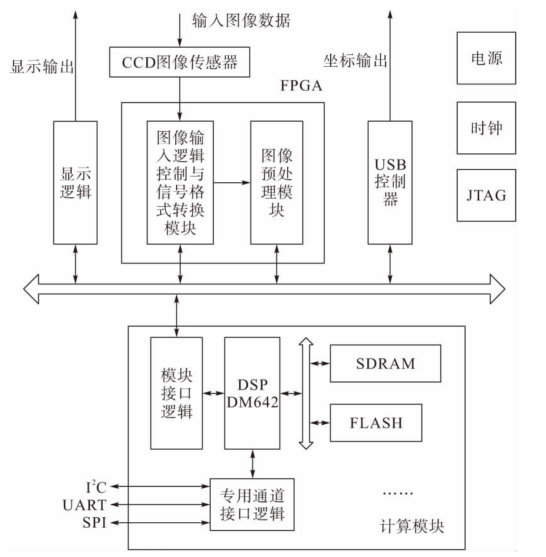

本章描述的系统是一个光学图像信息处理机,负责接收来自CCD成像传感器的光学图像序列,经过信息处理系统处理后,得到关于指点笔光斑目标的坐标位置信息,通过与上位机(控制计算机)接口将计算结果返回上位机,同时与上位计算机的应用软件配合,进行相关的操作,系统工作原理如图7-11所示。

图7-11 系统工作原理图

CCD成像传感器通过图像数字接口发送图像序列给图像信息处理机,图像序列信号通过隔离和驱动后,送往接口FPGA(Field-Programmable Gate Array,现场可编程门阵列)芯片,由对应的FPGA逻辑实现对图像序列数据的接收和增强,并送往缓存中,供DSP(Digital Signal Processor)系统读取和处理。FPGA逻辑还负责DSP系统和上位机系统的通信转换以及完成显示功能等。信息处理系统总体上分为以实现算法计算为核心的DSP系统和以实现接口及通信的FPGA逻辑组成的系统。

7.2.1 系统结构设计

由于针对简单背景的快速运动目标检测识别和图像畸变算法对实时图像处理系统提出的要求有所不同,所以在计算能力分配、系统控制方案等方面有所侧重。总的来说,所研制的实时图像识别系统具有资源可扩展、可剪裁、模块化、系统结构可在线重构等特点,有效地满足了不同图像处理算法对系统资源、系统并行化结构提出的不同要求。

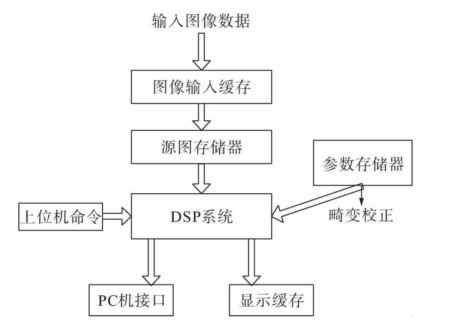

图7-12是图像信息处理系统的硬件框图。整个系统为一种松散耦合的DSP+FPGA体系。

图7-12 图像处理机的结构框图

系统由三类模块组成:计算模块、接口模块和显示模块。计算模块的任务是负责接收实时进入的图像、负责系统监控、与上位机通信以及主要的图像处理算法计算工作。接口模块主要用于与外部进行通信,扩充系统的计算能力,并预留有继续扩展的模块接口。显示模块主要完成显示任务。

系统中DSP采用的是目前Ti公司速度最快的定点DSP芯片TMS320DM642,其最大峰值速度为4800 MIPS。它有1 Mbit片内集成大容量SRAM,非常适合图像处理的需要;拥有64 bit高性能外部存储器接口(EMIF)1个,可与多种同步/异步存储器直接接口;有多达64个EDMA(Enhanced Direct Memory Access,增强型直接内存存取)通道,3个多通道缓冲串口(Mcbsp,最高速率达75 Mbit/s),以及3个32 bit的时钟,这些特征为DSP进行高速计算提供了工作条件,使DSP拥有强大的数据处理能力。

从图7-12还可看出,系统中的FPGA不仅承担了接口的作用,而且完成了部分图像预处理工作,用FPGA实现一些算法成熟而计算量大的预处理工作(如滤波、标记、校正等),从而较大程度上减轻了计算模块的负担,提高了系统的处理能力。系统的图像数据流程如图7-13所示。

图7-13为信息处理系统的数据输入输出流程图,输入图像数据在FPGA的FIFO里缓存后,传入系统的源图存储器里存放,DSP负责大量的相关图像处理算法的计算和校正参数的计算,FPGA逻辑实现存在校正参数情况下的图像校正、图像数据预处理、通信接口的实现、结果图像的显示等功能。

图7-13 图像数据输入输出流程

7.2.2 处理板接口设计

7.2.2.1 FPGA与CCD传感器的接口设计

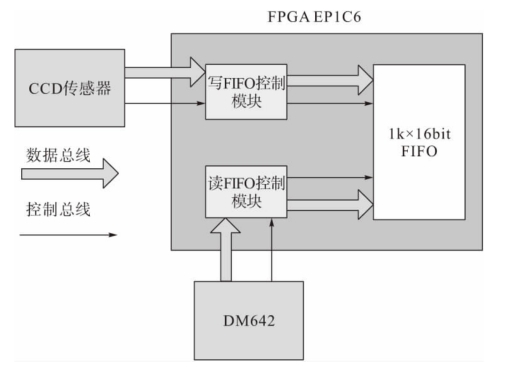

由CCD传出的图像数据的像素时钟是50 MHz,一帧图像的数据大小为1024×768×8 bits,由于CCD输出像素时钟频率太高且每帧图像数据量过大,如果DSP与CCD传感器直接连接,势必导致DSP外部总线负担过大,并且DSP也无法将图像数据全部接收存在内存里,所以考虑使用FPGA与CCD接口缓存图像数据,之后再由FPGA将图像数据传送给DSP接收。

在设计(胡佳,2007年)中,CCD输出的像素时钟为48 MHz,FPGA的工作频率为50 MHz,需要解决两者存在着工作频率不匹配的问题,因此在FPGA内形成一个异步读写的FIFO;设计中选用的FPGA为Altera Cyclone EP1C6,其拥有5980个LE逻辑单元,92160 bit的SRAM资源;为节约逻辑资源,FIFO的大小不可能很大,经过仔细考虑,设置FPGA内FIFO的大小为1 k×16 bit,使之能够缓存两行大小的图像。FPGA与CCD的接口设计框图如图7-14所示。

图7-14 FPGA与DSP、CCD传感器的接口框图

由图7-14可见,CCD将镜头采集到的图像数据写入到FPGA内形成的FIFO内,当FIFO内的图像数据存满一帧图像的一行大小时,FPGA给DM642一个外部中断,DM642读取FIFO接收的图像数据,由于FPGA内的FIFO可以容纳下两行图像,所以在DSP读图像的时候,CCD同时可以向FIFO内写入下一行的图像数据。

7.2.2.2 DSP端图像接收接口设计

DSP访问片外存储器时必须通过外部存储器接口EMIF。TMS320DM642具有很强的接口能力,可以与目前几乎所有类型的存储器直接连接。在设计中,DSP与外部FPGA内的FIFO的通信全部采用EMIF(External Memory Interface,外部存储器接口)口的同步FIFO接口来实现。

EMIF可编程同步接口提供4个控制信号(见表7-1)。这4个控制信号可以通过组合从而实现和FIFO的无缝连接。通过EMIF的CExCTL寄存器设置同步读/写的接口时序,可以满足对不同速度异步器件的存取。在设计中,DSP读FIFO的速度为100 MByte/s。

表7-1 C64X的可编程同步接口管脚

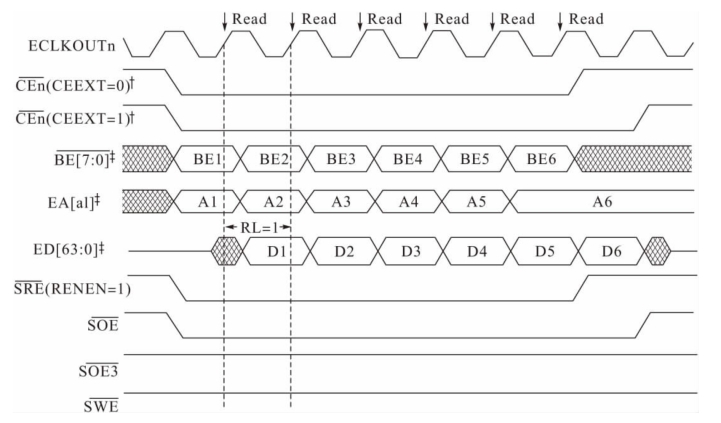

C64X的可编程同步接口同时支持标准FIFO以及FWFT FIFO的接口。图7-15是DM642的CE3空间与同步FIFO的无缝连接框图。

图7-15 CE3空间与同步FIFO的无缝连接

图7-16所示是DSP与标准同步FIFO读接口的时序,需要对CEXSEC寄存器作如下设置:

图7-16 与标准同步FIFO读接口时序图

●SYNCRL=01b,1周期的读延迟。

●RENRENN=1,/SADS/SRE管脚为/SRE信号。

●CEEXT=0,可以实现与FIFO的直接连接;CEEXT=1,接口需要辅助逻辑。

由于CCD的像素时钟很快,并且FIFO的容量很小,所以当FIFO里的数据存满一行像素时,FPGA给DSP一个中断(EXT4),通知DSP来取数据。DSP得到中断后,启动EDMA,将FIFO里的数据传输到DSP的片内(或者片外)内存里。

7.2.2.3 DSP的IIC接口设计

IIC(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。IIC总线产生于20世纪80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。

IIC总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。CCD器件是本系统中源图像的获取通道,CCD器件里有很多参数,在CCD器件启动后,它是按缺省的模式工作的。在本设计中,为了控制CCD芯片的工作模式,DSP使用IIC接口访问CCD芯片,发出命令和数据,从而修改CCD器件的工作状态。需要用DSP的IIC接口连上CCD器件的IIC接口,并且设置DSP的IIC接口为主器件,CCD的IIC接口为从器件,然后依照CCD器件的访问时序,DSP通过IIC接口设置CCD器件的寄存器,使CCD器件配置成所需的模式。

下面举两例说明DSP配置CCD器件的时序,图7-17所示为IIC向CCD行大小寄存器(0x04)写入值(0x027F),图7-18所示为IIC从CCD读出行大小寄存器(0x04)的值,返回0x027F。

图7-17 IIC向CCD行大小寄存器(0X04)写入值(0X027F)

图7-18 IIC从CCD读出行大小寄存器(0x04)的值,返回0x027F

7.2.2.4 DSP的USB接口设计

Cypress公司生产的USB接口控制芯片EZ-USB CY7C68001可与任何ASIC、MCU或DSP进行连接,并且支持所有通用总线标准。在USB协议定义的4种传输模式中,批量传输和等时传输的速度较快。但批量传输具有差错校验,可以保证数据传输的正确性。因为实际应用对数据的准确性要求较高,故采用批量传输方式。

该芯片在与DM642连接时,芯片内的FIFO作为外部存储器接在DSP的CE2外部空间上,DSP通过芯片的控制引脚和读写FIFO实现USB的传输。DM642与CY7C68001的硬件接口框图如图7-19所示。

图7-19 DM642与CY7C68001的接口

CY7C68001内的FIFO作为16位的异步FIFO配置在DM642的外部存储空间上,CY7C68001提供给DSP两种接口:一个是FIFO接口,SX2内的4 kbyte的RAM(8个512 byte块)分别分配给端点EP2、EP4、EP6、EP8;另一个是命令接口,使用端点EP0,用于初始化芯片、读取状态、加载描述府和访问端点等。DM642通过对CY7C68001地址线FIFOADDR[2∶0]的控制访问上述两种接口。CY7C68001内的FIFO地址分配见表7-2。2007年,华中科技大学胡佳的硕士论文还研究了小目标检测和图像畸变校正算法。

表7-2 DSP对CY7C68001的寻址

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。