7.5.6 脉冲计数器

脉冲计数器也是一种由触发器构成的数字电路,是组成数字逻辑电路的基本部件。它能累计输入脉冲的个数并以代码的形式表示这个数目。脉冲计数器可以进行加法计数、减法计数等。

1.异步二进制计数器

图7.5-12所示电路是一种由3个JK触发器组成的脉冲计数器的实现电路,设3个触发器的初始状态为0,由于计数脉冲从触发器FF0的“C0”端输入,而且低位触发器的输出作为高位触发器的脉冲直接与高位触发器的“C”端连接,也就是说,各个触发器所接受的脉冲信号不是同一个,造成各个触发器状态的变化有先有后,是异步的,所以称该电路为异步计数器。

图7.5-12 异步二进制计数器

分析计数器计数过程的步骤如下。

①写出各触发器的驱动方程,即触发器输入端变量的表达式。

J0=K0=1,J1=K1=1,J2=K2=1

注意:触发器的J、K端悬空,处于高电位状态。

②填写状态转换表。

因为各触发器的J、K输入均为高电平,所以,每当触发脉冲的下降沿到来时,Q0翻转,即由1变为0,或由0变为1;每当Q0由1变为0时,Q1翻转;当Q1由1变为0时Q2翻转。由此,得表7.5-7。

表7.5-7 分析计数器所用的状态转换表

③图示电路中的各触发器均为下降沿触发,其工作波形如图7.5-13所示。

图7.5-13 图7.5-12所示电路的工作波形

④根据状态转换表和波形图,得出适当的结论。

该计数器的工作方式为“异步”的;3个触发器的输出端Q2、Q1、Q0以二进制形式表示输入的脉冲数,每一个触发器实质上完成的是一位二进制数的加法运算,从低位输出送入上一位C端的信号实质上是低位加法器的进位。

综上,该计数器是一种异步的4位二进制加法计数器。

从信号处理的角度看,Q0输出4个脉冲,是8个CP脉冲的1/2,所以,Q0为二分频输出端,同理可知,Q1和Q2分别构成4分频和8分频。所以,二进制脉冲计数器也用来作为数字信号的分频器使用。

确定计数器进制数的方法还有一种,即根据计数器所能计的最大脉冲个数作为进制数,例如图7.5-8所示计数器最多能计8个脉冲,因此,它又是一个异步的1位8进制计数器。

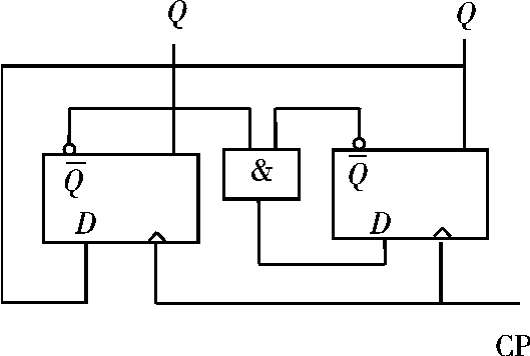

图7.5-14 例7.5-6图

【例7.5-6】设图7.5-14所示电路的2个D触发器的初始状态为“0”,则该电路是( )。

(A)异步二进制计数器

(B)同步三进制计数器

(C)异步四进制计数器

(D)同步五进制计数器解:答案为选项(C)。

根据已知电路图可知,该电路2个D触发器的CP来自不同信号,而且是上升沿触发,所以图示电路为上升沿触发的异步计数器。

触发器的驱动方程:D0=

根据驱动方程和D触发器的逻辑功能状态表,可得计数器的输出状态,如下表。

从整体来看计数电路,由于是4个状态一循环,所以该计数器为四进制计数器。

综上所述,(C)选项为本题答案。

2.同步二进制计数器

图7.5-15 例7.5-7图

所谓“同步”是指计数器中各个触发器的脉冲来自同一个信号,致使触发器的输出状态同步变化。以例7.5-7说明同步计数器的工作。

【例7.5-7】分析图7.5-15所示逻辑电路的逻辑功能,并用输入/输出逻辑信号波形图加以说明。

解:电路中各触发器的驱动方程:D0= D1=Q0。

D1=Q0。

该电路各触发器的状态如表7.5-8:

表7.5-8 各触发器的状态转换

图7.5-15 电路的工作波形

综上可知:电路为三进制同步计数器(上升沿触发)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。