【摘要】:在SystemVerilog中,随机变量、随机数发生器和约束条件都可被集成在面向对象的类系统中。SystemVerilog用rand关键字来区别随机变量和非随机变量。在本例中,调用P.randomize将使用约束addr_range生成随机变量m_address的值,同时生成没有约束的随机变量m_data的值。检查随机函数randomize()的返回值。如果放在一个类中并加在随机变量上的约束条件没有解,randomize()返回0。对返回值的检查是很重要的,这样一旦发现任何问题都会报告给用户。立即断言对报告这些问题很有用。

10.2 对类加入随机

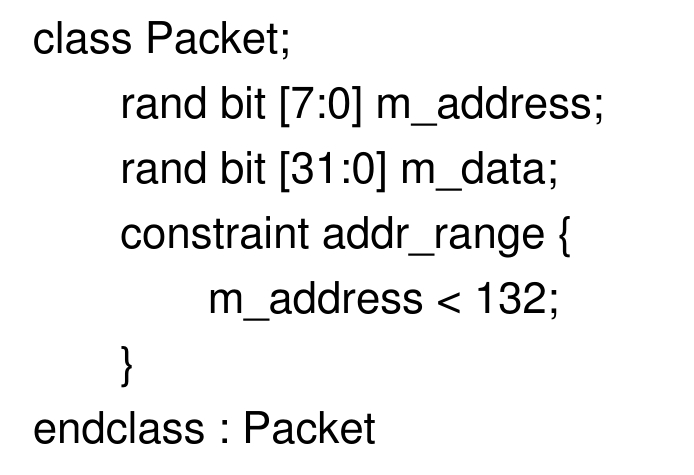

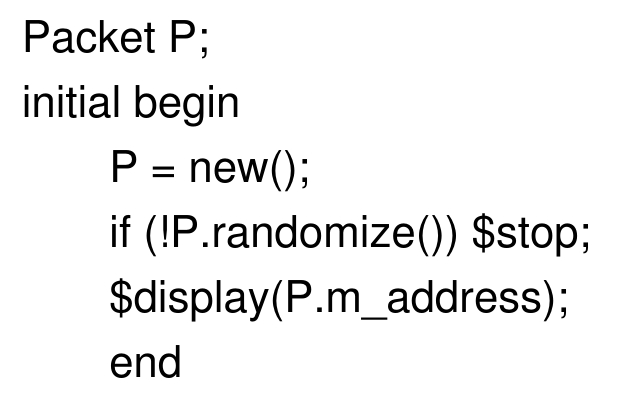

在SystemVerilog中,随机变量、随机数发生器和约束条件都可被集成在面向对象的类系统中。randomize( )函数是系统内建的成员函数,可以在所有的类中直接使用。SystemVerilog用rand关键字来区别随机变量和非随机变量。用有名的表达式列表定义约束,并用constraint关键字声明约束。

通过使用类的内嵌成员函数randomize(),来调用RNG和约束求解器,randomize()在类构造完成后就可以调用。在本例中,调用P.randomize将使用约束addr_range生成随机变量m_address的值,同时生成没有约束的随机变量m_data的值。

检查随机函数randomize()的返回值。如果放在一个类中并加在随机变量上的约束条件没有解,randomize()返回0。对返回值的检查是很重要的,这样一旦发现任何问题都会报告给用户。立即断言对报告这些问题很有用。

![]()

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。