2.2.3 结构级(Structural Level)描述

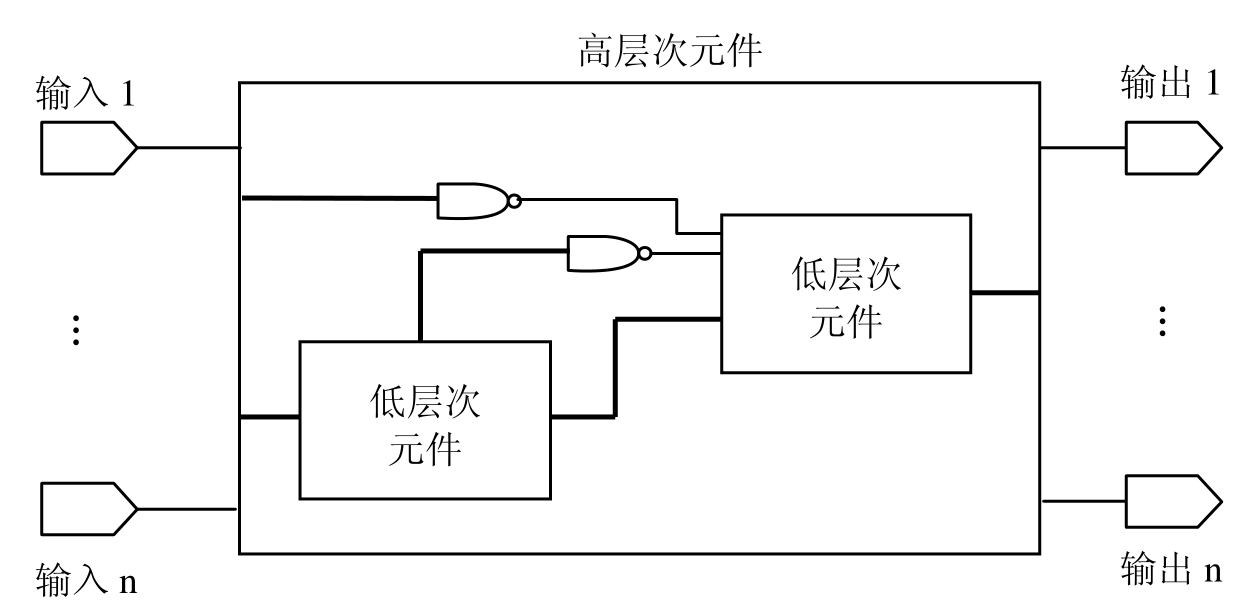

结构级描述(如图2.13所示)描述电路或系统的功能和结构。将其应用在层次化设计中,可方便地实现高层次设计模块调用低层次设计模块,或者直接调用基本逻辑单元来构成一个复杂逻辑电路。从设计共享和复用的角度讲,结构级描述的程序最能提高设计效率,它可以将已有的设计成果,方便地用到新的设计中去。

图2.13 结构级描述示意

【例2-11】全加器adder的结构级描述

在认识到所讨论的“一个五端口电路”其实就是一个全加器以后,可以进一步运用我们对全加器的认识:如图2.14所示,全加器可以由两个半加器(half_adder)和一个“或”门(or_gate)组成。假定这些元件已设计完成,那么,调用这些现成的元件,经过适当连接组合就可以构成一位全加器adder的结构级描述了。

图2.14 全加器的一种逻辑结构图

用半加器和“或”门构建全加器的结构级描述如下:

例2-11的VHDL源程序的构造体中先说明了本构造体所引用的两类元件(COMPONENT)的名称及各自的端口情况,继而申明了构造体中所需用到的内部信号(SIGNAL)线a,b和c。在关键字BEGIN后为三个元件引用例示语句。u1,u2,u3是三个引用元件的标号,标号后紧跟的是所引用的元件名及各端口与内部信号的连接关系(即端口映射PORT MAP)。上述结构级建模的程序描述经逻辑综合后,即可得到与图2.14相同结构的电路原理图。

如果结构级描述中使用的元件,全都是ASIC代工厂或可编程器件提供的基本元件,那么其VHDL源程序描述的结构与该程序综合后的门级网表结构将一一对应。

在本章的例子中,涉及了VHDL程序中一些常见的基本语句,其基本格式及基本用法的详细内容将在后续章节中逐一介绍。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。