10.1 Verilog HDL程序模块结构

10.1.1 模块端口定义

模块端口定义用来声明设计电路模块的输入输出端口。端口定义的格式如下。

MODULE模块名(端口1,端口2,端口3,...);

端口定义的圆括弧中的内容是设计电路模块与外界联系的全部输入输出端口信号或引脚,它是设计实体对外的一个通信界面,是外界可以看到的部分(不包含电源和接地端),多个端口名之间用“,”分隔。例如,

MODULE ADDER(SUM,CONT,INA,INB,CIN);

10.1.2 模块内容

模块内容包括模块的I/O说明、信号类型声明和功能描述。

1.模块的I/O说明

模块的I/O说明用来声明模块端口定义中各端口的数据流动方向,包括输入(INPUT)、输出(OUTPUT)和双向(INOUT)。I/O说明的格式如下。

INPUT端口1,端口2,端口3,...;

OUTPUT端口1,端口2,端口3,...;

例如:

INPUT INA,INB,CIN;

OUTPUT SUM,CONT;

2.信号类型声明信号类型声明用来说明在设计电路的功能描述中所用信号的数据类型及函数声明。信号的数据类型主要有连线(wire)、寄存器(reg)、整型(integer)、实型(real)和时间(time)等类型。

3.功能描述

功能描述是Verilog HDL程序设计中最主要的部分,用来描述设计模块的内部结构和模块端口间的逻辑关系,在电路上相当于器件的内部电路结构。

功能描述可以用ASSIGN语句、元件例化(instantiate)方式、ALWAYS块语句、INITIAL块语句等方法来实现,通常把确定这些设计模块描述的方法称为建模。

1)用ASSIGN语句建模

用ASSIGN语句建模的方法很简单,只需要在“ASSIGN”后面再加一个表达式即可。ASSIGN语句一般适合对组合逻辑进行赋值,称为连续赋值方式。

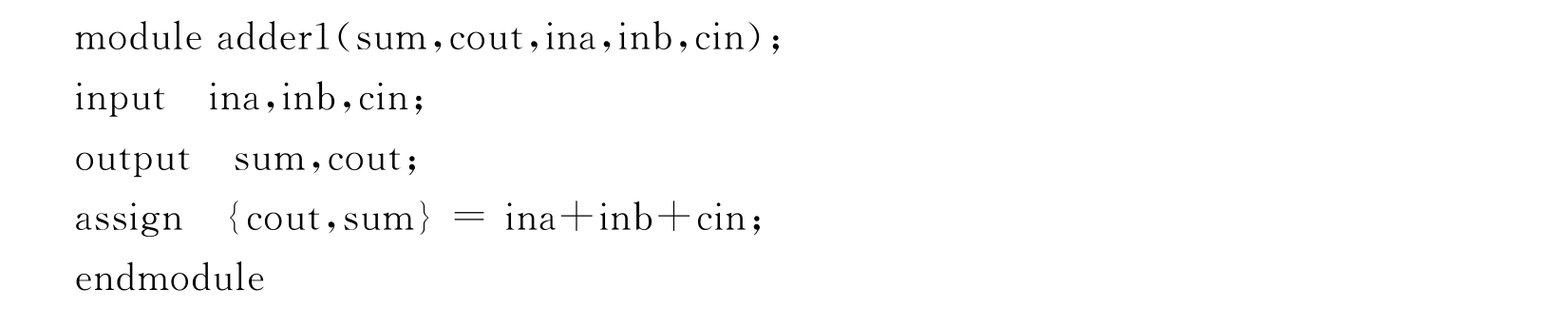

【例10.1.1】 1位全加器的设计。

设计1位全加器的Verilog HDL源程序如下。

2)用元件例化方式建模

元件例化方式建模是利用Verilog HDL提供的元件库来实现的。

例如,用与门例化元件定义一个3输入端与门可以写为

AND MYAND3(y,a,b,c);

3)用ALWAYS块语句建模

ALWAYS块语句可以产生各种逻辑,常用于时序逻辑的功能描述。一个程序设计模块中,可以包含一个或多个ALWAYS语句。程序运行中,在某种条件满足时,就重复执行一遍ALWAYS结构中的语句。

8位二进制加法计数器的Verilog HDL源程序如下。

4)用INITIAL块语句建模

INITIAL块语句与ALWAYS块语句类似,不过在程序中它只执行1次就结束了。

现对Verilog HDL程序设计模块的基本结构做如下小结。

(1)Verilog HDL程序是由模块构成的。每个模块的内容都是嵌在MODULE和ENDMODULE两语句之间的,每个模块实现特定的功能,模块是可以进行层次嵌套的。

(2)每个模块首先要进行端口定义,并说明输入、输出或双向,然后对模块的功能进行逻辑描述。

(3)Verilog HDL程序的书写格式自由,一行可以一条或多条语句,一条语句也可以分为多行写。

(4)除了END或含END(如ENDMODULE)的语句外,每条语句后必须要有分号。

(5)可以用/*......*/或//......对Verilog HDL程序的任何部分作注释。一个完整的源程序都应当加上需要的注释,以增强程序的可读性。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。