12.4 SoPC设计流程与支持Nios II的FPGA器件

12.4.1 SoPC设计流程

在采用Nios II处理器设计嵌入式系统时,一般遵循以下流程:

(1)分析系统需求说明,包括功能需求和性能要求等;

(2)建立Quartus II工程,建立顶层实体;

(3)调用SoPC Builder,生成一个用户定制的系统模块(包括Nios II及标准外设模块);

(4)将SoPC系统模块集成到硬件工程中,并添加一些模块,可以是Altera公司提供的LPM模块、第三方提供的或用户自己定制的模块;

(5)在顶层实体中,将SoPC系统模块、Altera的LPM或用户自定义的模块连接起来;

(6)分配引脚和编译工程,编译生成系统的硬件配置文件.sof和.pof文件;

(7)下载工程,将配置文件下载到开发板上进行验证;

(8)软件开发,开发可以使用IDE开发环境,也可以使用SDK Shell;

(9)编译软件工程,生成可执行文件.elf;

(10)调试程序,将硬件配置文件下载到开发板,将可执行文件下载到RAM,直到软硬件协同工作。

在上面的过程中,用到的软件有Quartus II、Nios II SDK shell或Nios II IDE、ModelSim等,如果进行DSP的开发,还会用到Matlab和DSPBuilder。

Quartus II用来建立硬件的系统包括SoPC Builder工具,SoPC Builder用来建立SoPC系统模块,Quartus II支持多种设计方式,如原理图、硬件描述语言等,硬件描述语言支持VHDL和Verilog等方式。

软件开发使用Nios II SDK shell或Nios II IDE,IDE开发环境采用图形化的开发环境,使用方便直观。而SDK shell采用命令窗口的方式进行程序的调试。

ModelSim是HDL编译仿真软件,用于对设计的硬件系统进行RTL级的仿真。

DSP Builder是Altera公司推出的数字信号处理开发软件,用来实现算法和硬件实现的无缝过渡,用户可以在Matlab的Simulink中完成算法模型的仿真、验证,然后通过SignalCompiler将模型文件转换成硬件描述语言的文件。

12.4.2 支持Nios II的FPGA器件

支持Nios II的FPGA器件有Cyclone和Cyclone II系列、Stratix和Stratix II系列、HardCopy器件、HardCopy II、HardCopy Stratix、HardCopy APEX三代。

1.Cyclone和Cyclone II系列

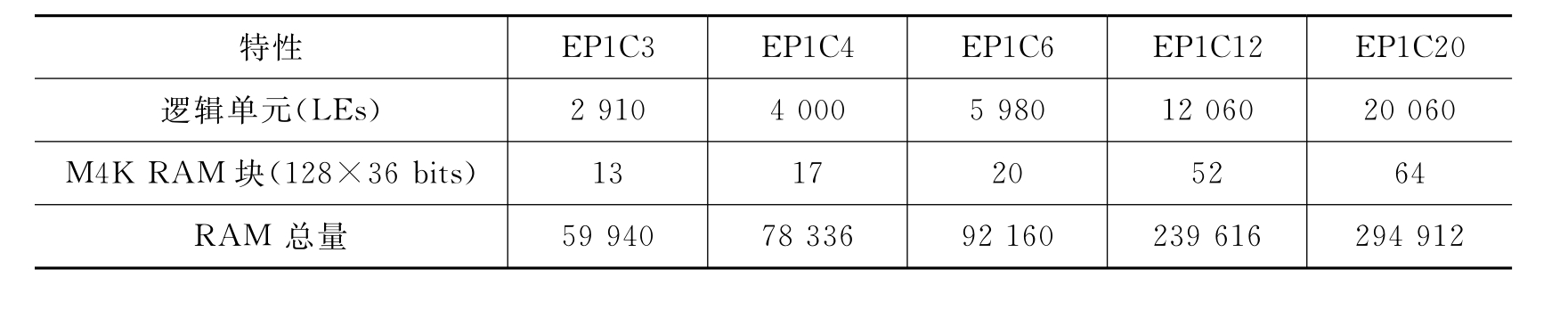

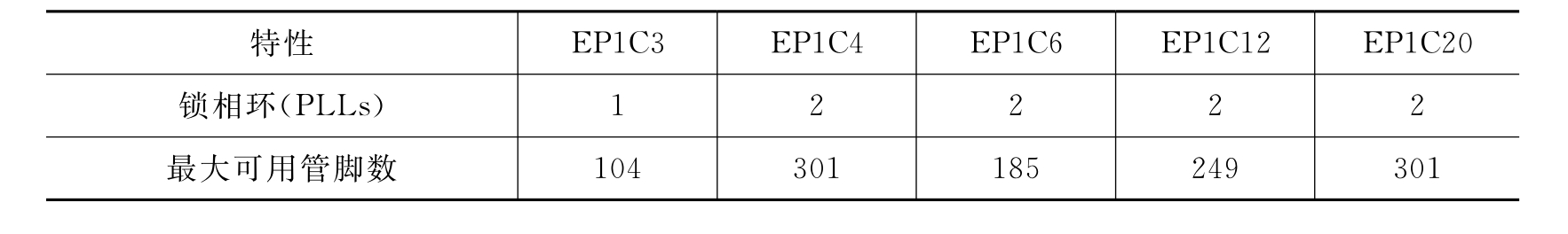

Cyclone系列器件基于1.5V、0.13μm及全铜SRAM工艺,Cyclone系列FPGA的容量为2 910~20 060个逻辑单元(LE),拥有288K位的RAM,如表12.4.1所示。Cyclone系列FPGA的最大特点是低成本,Cyclone系列FPGA是成本敏感大批量应用的最佳方案。如果需要进一步进行系统集成,可以考虑密度更高的Cyclone II FPGA和Cyclone III FPGA。Cyclone系列巩固了Altera在大批量、低成本应用方案中的领先优势。

Cyclone FPGA是目前ASIC应用的低成本替代方案。利用其系统级集成功能,Cyclone系列FPGA避免了ASIC昂贵的NRE负担,降低了订购量和产品推迟带来的风险。

Cyclone系列FPGA的价格和功能满足了市场对创新的需求,通过产品迅速面市来确定领先优势。消费类、通信、计算机外设、工业和汽车等的低成本大批量应用市场都可以使用Cyclone系列FPGA。

表12.4.1 Cyclone系列产品的主要性能

续表

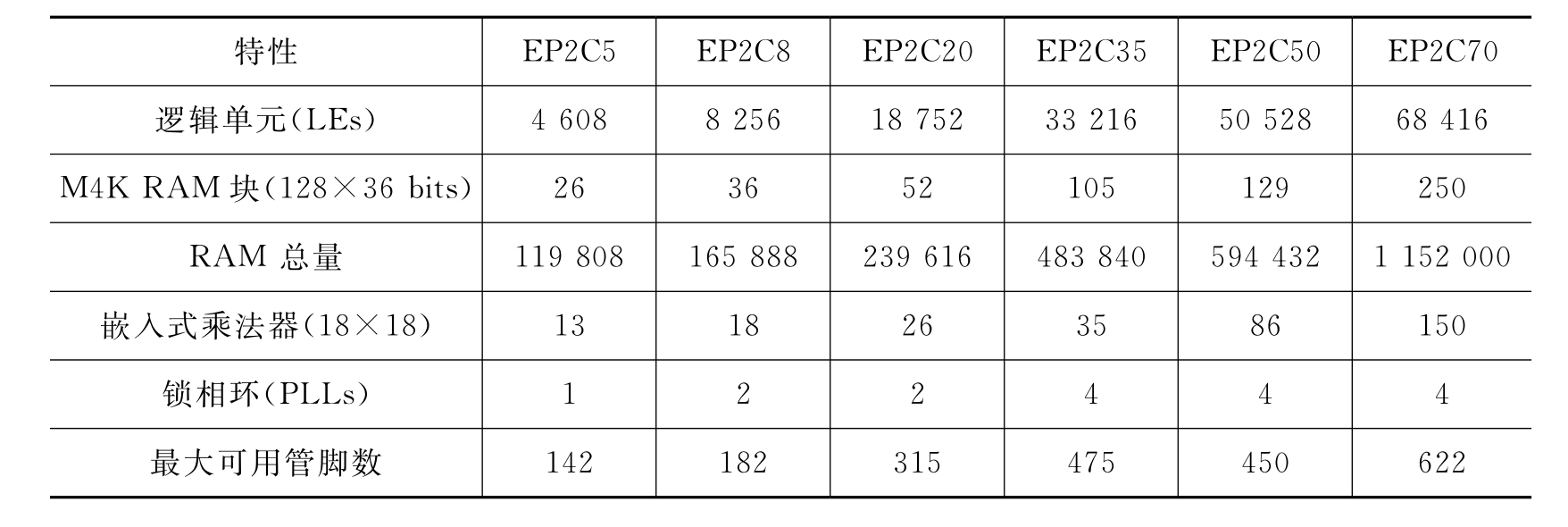

Cyclone II是Altera公司在第一代Cyclone系列的基础上开发的第二代FPGA系列器件,如表12.4.2所示。Cyclone II采用了全铜层90nm低k绝缘工艺,1.2VSRAM工艺设计。Cyclone II具有很高的性能和极低的功耗,而价格和ASIC相当。它的应用领域和Cyclone系列相似,是对成本敏感的应用大批量的产品解决方案,是消费类、通信、计算机外设、工业和汽车、视频处理等终端市场解决方案的理想选择。

表12.4.2 Cyclone II系列产品的主要性能

Cyclone II为在FPGA上实现低成本的数字信号处理系统提供了一个理想的平台,用户可以单独使用Cyclone II或者作为数字信号处理协处理器使用。Cyclone II器件含有经过优化的多种DSP特性,为Altera全面的DSP流程提供支持。

Cyclone II DSP支持包括:多达150个的18×18乘法器;1.1M位的片内嵌入式存储器;外部存储器高速接口;DSP IP内核。68 416个逻辑单元(LE)提供了嵌入式18× 18位乘法器、专用外部存储器接口电路(最高速率可达668Mb/s)、4K位嵌入式存储器块、最多为4个的增强型锁相环等。

2.Stratix和Stratix II系列

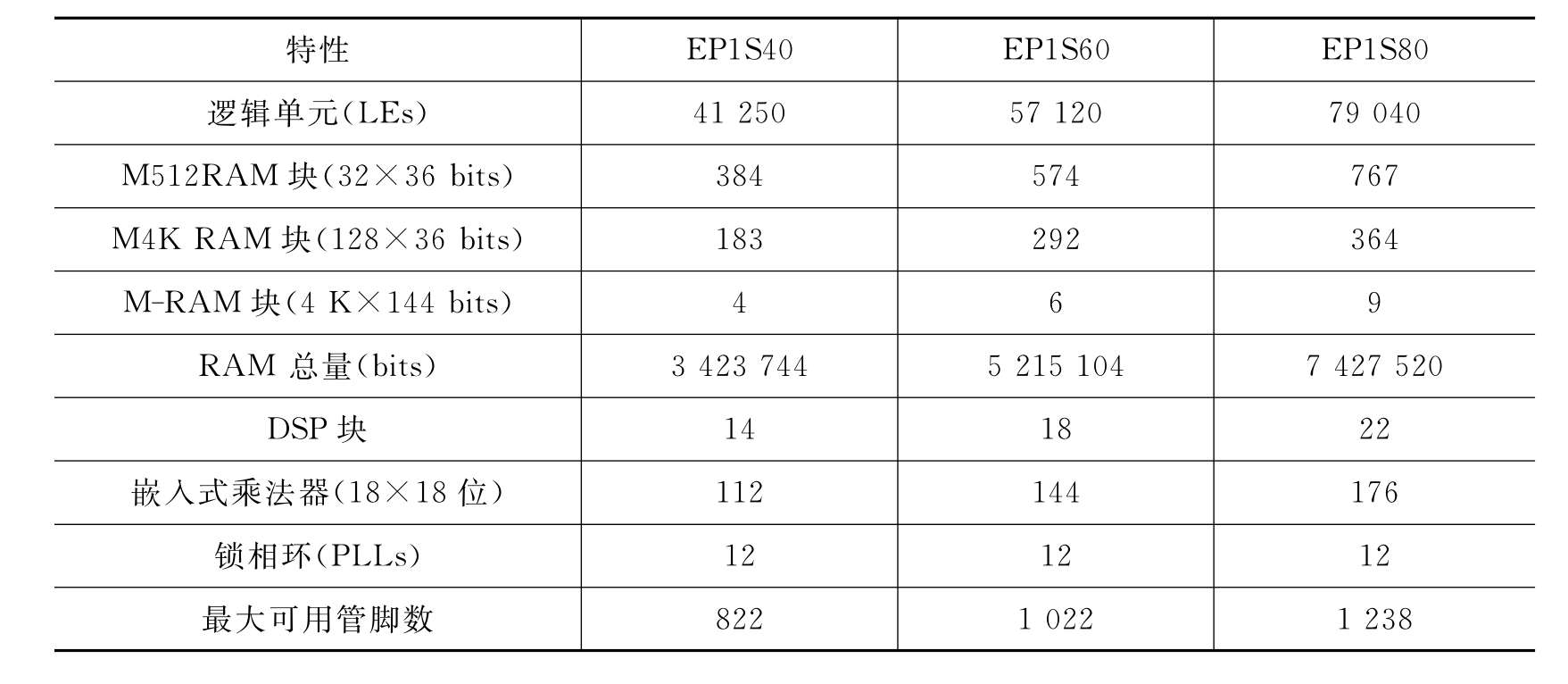

Stratix FPGA是Altera公司的第一代Stratix系列器件。Stratix系列器件是Altera公司的大规模高端FPGA,于2002年推出,采用0.13μm的工艺,1.5V内核供电,容量为10 570~79 040个逻辑单元、具有7M位的RAM。Stratix器件具有22个DSP块和176个9×9位嵌入式乘法器,同时器件还具有多种高性能的I/O接口、层次时钟结构和12个锁相环,如表12.4.3所示。第一代Stratix FPGA依然是军用和航空航天领域所选用的FPGA,在这些应用中需要较宽的工作温度范围。

Stratix II和Stratix III器件由于采用了创新性的逻辑结构,不但具有前代Stratix器件的所有特性,而且功耗更低、性能更好。Stratix II与Stratix相比,运行速度提高50%,逻辑容量提高1倍,而成本更低。Stratix III器件是功耗最低、性能最好的FPGA之一。

表12.4.3 Stratix系列产品的主要性能

Stratix II器件于2005年推出,在Stratix架构的基础上做了一些适合于90nm工艺的改进,采用1.2V、90nm、9层金属走线、全铜SRAM工艺制造。Stratix II器件在Stratix的基础上增加了新的特性:采用了全新的逻辑结构——自适应逻辑模块(ALM);增加了源同步通道的动态相位校准(PDA)电路和对新的外设存储器接口的支持;采用了128位AES密钥对配置文件进行加密。

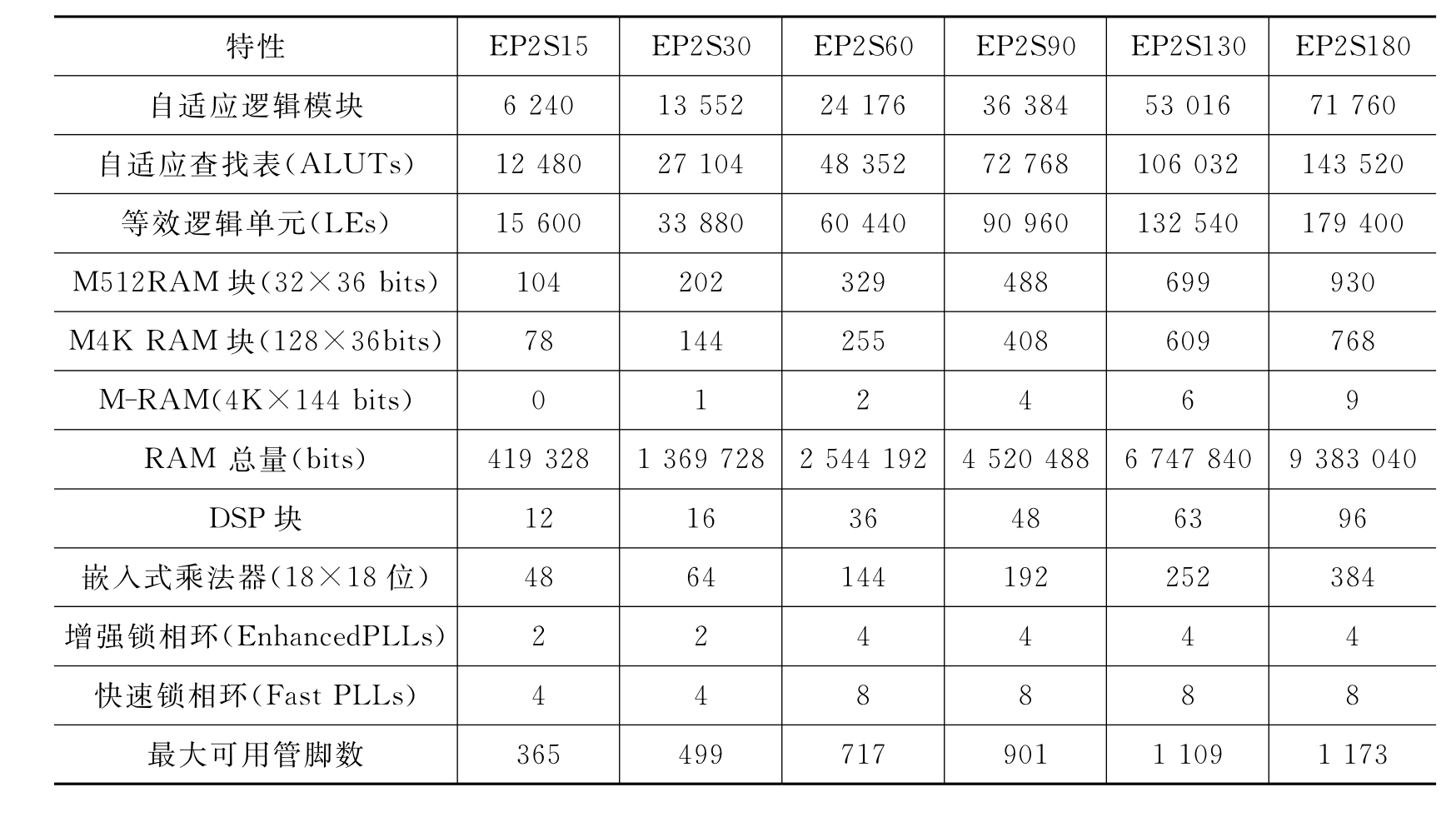

Stratix II FPGA采用等效逻辑单元高达179 400个,嵌入式存储器达到9M位,最大可用管脚数达到1 173个,高度优化的数字信号处理模块中18×18位嵌入式乘法器数量达到384个,如表12.4.4所示。

表12.4.4 StratixII系列产品的主要性能

3.HardCopy器件

HardCopy就是利用原有的FPGA开发工具,将成功实现于FPGA器件上的SoPC系统通过特定的技术直接向ASIC转化,从而克服传统ASIC设计中普遍存在的问题(如开发周期长、产品上市慢、一次性成功率低、有最少投片量要求、设计软件工具繁多且昂贵、开发流程复杂等)。HardCopy II体系结构建立在被称为Hcell的精细粒度晶体管阵列上。Hcell支持FPGA的无缝移植,具有ASIC技术那样的密度、成本、性能和功耗优势。

HardCopy II结构化ASIC具有独特的FPGA前端设计方法,实现了业界风险最低、产品面市最快的解决方案。Altera公司的HardCopy设计中心将设计无缝移植为低成本、功能等价、引脚兼容的HardCopy II器件。

Altera公司率先推出40nm工艺的FPGA,Straitix IV和HardCopy IV超越了ASIC的平均密度。它们的性能和功耗都有很大改善,高密度,具有22.4Mbits嵌入式存储器和1 360个18×18乘法器。

Stratix IV比市场上的其他高端FPGA功耗低50%。

Stratix IV FPGA和HardCopy IV ASIC相结合,同时具备了FPGA的优势和ASIC的优势。HardCopy IV ASIC为满足定制逻辑需求提供了风险最低、总成本最低、产品面市最快、收益最快的解决方案。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。