实验二十九 竞争冒险实验

一、实验目的

1.了解组合逻辑电路和时序逻辑电路竞争冒险现象产生的原因。

2.了解冒险现象的消除方法。

3.了解在软件中模拟竞争冒险产生的方法。

4.初步了解MAX+plus II软件的使用。

二、实验原理

1.一般竞争冒险的产生及消除

(1)理论上分析组合逻辑电路时,都没有考虑门电路的延迟时间对电路产生的影响。实际上,从信号输入到输出稳定都需要一定的时间。由于从输入到输出的过程中,不同通路上门的级数不同,或者门电路平均延迟时间的不同,使信号从输入经不同通路传输到输出级的时间不同。由于这个原因,可能会使逻辑电路产生错误输出。通常把这种现象称为竞争冒险。

(2)竞争冒险现象有两种情况,分别是0型竞争冒险现象和1型竞争冒险现象。

①0型竞争冒险现象

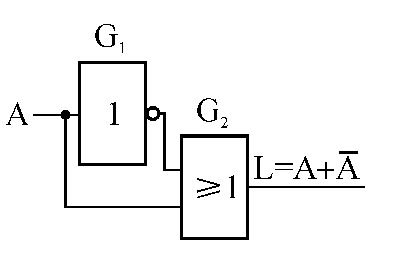

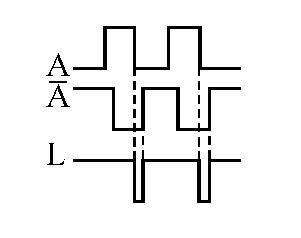

其电路图如图6-161所示,波形图如图6-162所示。

图6-161 0型竞争冒险电路图

图6-162 波形图

输出函数L=A+A,在电路达到稳定时,即静态时,输出L总是1。然而在A变化时(动态时),从图6-163可见,在输出L的某些瞬间会出现0,即当A经历1变0的变化时,L出现负窄脉冲,即电路存在静态0型竞争冒险现象。或门G2的两个输入信号分别由G1和A端两个路径在不同时刻到达的现象,通常称为竞争,由此产生输出干扰脉冲的现象称为冒险。

②1型竞争冒险现象

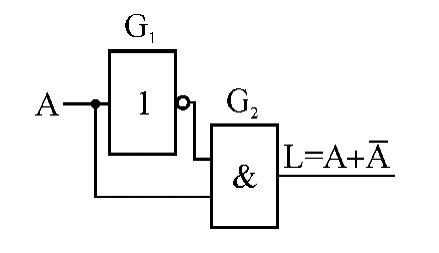

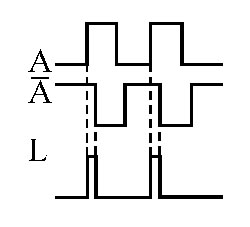

其电路图如图6-163所示,波形图如图6-164所示。

图6-163 1型竞争冒险电路图

图6-164 波形图

输出L=A A,在电路达到稳定时,即静态时,输出L总是0。然而在A变化时(动态时),从图6-164可见,在输出L的某些瞬间会出现1,即当A经历0变1的变化时,L出现窄脉冲,即电路存在静态1型竞争冒险现象。

(3)总结

当电路中存在由反相器产生的互补信号,且在互补信号的状态发生变化时可能出现竞争冒险现象。

(4)消除竞争冒险的方法

①发现并消掉互补变量

例如,函数式F=(A+B)(-A+C),在B=C=0时,可得F=A-A。若直接根据这个逻辑表达式组成逻辑电路,则可能出现竞争冒险。可以将函数式化为F=AC+-AB+BC,根据这个表达式组成逻辑电路就不会出现竞争冒险。

②增加乘积项

例如,函数式L=AC+B-C,当A=B=1时,可得L=C+-C,根据这个逻辑表达式组成逻辑电路,则可能出现竞争冒险。我们可利用代数恒等式将L化为F=AC+B-C+AB,根据这个表达式组成逻辑电路就不会出现竞争冒险。

③输出端并联电容器

如果逻辑电路在较慢的速度下工作,为了消除竞争冒险现象,可以在输出端并联一个电容器,其容量为4~20pF之间,它对于很窄的负跳变脉冲起到平波的作用,这时在输出端就不会出现逻辑错误。

2.在CPLD中模拟竞争冒险的产生

图6-165 竞争冒险原理图

由于普通门电路的传输时延只有几十个纳秒,而且竞争冒险产生的脉冲很窄,用普通的示波器无法看清楚,要看到竞争冒险现象,就需要精度很高的示波器。如果用普通的硬件电路做的话,由于电路的分布电容和其他干扰,使得本来就很窄的脉冲被积分掉了,考虑到一般情况,我们采用可编程逻辑器件来做此实验。其原理图如图6-165所示。

要做此实验就要使用可编程逻辑器件及其相关软件。这方面的知识可以参照本实验指导书的可编程逻辑器件实验部分。在此我们使用MAX+plus II软件的仿真功能,来观察使用D触发器做分频时产生的竞争冒险现象。需要说明的是,在本实验中我们没有做基本门电路产生的竞争冒险。我们做的是组合逻辑电路使用时产生的竞争冒险。它们的原理都相似,都是由于器件的时延引起的,都会造成一定的危害。

图6-166 仿真分析

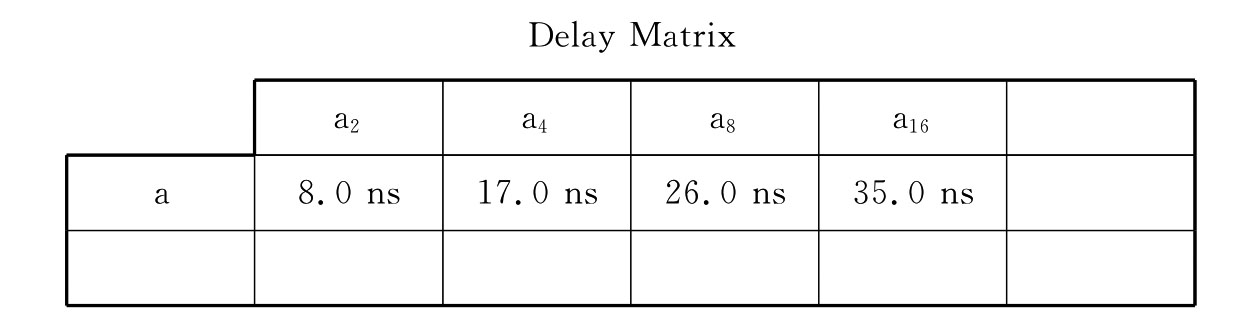

从仿真分析中能清楚地看到,在2分频,4分频,8分频,16分频时,都有一定的传输时延,虽然只有几个或十几个纳秒,但分频的次数比较多,就可能造成影响。图6-167是器件的传输时延分析图。

图6-167 传输时延分析

从传输时延分析图中我们可以看出,第一次分频即2分频时,有8纳秒的时延,第二次分频即4分频时有17纳秒的时延,第三次分频即8分频时有26纳秒的时延,第四次分频即16分频时有35纳秒的时延。这样如果有很多级的分频,时延就会更多。

由以上分析可知,竞争冒险产生的原因是D触发器分频引起的时延,如何消除这种竞争冒险呢?我们采用同步触发的方式就可以消除。因为在上面的原理图中,我们采用的是异步触发的方式,即每一个触发器都是单独翻转的。如果采用所有的触发器同时翻转就可以消除这种竞争冒险。

三、实验步骤

1.运行MAX+plus II软件,学习其基本用法。

2.在MAX+plus II软件中按照图6-165输入原理图,并编译,下载。

3.使用MAX+plus II软件的仿真功能,观察分频时的延时。

4.使用MAX+plus II软件的时序分析功能,观察各级分频之间的时延。

四、实验报告要求

1.在MAX+plus II软件中观察实验现象,并找出产生这种现象的原因。

2.通过本实验,你对竞争冒险有什么样的认识?并写一篇学习报告。

3.思考:将原理图进行管脚分配,输入一定频率的波形,你能观察到什么实验现象?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。