2.2.4 数字多级交换网络

当交换网络的容量增大时,只有T接线器就不能满足要求了,要扩大容量需要用S接线器配合T接线器组成多级交换网络。

1.TST交换网络

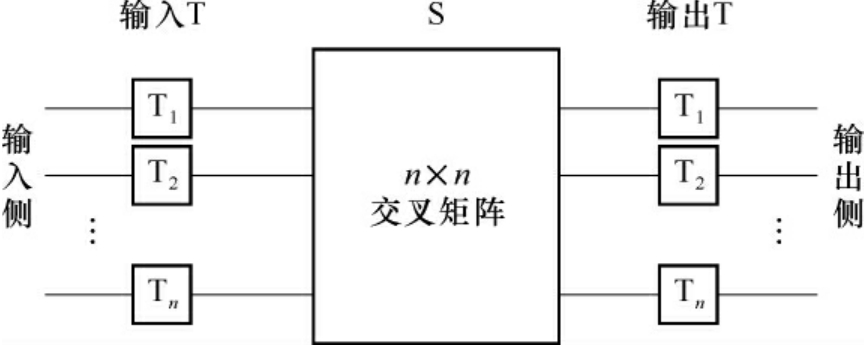

TST交换网络是3级交换网络,由输入T级(TA)、输出T级(TB)和中间的S接线器组成,如图2.20所示。其中S接线器的输入复用线和输出复用线的数量取决于两侧T接线器的数量,如每侧有8个T接线器,则S级采用8×8交叉矩阵。

图2.20 典型的TST交换网络结构

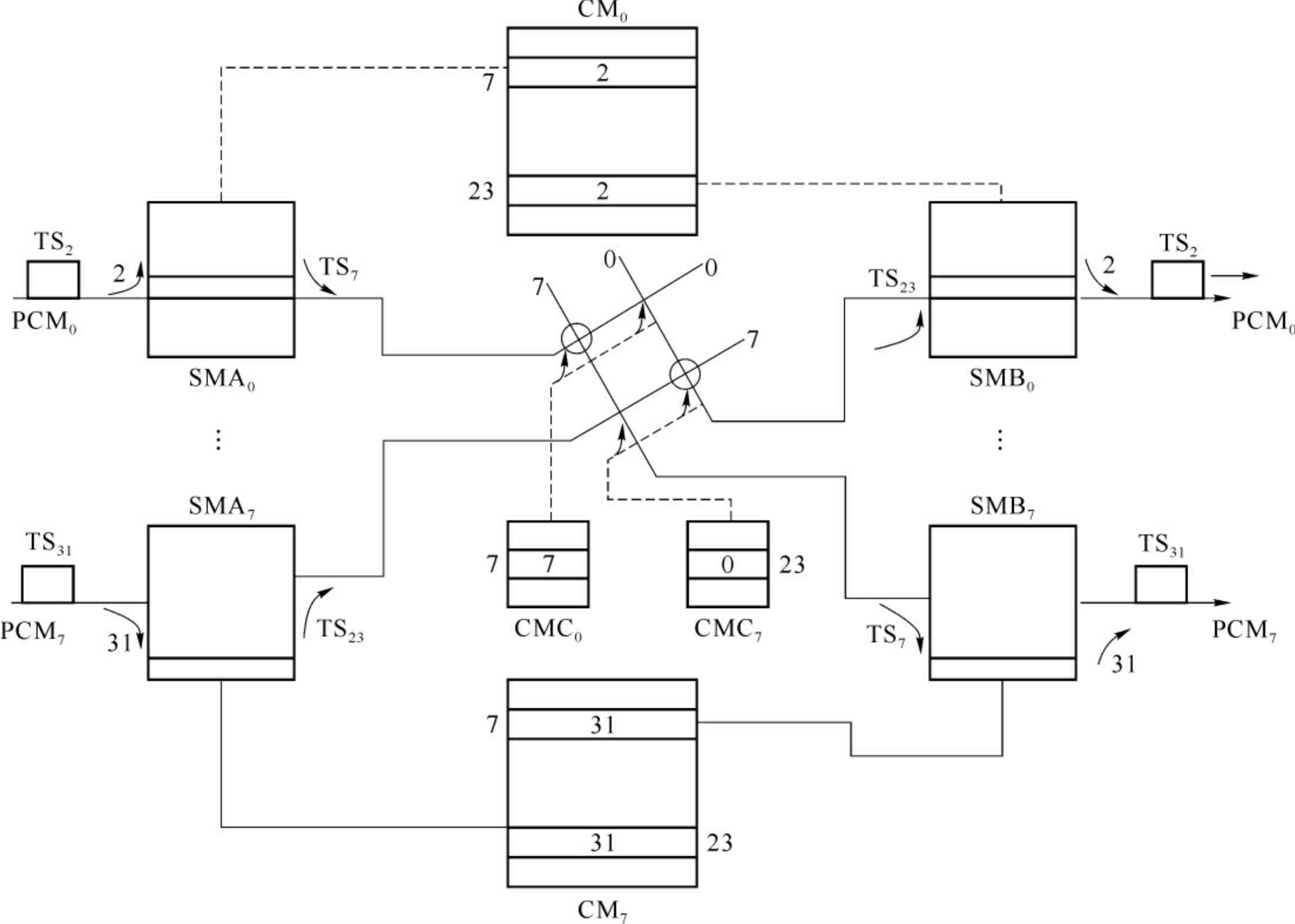

下面以图2.21为例说明TST交换网络的工作原理。其中输入T接线器采用输出控制方式,输出T接线器采用输入控制方式,S接线器采用输入控制方式。假设PCM0上TS2的A用户与PCM7上TS31的B用户通话。需要注意,用户间通话为双向的,但交换网络只能单向传输,所以交换中的用户间通话应建立双向通路。

图2.21 TST交换网络

(1)A→B方向:即PCM0上TS2中的话音编码信息交换到PCM7上TS31中去。首先PCM0上TS2中用户A的话音信息顺序写入输入T接线器的话音存储器的2单元,处理机为此次接续寻找一空闲内部时隙,现假设找到的空闲时隙为TS7,则处理机控制话音存储器2单元中的话音信息在TS7读出,则TS2的话音信息交换到了TS7,这样输入T接线器完成了TS2→TS7的时隙交换。然后S接线器在TS7将入线PCM0和出线PCM7接通(即TS7时刻闭合交叉点),使入线PCM0上的TS7交换到PCM7上。最后输出T接线器在控制存储器的控制下,将内部时隙TS7中的话音信息写入其话音存储器的31单元,输出时在TS31时刻顺序读出,这样输出T接线器完成了TS7→TS31的时隙交换。

此时,经过TST交换网络,输入PCM0上TS2中A用户的话音信息就交换到输出PCM7上TS31中,实现了A→B方向的通话。

(2)B→A方向:即PCM7上TS31中的话音编码信息交换到PCM0上TS2中去。首先PCM7上TS31中用户B的话音信息顺序写入输入T接线器的话音存储器的31单元,处理机为此次接续寻找一空闲内部时隙TS23(TS23由反相法确定),则处理机控制话音存储器31单元中的话音信息在TS23读出,则TS31的话音信息交换到了TS23,这样输入T接线器完成了TS31→TS23的时隙交换。然后S接线器在TS23将入线PCM7和出线PCM0接通(即TS23时刻闭合交叉点),使入线PCM7上的TS23交换到PCM0上。最后输出T接线器在控制存储器的控制下,将内部时隙TS23中的话音信息写入其话音存储器的2单元,输出时在TS2时刻顺序读出,这样输出T接线器完成了TS31→TS2的时隙交换。

此时,经过TST交换网络,输入PCM7上TS31中B用户的话音信息就交换到输出PCM0上TS2中,实现了B→A方向的通话。

对于内部时隙的选取通常采用反相法,即两个方向相差半帧。如本例中一条复用线上的时隙数为32,即帧长为32,则半帧为16个时隙,A→B方向选定TS7,则B→A方向就选定了16+7=23即TS23,这样,使处理机可以一次选择两个方向的路由,避免处理机的二次路由选择,从而减轻了处理机的负担。

2.单T级交换网络

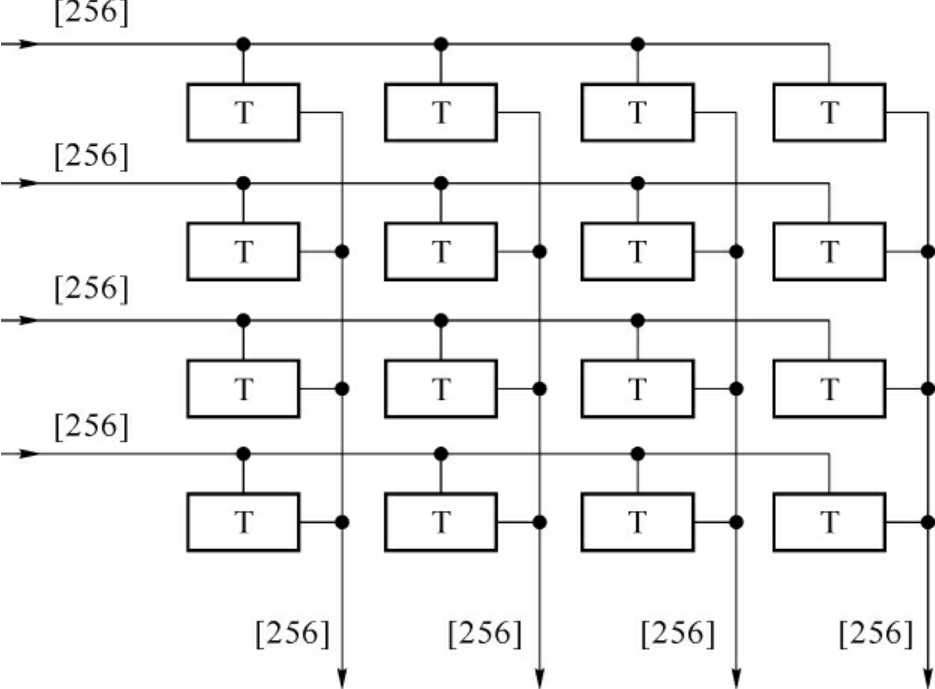

随着数字交换机的发展,出现了各种用于组成数字交换网络的集成芯片。芯片的容量从最早128×128时隙、256×256时隙逐渐发展到16k×16k时隙甚至更大。从交换网络的结构来看,S接线器集成度较低,所以当前主要采用T接线器集成芯片组成数字交换网络。

图2.22为一个256×256时隙数字接线器芯片的内部结构原理。在输入端“串/并”转换电路将串行信号变成并行信号,然后进入话音存储器进行交换;在输出端“并/串”转换电路将其复原成串行码,然后输出。

图2.22 256×256时隙数字接线器芯片内部结构

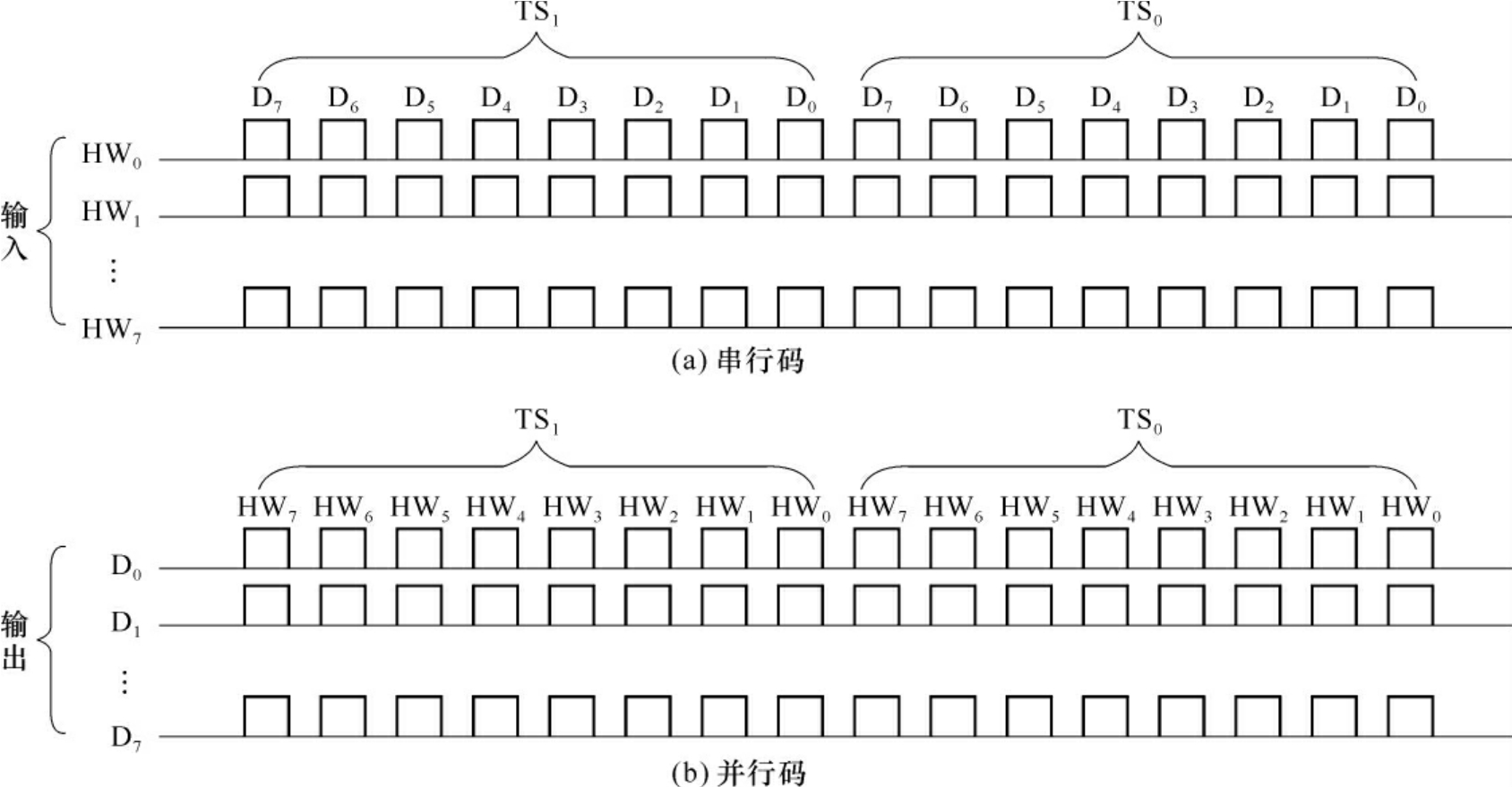

(1)串/并转换电路将输入时分复用线上到达的串行码流按照时隙分割变换为8位的8线并行码,如图2.23所示,然后经合路器把8个PCM(一个PCM称为一个HW)的并行码,按一定的次序进行排列,一个一个地送到话音存储器。这样做的目的是为了便于对存储器的操作与提高读写速度。需要注意的是,经过串/并转换后,线速降低到原来串行码的1/8,但时隙间隔时间保持不变(仍为约3.9μs)。

其中串行码是指各时隙内的8位码D0~D7是按时间的顺序依次排列,如图2.24(a)所示。并行码是指各时隙内的8位码D0~D7分别同时出现在8条线上,如图2.24(b)所示。

图2.23 串/并转换电路

图2.24 8端输入的串行码和并行码

(2)并/串转换电路的功能与串/并转换电路正好相反。

(3)2选1电路用于选择输出端是话音存储器内容还是控制存储器内容。

(4)话音存储器由控制存储器控制,它们所需要的定时信号由时基电路产生。

(5)CPU通过数据线D0~D7来控制芯片工作。它可以通过各种指令使得芯片8条PCM线的每个“交叉点”接通或释放。256×256交换网络芯片的交换速率为2Mbit/s。

3.TTT交换网络

通过多个T单元的复接,可以扩展T接线器的容量。如利用16个256×256的T接线器,可以得到一个1 024×1 024的T接线器,如图2.25所示。但由于采用这种方式扩展单级T交换网络所需T单元电路的数量按照(扩展的容量/单个T单元的容量)2增长,所以当交换网络容量很大时,就不经济了,这时可采用TTT三级网络。

图2.25 T单元的扩展

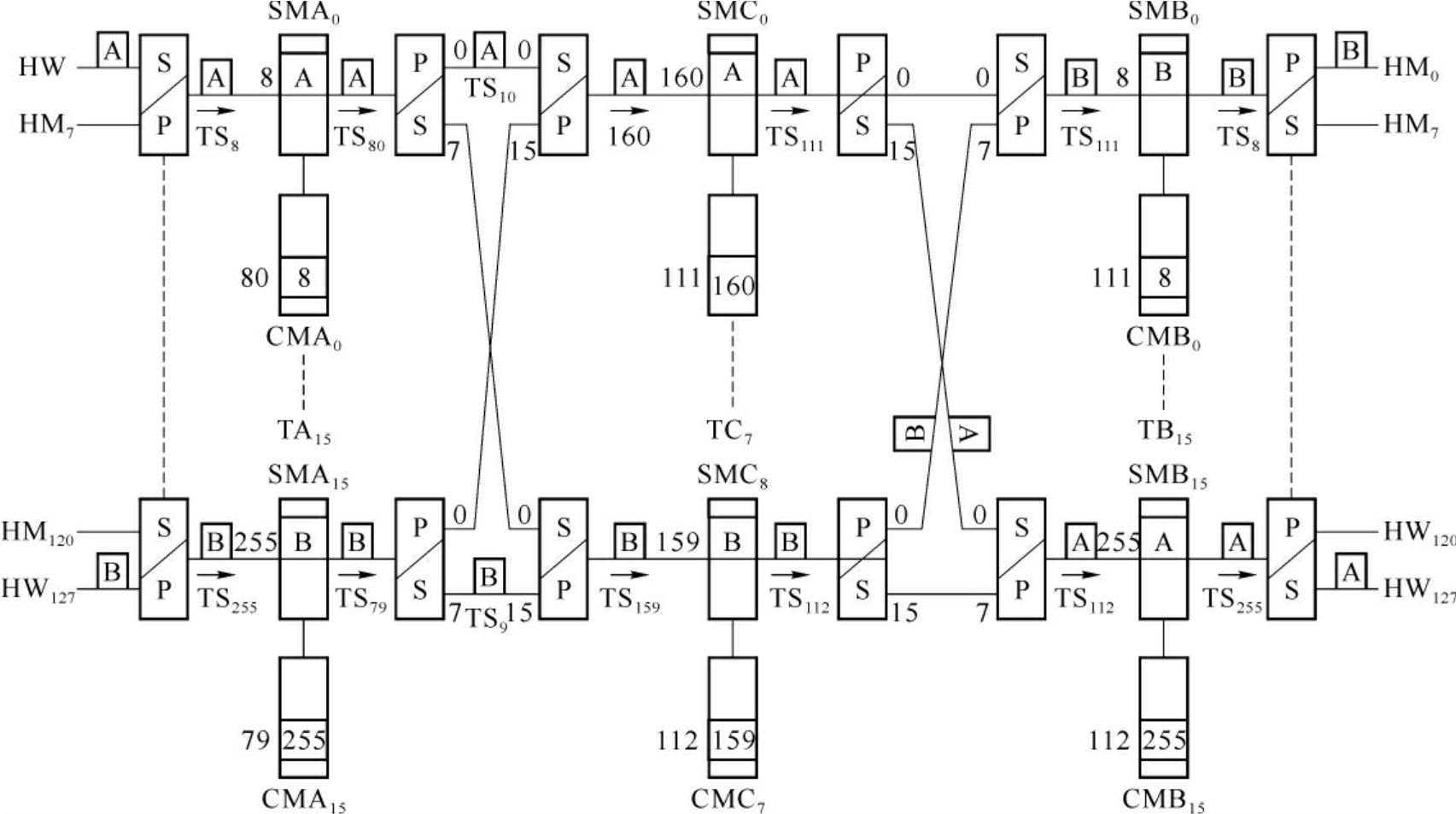

TTT 3级交换网络的结构如图2.26所示。它由输入TA级、中间TC级和输出TB级3级组成,输入端和输出端各有128条HW(HW0~HW127)。T接线器的容量均采用256个单元话音存储器和控制存储器,TA级和TC级采用输出控制方式,TB级采用输入控制方式。TA级和TB级各有16个T接线器(TA0~TA15、TB0~TB15),中间TC级有8个T接线器(TC0~TC7)。每个输入/输出HW有32个时隙、128个HW,共有128×32=4 096个时隙。设A用户在这次呼叫中占用HW0的TS8,B用户占用HW127的TS31,图中给出了这两个用户通过TTT交换网络交换信息的过程。A→B方向的内部链路选定TS80和TS111,B→A方向的内部链路选定TS79和TS112。

图2.26 TTT 3级交换网络的结构

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。