任务一 设计计算机串行口封装

一、任务介绍

图2-12 计算机串行通信接口

计算机串行通信接口如图2-12所示,应用ISP下载线可将计算机串行口与计算机连接起来。该接口实际应用时有两种安装方式,一种安装方式是将其25针引脚插入印制电路板相应焊盘内,其封装为插针式封装,如图2-13所示,该封装由系统库提供。另一种安装方式是将印制电路板夹在串行接口器件两排引脚间,其封装采用贴片方式,如图2-14所示,该封装需要自行设计。

图2-13 串行口插针式封装

图2-14 串行口贴片式封装

二、任务分析

封装设计最好的方式是用最简单的方法达到设计要求。由于串口封装有25个引脚,数量较多,如果完全重新绘制,在保障引脚间距参数的情况下工作量较大。通过对比两个封装,由于引脚间距是不变的,可以采取通过修改串行口插针式封装的方法设计串行口贴片式封装。

三、相关知识

前面设计“三极管放大器.PCB”时,电路涉及的元件封装均来自Protel 99 SE系统自带的封装库文件“Advpcb.ddb”。尽管系统自带了很多元件封装库,并适时更新,但由于电子技术的迅猛发展,元件库的更新速度仍落后电子元件的发展更新速度。特别是大量非标准元件的使用,更难以在系统提供的库中找到合适的封装。因此,对于PCB设计人员,制作元件封装是一项必备的技能。

制作元件封装应注意以下事项:

(1)元件封装引脚编号应与电路原理图中对应的元件引脚编号相同,以保证正确的电气连接关系。

(2)元件封装焊盘的规格与相互间距应与实际元件引脚相符,以保证元件能恰好安装在PCB上。

(3)元件封装的外形轮廓,要与实际元件的轮廓大小一致。如果元件的外形轮廓画得太大,会浪费PCB的空间;如果画得太小,元件可能无法安装。

(4)应准确获取元件的具体封装信息。封装信息主要来源于元器件生产厂家提供的用户手册。若没有所需元器件的用户手册,可以上网查找元器件信息,通常可在元件厂商或供应商的网站获得相应信息,也可以在www.21ic.com等电子网站上查询。如果有些元件找不到相关资料,则只能依靠实际测量,一般要配备游标卡尺,测量时要准确,特别是集成块的引脚间距。

制作封装有3种方法:修改法、手工绘制法、向导绘制法。

四、任务实施

1.启动元件封装库编辑器

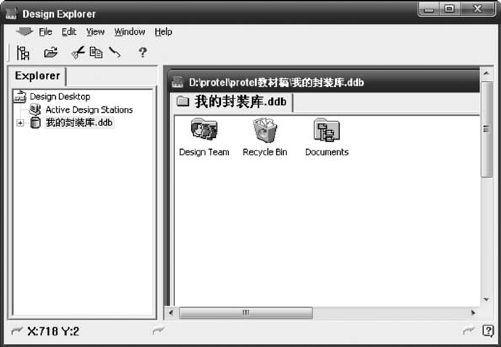

进入Protel 99 SE,新建“我的封装库.ddb”文件,如图2-15所示。

执行菜单命令【File】/【New】(或单击鼠标右键,在出现的对话框菜单中再单击【New】),再在系统弹出的对话框中双击图标 ,新建元件封装库,系统默认名为“PCBLIB1.LIB”,可将其修改为自己需要的名称,如“mypcb.lib”,用鼠标双击“mypcb.lib”文件,可以打开元件封装库编辑器,进入图2-16所示的元件封装库编辑器界面。

,新建元件封装库,系统默认名为“PCBLIB1.LIB”,可将其修改为自己需要的名称,如“mypcb.lib”,用鼠标双击“mypcb.lib”文件,可以打开元件封装库编辑器,进入图2-16所示的元件封装库编辑器界面。

图2-15 新建“我的封装库.ddb”

图2-16 元件封装库编辑器

元件封装库编辑器主要由元件封装库管理器、主工具栏、菜单、绘图工具栏、编辑区等组成。

(1)主菜单。主菜单主要是给设计人员提供编辑、绘图命令,以便于创建一个新元件。

(2)主工具栏。主工具栏为用户提供了各种图标操作方式,可以让用户方便、快捷地执行命令和各项功能。如打印、存盘等操作均可以由主工具栏实现。

(3)绘图工具栏。绘图工具栏的作用类似于菜单命令“Place”,是在工作平面上放置各种图元,如焊点、线段、圆弧等。

(4)元件封装库管理器。元件封装库管理器主要用于对元件进行管理。

(5)状态栏与命令行。在屏幕的最下方为状态栏和命令行,它们用于提示用户系统当前的状态和正在执行的命令。

2.修改串行口插针式封装为贴片式封装

(1)进入元件库编辑器后,执行菜单命令【Tools】/【New Component】,屏幕弹出元件设计向导,单击“Cancel”按钮,进入手工设计状态。

(2)执行菜单命令【Tools】/【Library Options】,系统弹出设置文档参数对话框,在“Layer”选项卡中,将可视栅格1设置为40 mil,可视栅格2设置为2 000 mil(默认值);单击“Option”标签,进入“Option”选项卡,设置捕获栅格为5 mil。

(3)在“我的封装库.ddb”中新建一PCB文件,默认名为“PCB1.PCB”,打开该文件,如图2-17所示。

图2-17 新建一PCB文件

(4)在编辑器左边单击“Browse”下拉列表框下拉按钮,选择“Libraries”项,并在“Components”元件封装浏览器中查找到“DB25/F”元件封装,如图2-18所示。

(5)单击“Edit”按钮,编辑该元件封装,如图2-19所示。

(6)复制该元件封装。执行菜单命令【Edit】/【Select】/【All】或利用主工具栏上的框选按钮 ,选中该封装(选中状态元件呈黄色);执行菜单命令【Edit】/【Copy】,光标呈十字形状,移动光标到元件上单击鼠标左键,将元件复制到粘贴板。

,选中该封装(选中状态元件呈黄色);执行菜单命令【Edit】/【Copy】,光标呈十字形状,移动光标到元件上单击鼠标左键,将元件复制到粘贴板。

图2-18 查找“DB25/F”元件封装

图2-19 编辑“DB25/F”元件封装

(7)进入元件封装编辑器,单击主工具栏上的粘贴按钮 ,将元件复制到编辑器中,单击主工具栏上的取消选中按钮

,将元件复制到编辑器中,单击主工具栏上的取消选中按钮 ,取消元件选中状态,如图2-20所示。

,取消元件选中状态,如图2-20所示。

图2-20 将“DB25/F”元件复制到元件封装编辑器中

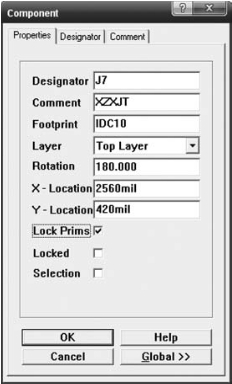

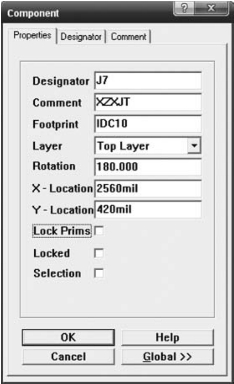

(8)修改焊盘设置属性。双击焊盘1,得到如图2-21所示的原焊盘属性设置对话框,修改焊盘大小后,如图2-22所示。修改后焊盘属性为:X-Size:78 mil;Y-Size:180 mil; Hole Size:0 mil(贴片式封装无须焊孔);Layer:TopLayer(焊盘由多层变为只在顶层);其他不变。

图2-21 原焊盘属性设置对话框

图2-22 修改后焊盘属性设置对话框

(9)在图2-22中,单击“Global>>”(全局设置)按钮,弹出如图2-23所示界面。单击“OK”按钮后,弹出确认对话框,如图2-24所示。单击“Yes”按钮确认后,所有焊盘均设置为与焊盘1相同的属性。修改焊盘属性后封装如图2-25所示。图中所有焊盘均呈红色,表明焊盘均在PCB顶层(手工绘制贴片元件封装与前面介绍的手工绘制元件封装相同,只需将焊盘设置在顶层即可)。

图2-23 全局修改焊盘属性

图2-24 全局修改确认对话框

(10)修改焊盘层。计算机串行口在进行贴片焊接时,1~13引脚在顶层,14~25引脚在底层,故需进行焊盘层属性修改。双击图2-25中焊盘14引脚,将层属性由“TopLayer”(顶层)修改为“BottomLayer”(底层),单击“OK”按钮后表示完成了修改。依次修改其他焊盘属性,修改后封装如图2-26所示。由于教材为黑白显示,图2-25与图2-26相同,实际工作时,修改后,14~25引脚焊盘呈蓝色。

(11)修改底层焊盘位置。利用主工具栏上的框选按钮 选中全部底层焊盘,将其整体移动后,再利用主工具栏上的取消选中按钮

选中全部底层焊盘,将其整体移动后,再利用主工具栏上的取消选中按钮 取消底层焊盘选中状态,得到图2-27所示的封装。

取消底层焊盘选中状态,得到图2-27所示的封装。

图2-25 全局修改焊盘属性后的元件封装

图2-26 修改部分焊盘层属性后的元件封装

图2-27 移动底层焊盘位置

(12)删去原封装安装孔,修改封装边框,将元件名称修改为MYDB25,保存该元件。最后完成该元件封装,如图2-28所示。

图2-28 计算机串行口封装

五、拓展提高——编辑库元件封装

Protel 99 SE系统提供了很多元件封装库,实际应用时,如果某个元件封装与实际需要有出入,除可以采用前面介绍的方法绘制元件封装外,也可以对系统已有的元件封装属性进行修改,使之符合要求。

若要修改元件封装库中的某个元件,先进入元件库编辑器,执行菜单命令【File】/【Open】,打开要编辑的元件库,在元件浏览器中选中要编辑的元件,窗口就会显示出此元件的封装图,若要修改元件封装的焊盘,用鼠标左键双击要修改的焊盘,出现此引脚焊盘的属性对话框,在对话框中就可以修改引脚焊盘的编号、形状、直径、钻孔直径等参数;若要修改元件外形,可以用鼠标点取某一条轮廓线,再次单击它的非控点部分,移动鼠标,即可改变其轮廓线的位置,或者删除原来的轮廓线,重新绘制新的轮廓线。元件修改后,执行菜单命令【File】/【Save】,将结果保存。

修改元件封装库的结果不会反映在以前绘制的印制电路板图中。如果按下PCB元件库编辑器上的“Update PCB”按钮,系统就会用修改后的元件更新印制电路板图中的同名元件。

采用此种方法修改元件封装的不足之处是系统提供的元件封装库已被修改。

绘制PCB时,若发现所采用的元件封装不符合要求,则需要加以修改,可以不退出PCB界面,直接进行修改。方法是:在元件浏览器中选中该元件,单击“Edit”按钮,系统自动进入元件编辑状态,其后的操作与上面相同。

实际设计电路时,在原理图中二极管元件引脚定义为1、2,如图2-29所示(在元件属性对话框中选中“Hidden Pins”复选框,即可看到引脚名称),而在封装中定义为A、K,如图2-30所示,两者不一致。此时可以通过编辑元件封装的方法,将焊盘由A、K修改为1、2。实际上也可以通过修改元件符号的方法,将原理图中元件引脚由1、2修改为A、K。

![]()

图2-29 原理中二极管元件

![]()

图2-30 二极管元件封装

六、思考与练习

1.制作元件封装应注意什么问题?

2.绘制如图2-31所示的元件封装(相邻引脚间距为100 mil,两列引脚间距为300 mil)。

图2-31 元件封装

任务二 设计ISP下载线PCB

一、任务介绍

本任务是完成下载线PCB设计。采用双面PCB设计方法,可以实现PCB小型化,但由于PCB较小,所以元件布局需要认真仔细,避免发生违规无法布线问题。本设计采用贴片元件,也是为了实现PCB的小型化。

二、任务分析

本任务主要完成3个操作:规划PCB、元件布局、PCB布线。由于线路较简单,采取自动布线的方式,只要元件布局合理,PCB布线可以顺利完成。

三、任务实施

1.规划印制电路板

新建“下载线电路.PCB”文件,并采取手工方式规划印制电路板,如图2-32所示,具体尺寸应根据下载线外壳结构设计。

图2-32 规划印制电路板

2.装载元件库

由于在电路设计时要使用到自绘封装,故需装载“我的封装库.ddb”。

3.装载网络表

执行菜单命令【Design】/【Load Nets】,装载“下载线电路.NET”网络表,装载成功后,如图2-33所示。

图2-33 装载网络表

4.元件布局

在图2-33中,各元件分散摆放在印制电路板框外,需手工进行元件布局,如图2-34所示。

实际设计电路时,J7并没有使用专业下载线连接器,而是用导线直接焊接在相应焊盘上,故可对封装进行在线修改。在线修改元件封装过程如下:

鼠标左键双击J7元件封装,弹出如图2-35所示的元件对话框。取消“Lock Prims”复选框,解除元件封装锁定状态,如图2-36所示,此时可以对封装进行修改。由图2-2下载线电路原理图中发现:J7中3引脚为空脚,故可将相应焊盘去除;4、6、8、10引脚均接地,故只保留一个焊盘即可,焊接时将4根地线焊到一个地线焊盘;删去原封装边框,修改J7封装后元件布局如图2-37所示,图中另加了两个焊盘作为安装孔。

图2-34 元件布局

图2-35 元件属性对话框

图2-36 解除元件封装锁定

图2-37 修改J7封装后的元件布局

5.设置布线规则

(1)“Clearance Constraint”(安全间距):设置为15 mil。

(2)“Routing Corners”(拐弯方式):取默认设置。

(3)“Routing Layers”(布线层):系统默认为双层板,故可取默认设置,设置“Top Layer”为“Horizontal”(顶层水平布线),“Bottom Layer”为“Vertical”(底层垂直布线),其他层为“Not Used”(不使用)。

(4)“Routing Via Style”(过孔类型):取默认设置。

(5)“SMD Neck-Down Constraint”(SMD焊盘与导线的比例):此规则用于设置SMD焊盘在连接导线处的焊盘宽度与导线宽度的比例,可定义一个百分比,取默认设置。

(6)“SMD To Corner Constraint”(SMD焊盘与拐角处的最小间距):此规则用于设置SMD焊盘与导线拐角的间距大小,取默认设置。

(7)“SMD To Plane Constraint”(SMD焊盘与电源层过孔间的最小长度):此规则用于设置SMD焊盘与电源层中过孔间的最短布线长度,取默认设置。

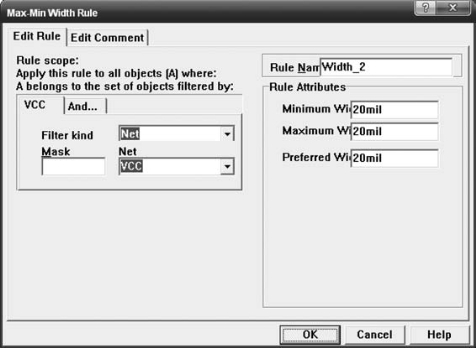

(8)设置导线宽度,如图2-38所示。

在设计管理器的“Browse”下拉列表框中,选择“Rules”,设置浏览器为规则浏览器,并选择“Width Constraint”,如图2-39所示。图中显示了PCB导线宽度设计规则。

单击“Edit”按钮,可以编辑(修改)相应设计规则,如图2-40所示。

6.自动布线

执行菜单命令【Auto Route】/【All】,进行自动布线。自动布线成功后得到图2-41。如果认为布线不合适,可重新调整元件布局或进行手工布线调整等。

图2-38 设置导线宽度

图2-39 利用浏览器显示设计规则

图2-40 编辑设计规则

图2-41 自动布线

7.补泪滴

执行菜单命令【Tools】/【Teardrops】,屏幕弹出设置对话框,在此取默认设置,完成后PCB如图2-42所示。

单击PCB浏览器下方的“Magnifier”按钮,可以在监视器中放大显示工作区中指定的内容,如图2-43所示。此种方法适合查看大型复杂电路的局部电路设计。

图2-42 补泪滴

图2-43 利用监视窗口查看局部电路

8.放置铺铜

本电路采取双面铺铜。

单击编辑器下面的“Bottom Layer”,选择底层印制电路板。

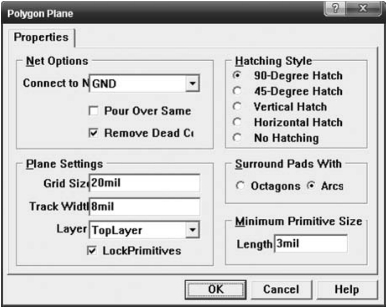

执行菜单命令【Place】/【Polygon Plane】,或单击放置工具栏上的按钮 ,屏幕弹出放置多边形铺铜设置对话框,设置铺铜与地线(GND)相连,如图2-44所示。

,屏幕弹出放置多边形铺铜设置对话框,设置铺铜与地线(GND)相连,如图2-44所示。

图2-44 铺铜设置

利用鼠标划定铺铜区域后完成铺铜,如图2-45所示。

图2-45 底层铺铜

单击编辑器下面的“Top Layer”,选择顶层印制电路板,完成顶层铺铜,如图2-46所示。

图2-46 顶层铺铜

四、拓展与提高——设计规则检查

印制电路板布线完成后,设计者可以利用设计规则检查功能检查印制电路板是否符合前面的设计规则以及布线是否正确。设计规则检查有报表输出(Report)和在线检测(Online)两种方式。

执行菜单命令【Tools】/【Design Rule Check】,屏幕出现图2-47所示的对话框,有两个选项卡,分别用于报表输出方式(Report)和在线检测方式(On-line)。

(1)报表输出方式(Report)。图2-47所示为“Report”选项卡,可以设置检查项目。

其中“Routing Rules”“Manufacturing Rules”和“High Speed Rules”三区分别列出了与布线、制作及高速电路有关的规则,若需要利用某个规则作检查,则选取相应的复选框。在进行DRC检查前,必须在执行菜单命令【Design】/【Rules】中设置好要检查的设计规则,这样在DRC检查时才能被选中。按下“Run DRC”按钮,开始进行DRC检查,检查完毕后,将给出一个检查报告。下面为图2-42中“下载线电路.PCB”(未铺铜时)的检查报告。

Protel Design System Design Rule Check

PCB File:Documents\下载线电路.PCB

Date :1-Jan-2000

Time :05:24:28

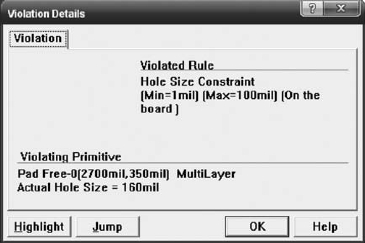

Processing Rule:Hole Size Constraint(Min=1 mil)(Max=100 mil)(On the board)

图2-47 设计规则检查对话框

(规则中焊盘最大孔径为100 mil,见图2-48中设置)

Violation Pad Free-0(2700mil,350mil) MultiLayer Actual Hole Size=160mil

Violation Pad Free-0(2040 mil,345 mil) MultiLayer Actual Hole Size=160mil

Rule Violations:2(检测到2个违规:两个安装孔焊盘实际孔径达160 mil,违反规则)

Processing Rule:Width Constraint(Min=20 mil)(Max=20 mil)(Preferred=20 mil)(Is on net VCC)

Rule Violations:0

Processing Rule:Width Constraint(Min=20 mil)(Max=20 mil)(Preferred=20 mil)(Is on net GND)

Rule Violations:0

Processing Rule:Width Constraint(Min=10 mil)(Max=10 mil)(Preferred=10 mil)(On the board)

Rule Violations:0

Processing Rule:Clearance Constraint(Gap=10 mil)(On the board),(On the board)

Rule Violations:0

Processing Rule:Short-Circuit Constraint(Allowed=Not Allowed)(On the board),(On the board)

Rule Violations:0

Processing Rule:Broken-Net Constraint(On the board)

Rule Violations:0

Processing Rule:Width Constraint(Min=20 mil)(Max=20 mil)(Preferred=20 mil)(Is on net VDD)

Rule Violations:0

Violations Detected:2(检测到2处违规)

Time Elapsed :00:00:01

图2-48 孔径参数设置

本例中虽有两处设计规则违规,但这是设计者实际设计需要,故不必进行修改。

(2)在线检测方式(On-line)。执行菜单命令【Tools】/【Preferences】,在弹出的对话框中的“Editing options”区,选中“On-line DRC”复选框实现在线检测。设置在线检测后,在放置和移动图件时,程序自动根据规则进行检查,一旦发现违规,将高亮度显示违规内容。

(3)PCB中违规错误的浏览。DRC检查后,系统给出检查报告,违规的图件将高亮显示,此时利用违规浏览器可以方便地找到发生违规的位置及违规的具体内容。

在设计管理器的“Browse”下拉列表框中,选择“Violations”,设置浏览器为违规浏览器,如图2-49所示。

图2-49 进入违规浏览器

单击“Details”按钮,屏幕弹出对话框,如图2-50所示,详细说明了违规的具体内容,包括违反的规则、违规的图件名和图件位置。

图2-50 违规详细信息

单击“Jump”按钮,屏幕显示违规图件,如图2-51所示。

图2-51 显示违规图件

五、思考与练习

1.什么是双层印制电路板?简述双层印制电路板图设计的步骤。

2.在制作印制电路板图的过程中,通常都设置哪些自动布线设计规则?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。