集成运算放大器简称集成运放,它是20世纪60年代发展起来的一种高增益直接耦合放大器。集成运放配上不同的外围器件,可构成各种功能和特性完全不同的集成运放电路,简称运放电路。集成运放的应用日益广泛,它除了完成诸如加法、减法、微分、积分等各种数学运算外,还可以完成信号的产生、转换、处理等各项功能,因此,集成运算放大器已成为模拟系统的一个基本单元。在进行应用电路的制作时,必须对集成运放的引脚功能及其内部结构加以掌握,以确保设计电路的正常运行。

2.4.1 任务目标

(1)熟悉常见集成运放的型号及内部结构。

(2)熟悉集成运放的主要参数及主要引脚功能。

(3)理解集成运放的理想特性。

2.4.2 基础知识一

差分放大电路

多级放大电路的级间耦合方式通常有: 直接耦合、阻容耦合和变压器耦合。电子技术中常需要放大变化缓慢的、甚至是直流信号,放大这类信号不能采用阻容耦合或变压器耦合,只能用直接耦合方式。而且,近年来发展迅速的集成电路中,为了减少级间耦合元器件及降低耦合损耗,也都采用直接耦合放大器。

2.4.2.1 直接耦合放大器存在的问题

在多级放大电路中采用直接耦合存在两个特殊问题: 一是各级静态工作点相互影响,二是存在零点漂移。

零点漂移简称“零漂”,是指当输入信号为零时,放大器出现的输出端信号不为零的现象。零漂在RC耦合电路中影响不大,但在直接耦合放大电路中会被后级电路逐级放大,且第一级的零漂影响最为严重。产生零漂的原因有: 温度变化、元器件参数的变化、电源电压波动等,但最主要的因素是环境温度的变化,所以零漂也成温漂。

在电路结构上,目前抑制零漂最有效的方法是采用差分放大电路,它常用做集成运放的输入级。

2.4.2.2 差分放大电路

差分放大电路,简称差放,是集成运算放大器中常用的一种单元电路,具有优越的抑制零点漂移性能。基本差分放大电路如图2-4-1所示,该电路采用对称共射电路,电路中VT1与VT2称为差分对管,两边的元器件采用相同的温度特性和参数,使之具有很好的对称性。输入信号ui1与ui2从差分对管的两个基极输入,称为双端输入; 输出信号可以从两个集电极之间取出,称为双端输出,也可以从其中的任意一个集电极输出,此时称为单端输出。

图2-4-1 基本差分放大电路

1.抑制共模信号

由于差分放大电路两边完全对称,且两个晶体管参数完全相同,当输入信号电压为零时,ui1=ui2=0,uc1=uc2,uo=uc1-uc2=0,输出信号电压也为零。当由于温度变化引起两管的集电极电流发生变化时,两管的集电极电流变化量相等,因此Δuo=Δuc1-Δuc2=0,输出电压总是为零。由此可以看出,对称差分放大电路的温度漂移在理想情况下等于零,电路对零点漂移具有很好的抑制作用。

差分放大电路的零点漂移折算到输入端时,相当于在晶体管VT1和VT2的输入端加上大小相等、极性相同的输入漂移电压。通常把这种大小相等、极性相同的输入信号叫做共模信号。温度或电源波动引起的零点漂移,相当于在差分电路输入端引入了共模信号。

一个完全对称的差动放大器,其共模电压放大倍数为

2.放大差模信号

基本差分放大器的输入信号可以分为共模信号和差模信号两种。在放大器两输入端分别输入大小相等、极性相反的信号,这种信号称为差模信号,这种输入方式称为差模输入。

在差模输入情况下,因电路对称、参数相同,两管集电极电位的变化必定大小相等、极性相反。若某个晶体管电位升高Δuc,则另一个必降低Δuc。设两晶体管放大倍数均为A,集电极输出电压分别为uc1、uc2,则uc1=Aui1,uc2=Aui2=-Aui1,uc=uc1-uc2=2Aui1。差模电压放大倍数为

由此可以看出,电路放大倍数与单级放大电路相同。

3.共模抑制比

差分放大电路的优点能有效地放大差模信号,同时抑制共模信号。为了全面衡量一个放大电路质量的优劣,通常把差模放大倍数Ad与共模电压放大倍数Ac的比值称共模抑制比,用KCMR来表示。KCMR越大,差分放大电路放大差模信号(有用信号)的能力越强,抑制共模信号(无用信号)的能力也越强。理想情况下,共模抑制比KCMR趋于无穷大。一般差放电路的KCMR为40~60d B,高质量的可达120d B以上。

2.4.3 基础知识二

集成运放简介

1.集成运放的内部构成

集成运放电路主要由输入级、中间增益级、输出级和各级偏置电路等四部分组成,如图2-4-2所示,对于高性能、高精度等特殊集成运放,还要增加有关部分的单元电路。例如:温度控制电路、温度补偿电路、内部补偿电路、过流或过热保护电路、限流电路、稳压电路等。

图2-4-2 集成运放组成框图

①输入级: 运放输入级通常由差动放大电路构成,目的是为了减小放大电路的零点漂移、提高输入阻抗。

②中间级: 通常由共发射极放大电路构成,目的是为了获得较高的电压放大倍数。

③输出级: 一般由互补对称电路或准互补对称电路构成,目的是为了减小输出电阻,以提高运放的输出功率和带负载能力。

④偏置电路: 其作用是给各级电路提供所需的电源电压。

2.集成运放的表示符号及其引出端

①集成运放的表示符号

集成运放电路图形符号如图2-4-3所示。“▷”表示信号传输方向,“∞”表示开环增益极高。

图2-4-3 集成运放的图形符号

集成运放有两个输入端,一个输出端uo。其中“+”为同相输入端ui+,“-”为反相输入端ui-。

②集成运放的引出端

在实际应用中,集成运放有五类引出端,分别是: 两个输入端、一个输出端、电源端、调零端、相位补偿端,如图2-4-4所示。

图2-4-4 集成运放的引出端

3.集成运放的封装形式及管脚排列

从封装外形来分,主要有两类: 双列直插封装和金属圆帽封装,如图2-4-5所示。

图2-4-5 集成运放的封装形式及管脚排列

(a)双列直插封装引脚排列图; (b)金属圆帽封装引脚排列图

图2-4-6所示为集成运放常见的几种封装形式。

图2-4-6 不同封装外形的集成运放

μA741实物及引脚排列如图2-4-7所示。

4.集成运放的分类

①通用型按增益高低可分为:

·低增益(开环电压增益在60~80d B)的通用Ⅰ型。

·中增益(开环电压增益在80~100d B)的通用Ⅱ型。

图2-4-7 μA741实物及引脚排列图

(a)μA741实物图; (b)μA741引脚排列

·高增益(开环电压增益大于100d B)的通用Ⅲ型等。

②低输入偏置电流、高输入阻抗型: 偏置电流一般为0.1p A~50p A,其输入阻抗一般为1012~1014Ω。输入阻抗在1000GΩ以上的有μA740、μPC152、8007等。国内产品5G28的输入阻抗大于10GΩ,F3103的输入阻抗达到1000GΩ。

③高速型和宽频带型: 具有快速跟踪输入信号电压能力的集成运放。主要产品有F715、F722、4E321、F318、μA207等。其中,国产的F715的转换速率达到100V/μs,F318的转换速率达到70V/μs,国外的μA207的转换速率达到500V/μs,个别产品已达到1000V/μs。

④高压型: 工作电源电压越高,输出电压的动态范围越宽。一般电源电压在±20V以上者称为高压型集成运放。国内高压运放有F1536、BG315、F143等。

⑤高输出电流型和功率型: 当输出电流在50m A以上者称为高输出电流型; 输出电流在1A以上者通常称为功率型集成运放。主要产品有F3401、MC3401、LM3900等。

⑥低噪声型: 一般等效输入电压在2 V以下者为低噪声型。这类产品有F5037、XFC88等。

⑦多元型: 多元集成运放也叫复合集成运放,它是在一个芯片上同时集成2个或2个以上独立的集成运放。主要产品有F747、F1437、F1537、F1558、F347、F4558、XFC80、BG320、5G353等。

⑧单电源型: 主要产品有F3140、F124、F158、F358、7XC348等。

5.集成运放的主要参数

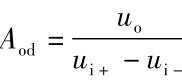

①开环差模增益Aod。指集成运放本身的差模增益,即 。它体现了集成运放的电压放大能力,一般在104~107之间。

。它体现了集成运放的电压放大能力,一般在104~107之间。

②开环共模增益Aoc。指集成运放本身的共模增益,它反映集成运放抗温漂、抗共模干扰的能力,优质的集成运放Aoc应接近于零。

③共模抑制比KCMR。用来综合衡量集成运放的放大能力和抗温漂、抗共模干扰的能力,一般应大于80d B。

④差模输入电阻Rid。指差模信号作用下集成运放的输入电阻。

⑤输入失调电压Uio。指为使输出电压为零,在输入级所加的补偿电压值。

6.集成运放的理想特性

在分析运放的各种实用电路时,为了简化问题的分析,通常将运放看成为理想运放。

(1)理想运放的条件

①开环差模放大倍数趋于无穷大,即Aod=∞。

②两输入端之间的输入电阻趋于无穷大,即Rid=∞。

③输出电阻为零,即Ro=0。

④共模抑制比趋于无穷大,即KCMR=∞。

⑤漂移为零。

(2)理想运放的特点

理想运放工作区域有两个,即线性工作区和非线性工作区。

工作在线性放大状态的理想运放具有两个重要特点:

①虚断: 由Rid=∞,得i+=i-=0,即理想运放两个输入端的输入电流为零。

②虚短: 由Aod=∞,得ui+=ui-,即理想运放两个输入端的电位相等。

2.4.4 操作指导

集成运放在电路的使用时,必须注意以下各点:

(1)集成运放的管脚排列次序有一定的规律,一般是从外壳顶部向下看,从左下脚按逆时针方向读数,其中第一脚附近一般有参考标志,如凹槽、色点等。

(2)根据电路要求对集成运放的型号、性能参数做出正确的选择。

(3)使用集成运放器件之前对相关引脚的功能进行确定,确保电源端、输入端、输出端接线正确。

(4)注意集成运放输入、输出、电源极性的保护。

2.4.5 技能实训

集成运放的识读与检测

2.4.5.1 实训目的

(1)学会借助资料读懂集成运放的型号,明确各引脚的功能。

(2)会用电阻测试法检测集成运放。

2.4.5.2 实训器材

(1)万用表(MF-47型1只)。

(2)集成运放产品(F007、CF224、CF741、CF747、LM358、μA741)。

2.4.5.3 实训步骤与内容

(1)查阅资料,识读集成运放的型号。

(2)查阅资料,识读集成运放的引脚,填写表2-4-1。

表2-4-1 集成运放的引脚号及引脚功能

(3)画出μA741、CF747的引脚排列示意图,完成图2-4-8。

图2-4-8 集成运放的引脚排列示意图

(4)选择CF224,采用电阻测试法测量各引脚相对于接地引脚的正、反向电阻。查资料确定接地引脚为 ,然后填写表2-4-2。

表2-4-2 CF224的各脚对地的正、反向电阻值

2.4.5.4 实训注意事项

(1)电源、接地引脚确定。

(2)万用表的欧姆挡不宜选低,亦不宜选高。

(3)测量时,手不要碰及引脚,以免人体电阻的介入影响到测量的准确程度。

2.4.5.5 实训考核

集成运放的识读与检测实训考核评价如表2-4-3所示。

表2-4-3 实训考核评价表

注: 各项配分扣完为止。

2.4.5.6 实训思考

为什么在用电阻测试法对集成运放进行检测的时候,万用表欧姆挡的倍率不宜选R×1和R×10k?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。