实验七 集成逻辑电路的连接和驱动

一、实验目的

1.了解TTL门电路的输出特性。

2.了解CMOS门电路的输出特性。

3.掌握集成逻辑电路相互衔接时应遵守的规则和实际衔接方法。

二、实验原理

1.TTL电路输入输出电路性质

当输入端为高电平时,输入电流是反向二极管的漏电流,电流极小。其方向是从外部流入输入端。当输入端处于低电平时,电流由电源VCC经内部电路流出输入端,电流较大,当与上一级电路衔接时,将决定上级电路应具备的负载能力。高电平输出电压在负载不大时为3.5V左右(当VCC=5V时)。低电平输出时,允许后级电路灌入电流,随着灌入电流的增加,输出低电平将升高,一般LS系列TTL电路允许灌入8mA电流,即可吸收后级20个LS系列标准门的灌入电流。最大允许低电平输出电压为0.4V。

2.CMOS电路输入输出电路性质

一般CC系列的输入阻抗可高达1 010Ω,输入电容在5pF以下,输入高电平通常要求在3.5V以上,输入低电平通常在1.5V以下。因CMOS电路的输出结构具有对称性,故高低电平具有相同的输出能力,负载能力较小,仅可驱动少量的CMOS电路。当输出端负载很轻时,输出高电平将十分接近电源电压;输出低电平时将十分接近地电位。

在高速CMOS电路54/74HC系列中的一个子系列54/74HCT,其输入电平与TTL电路完全相同,因此在相互取代时,不需考虑电平的匹配问题。

3.集成逻辑电路的衔接

在实际的数字电路系统中总是将一定数量的集成逻辑电路按需要前后连接起来。这时,前级电路的输出将与后级电路的输入相连并驱动后级电路工作。这就存在着电平的配合和负载能力这两个需要妥善解决的问题。可用下列几个表达式来说明连接时所要满足的条件:

VoH(前级)≥ViH(后级) VoL(前级)≤ViL(后级)

IoH(前级)≥n×IiH(后级) IoL(前级)≤n×IiL(后级) n为后级门的数目

(1)TTL与TTL的连接

TTL集成逻辑电路的所有系列,由于电路结构形式相同,电平配合比较方便,不需要外接元件可直接连接,主要的限制是受低电平时负载能力的限制。表6-3列出了74系列TTL电路的扇出系数。

表6-3 74系列芯片扇出系数比较

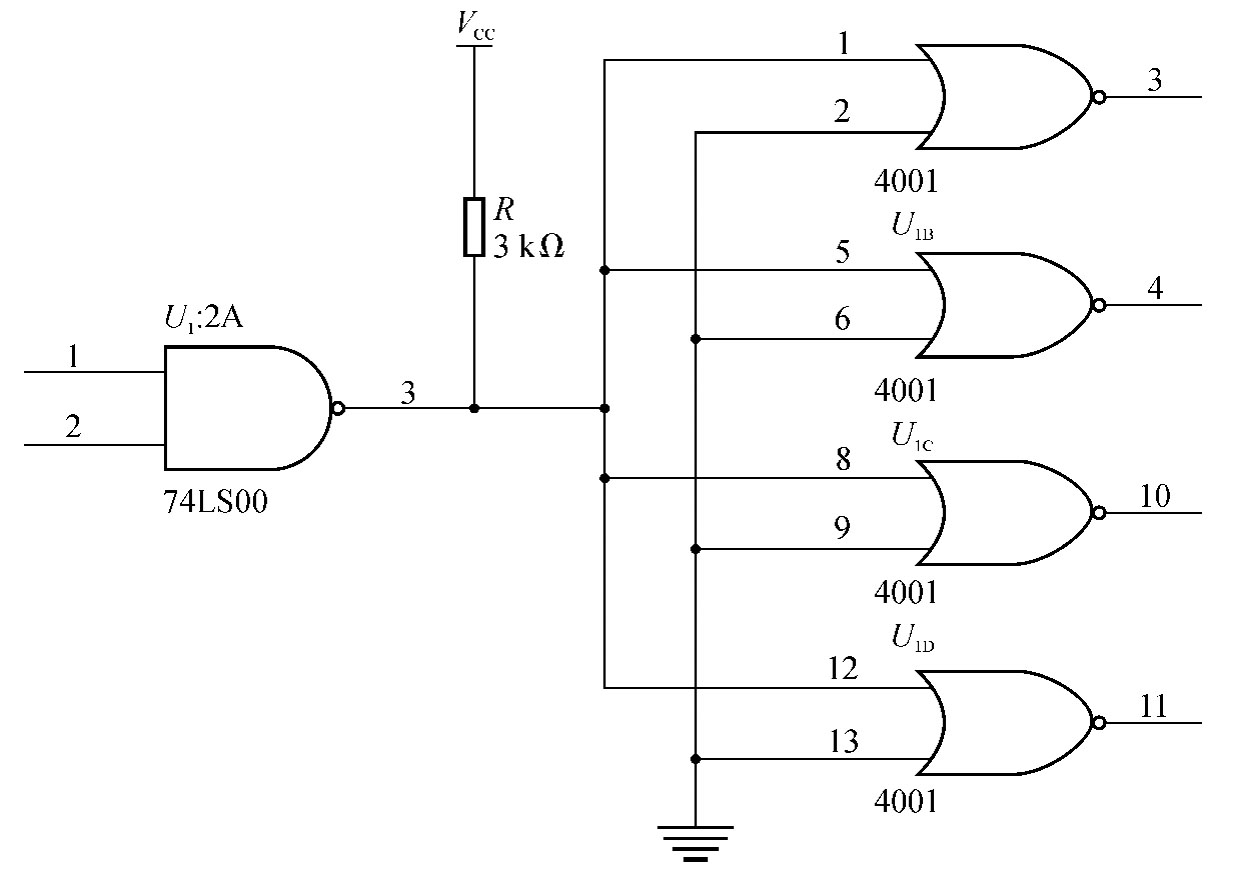

(2)TTL驱动CMOS电路

TTL电路驱动CMOS电路时,由于CMOS电路的输入阻抗高,故驱动电流一般不会受到限制,但在电平配合问题上,低电平是可以的,高电平有困难。因为TTL电路在空载时,输出高电平通常低于CMOS电路对输入高电平的要求,因此为保证TTL输出高电平,后级的CMOS电路能可靠工作,通常要外接一个上拉电阻R,如图6-23所示,使输出高电平达到3.5 V以上,R的取值为2~6.2kΩ较合适,这时TTL后级的CMOS电路的数目可以很多。

图6-23 TTL电路驱动CMOS电路

(3)CMOS驱动TTL电路

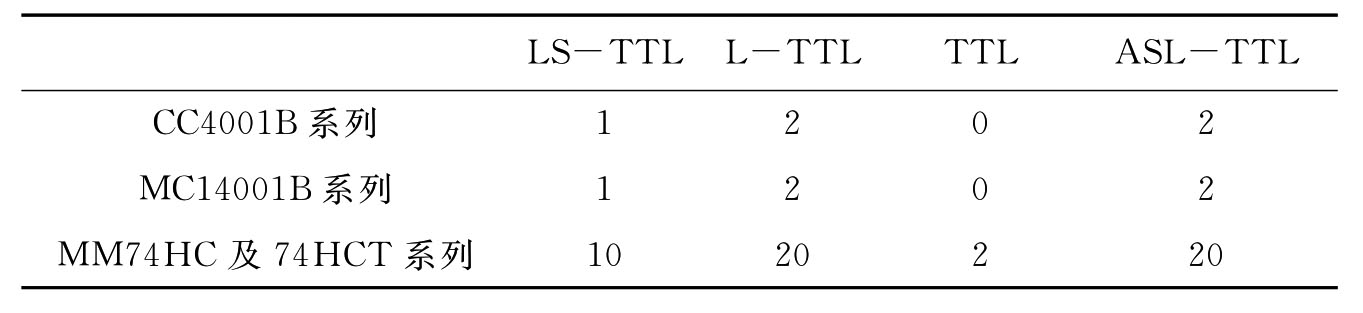

CMOS的输出电平能满足TTL对输入电平的要求,而驱动电流将受限制,主要是低电平时的负载能力。表6-4列出了一般CMOS电路驱动TTL电路扇出系数,从表中可见,除了74HC系列外的其他CMOS芯片驱动TTL的能力都较低。

表6-4 各种门的驱动能力

既要使用此系列又要提高其驱动能力时,可采用以下两种方法:

①采用CMOS专用驱动器,如CC4049,CC4050等芯片。

②将几个同功能的CMOS电路并联使用,即将其输入端并联,输出端并联(TTL电路是不允许并联的)。

(4)CMOS与CMOS的衔接

CMOS电路之间的连接十分方便,不需另加外接元件。对直流参数来讲,一个CMOS电路可带动的CMOS电路数量是不受限制的,但在实际使用时,应当考虑后级门输入电容对前级门的传输速度的影响,电容太大时,传输速度下降,因此在高速使用时要考虑负载电容,例如CC4000T系列。CMOS电路在10MHz以上速度运用时应限制在20个门以下。

三、实验设备与器件

1.数字逻辑电路实验箱

2.数字万用表

3.芯片74LS00、74LS04,CC4001、74HC00

4.100Ω、470Ω、3kΩ电阻,4.7kΩ可调电位器(规格为3296、在IC插座上连接)

四、实验内容及实验步骤

1.测试TTL电路74LS00及CMOS电路CC4001的输出特性

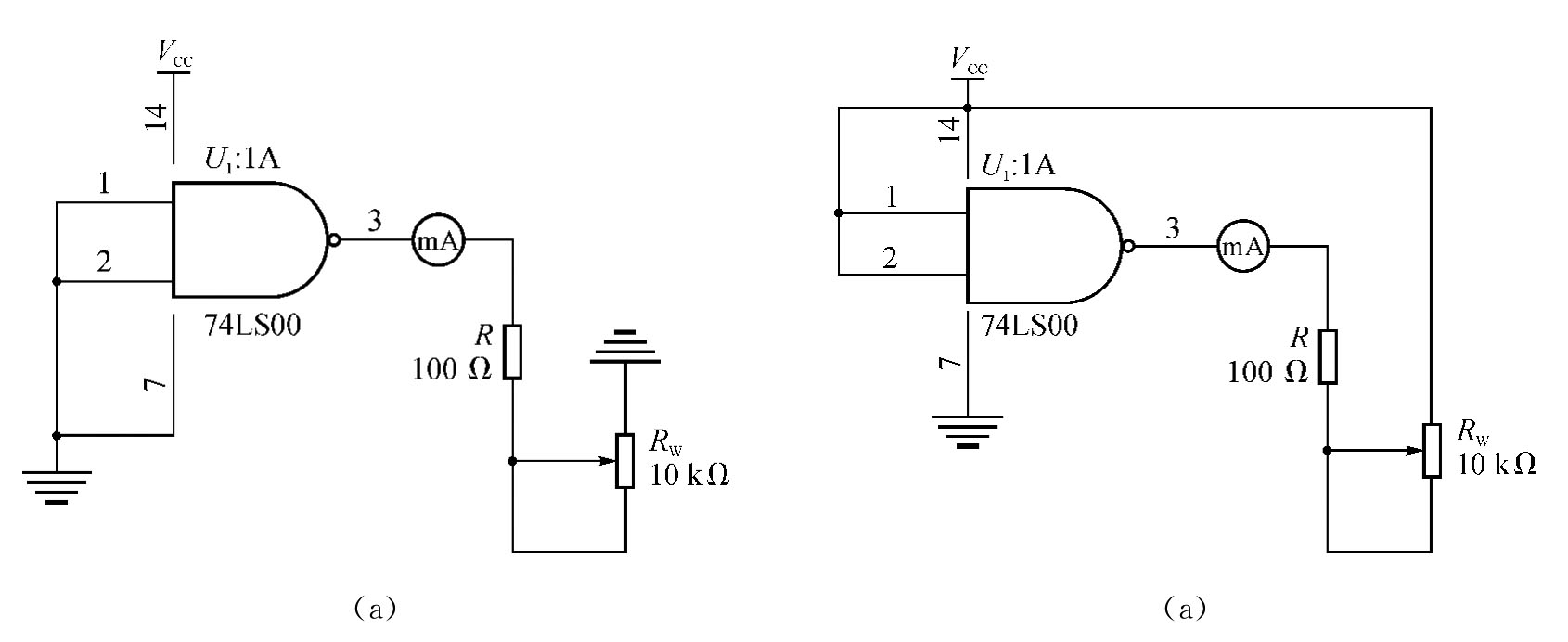

(1)测试TTL电路74LS00的输出特性

在数字逻辑电路实验箱IC插座模块处找一个DIP14的插座插上芯片74LS00(CC4001),并在DIP14插座的第7脚接上实验箱的地(GND),第14脚接上电源+5V(VCC)。测试电路如图6-24所示,改变电位器RW的阻值,从而获得输出特性曲线,R为限流电阻。对图6-24(a)所示输出高电平测试时应测量到最小允许高电平(2.7V)之间的系列点;对图6-24(b)所示输出低电平测试时应测量到最大允许低电平(0.4V)之间的系列点。

图6-24 与非门输出特性测试电路

(2)测试CMOS电路CC4001的输出特性

同(1)方法,测量出CC4001的输出特性,测试时R取为470Ω,RW取10kΩ不变,VCC为+5V。输出高电平测试时应测量到最小允许高电平(4.6V)之间的系列点;输出低电平测试时应测量到最大允许低电平(0.4V)之间的系列点。

2.TTL电路驱动CMOS电路

用74LS00的一个门来驱动CC4001的四个门,实验电路如图6-23。测量连接3kΩ与不连接3kΩ电阻情况下的各芯片逻辑功能及输出的高低电平电压值。

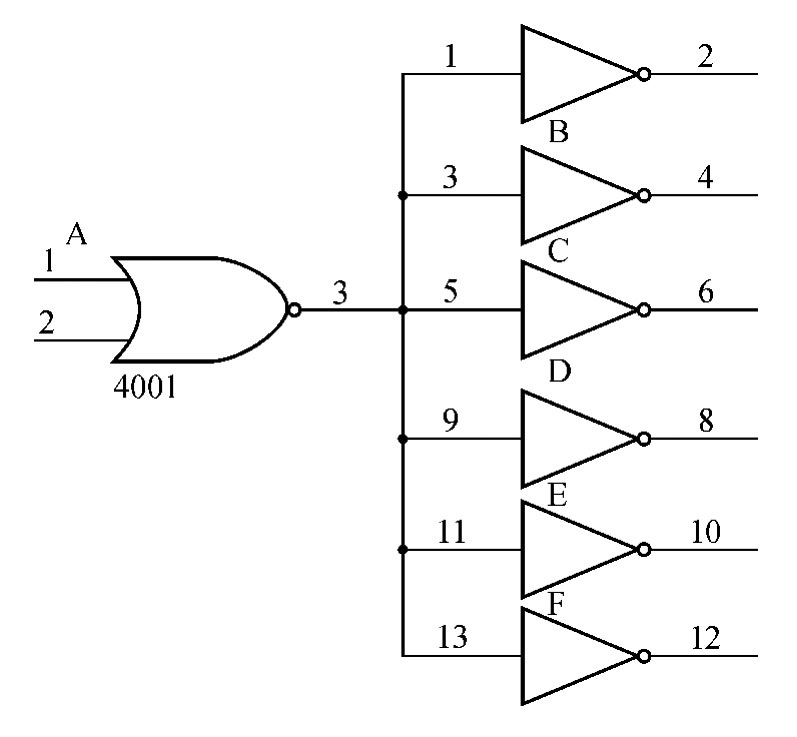

3.CMOS电路驱动TTL电路

电路如图6-25所示,被驱动的电路用74LS04的6个非门并联。电路的输入端接逻辑电平输出模块处的输出插口,6个输出分别接逻辑电平显示模块处的输入插口。先用CC4001的一个门来驱动,观测CC4001的输出电平和74LS04的输出逻辑功能。然后将CC4001的其余三个门,一个个并联接到第一个门上(输入与输入并联,输出与输出并联),分别观察CMOS的输出电平及74LS04的逻辑功能。最后用1/4 74HC00代替1/4CC4001,测试其输出电平及系统的逻辑功能。

五、实验预习要求

1.自拟各实验记录用的数据表格及逻辑电平记录表格。

2.熟悉所用集电路的引脚功能。

六、实验报告要求

1.整理实验数据,作出输出特性曲线,并加以分析。

2.通过本次实验,你对不同集成门电路的衔接得出什么结论?

图6-25 CMOS电路驱动TTL电路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。