【摘要】:若像素电极边缘刻蚀量(边刻蚀)过大,则可能会造成ITO与接触孔的错位而引起点缺陷,或引起遮光区域外的液晶分子控制不良,导致漏光,如图8.17像素电极两边的白色部分所示。另外,由于ITO膜透明,为防止边刻蚀量过大或不足,以及在与CF基板对准时,需要使用一些辅助配线。

8.4.3 像素电极湿刻

在许多TFT的设计中,都把像素电极膜放在阵列基板的最上层,这样对电极形状的要求比较低,但是对线宽控制的要求比较高,因此在两刻蚀槽中均采用速度较快、对线宽控制较好的喷淋方式进行湿刻,在工艺性能上对ITO残渣与线宽控制要求比较严格。

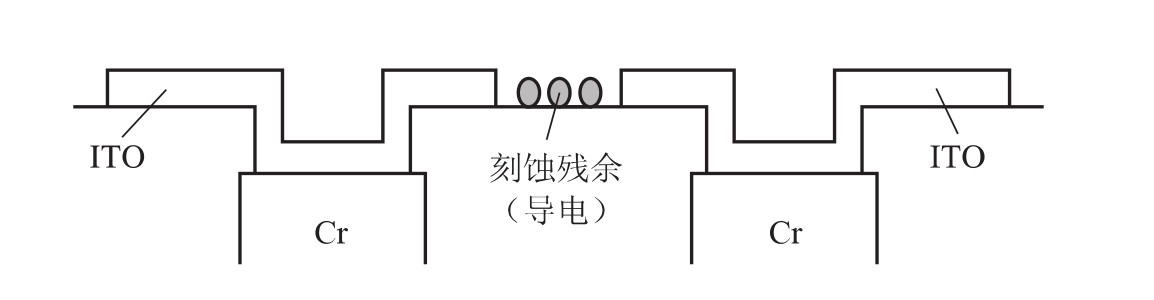

1.像素电极刻蚀残余

若刻蚀量不足,且存在ITO膜的结晶不均匀时,易产生刻蚀残余,导致点缺陷和短路,如图8.15所示。又如图8.16所示,还会造成端子部的短路。

图8.15 刻蚀量不足导致点缺陷和短路

图8.16 刻蚀量不足造成端子部的短路

2.像素电极刻蚀线宽控制

若像素电极边缘刻蚀量(边刻蚀)过大,则可能会造成ITO与接触孔的错位而引起点缺陷,或引起遮光区域外的液晶分子控制不良,导致漏光,如图8.17(a)像素电极两边的白色部分所示。若像素电极边缘边刻蚀量过小,则像素电极边缘与漏极产生部分交叠,形成附加电容,如图8.17(c)所示,引起显示不均(姆拉)。如果整个基板上像素电极的边刻蚀均一性不好,将引起显示不良。

另外,由于ITO膜透明,为防止边刻蚀量过大或不足,以及在与CF基板对准时,需要使用一些辅助配线。如图8.18中的线a、线b、线c、线d,阴影部分为与上层CF基板黑矩阵对应的遮光部分,线a、线d与漏极在同一层上;线b、线c与栅极在同一层上,其断面图为图8.17中所标示的“g”。

图8.17 边缘刻蚀量(边刻蚀)过大导致漏光,形成附加电容,引起显示不均

图8.18 为防止边刻蚀量过大或不足使用一些辅助配线

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。