基于ARM电子白板的系统硬件电路主要由信号发射模块、信号采集模块和信号处理模块三部分组成,总体框图如图11-4所示。

图11-4 系统硬件框图

11.2.1 基于ARM电子白板的系统硬件平台

1.信号发射模块

信号发射模块封装在信号笔中,原理框图如图11-5所示。书写时,笔尖与书写板之间的压力使笔内的电源接通,信号笔开始以17 ms为周期发射超声、红外信号。当停止书写时,笔尖与书写板断开接触,笔内电源断开,信号笔停止工作。信号笔发出的超声、红外信号的时序见图11-6所示。

图11-5 信号笔原理框图

图11-6 红外、超声信号时序图

2.信号采集模块

信号采集模块原理框图如图11-7所示,它负责接收信号笔周期性发出的红外、超声信号并放大和模数转换,然后,将转换后的数据送入DSP处理器中进行时延提取,最后通过USB接口送入信号处理模块进行处理。

图11-7 信号采集模块原理框图

3.信号处理模块

信号处理模块是基于ARM的电子白板的核心部分。

11.2.2 信号处理模块硬件设计

11.2.2.1 S3C2440X接口电路设计

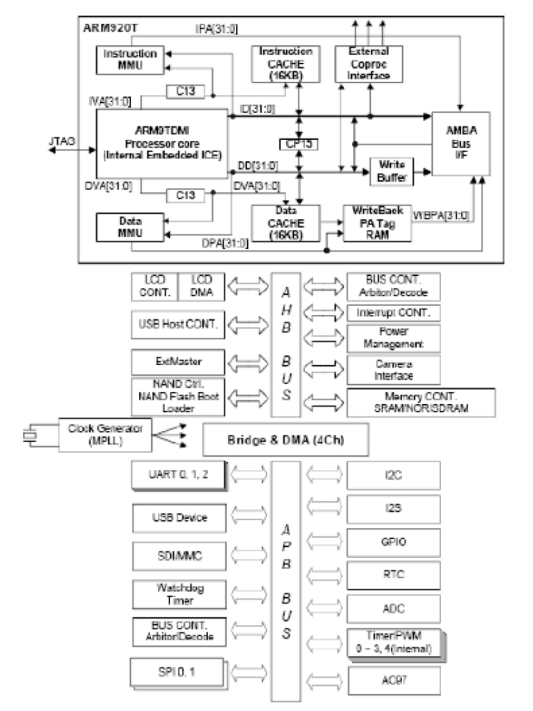

系统使用的CPU是韩国三星公司生产的S3C2440X,采用ARM公司设计的16/32位ARM920T处理器内核,最高工作频率533MHz。S3C2440X内部结构(如图11-8所示),由ARMTDMI、存储管理单元(MMU)和高速缓存三部分组成,其中MMU可管理虚拟内存,高速缓存由16 kB指令Cache和16 kB数据Cache组成。另外还有两个内部协处理器:CP14和CP15。CP14用于调试控制,CP15用于存储系统控制和测试控制。

图11-8 S3C2440X处理器内部结构图

ARM920T系列的处理器具有较高的性价比和较低的功耗,其特点如下:

(1)采用5级流水线结构,每个时钟周期可以执行5条指令,大大提高了处理性能;

(2)采用1.1MIPS/MHz哈佛结构,内部具有独立的数据Cache和程序Cache,取地址和取数据可同时进行,具有较高的执行效率;

(3)支持32位的ARM指令集和16位的Thumb指令集;

(4)支持32位高速AMBA总线接口;

(5)具有全性能的MMU,支持Windows CE、Linux、VxWorks等多种主流操作系统;

(6)MPU支持实时操作系统。

S3C2440X具有丰富的片上资源,具体资源如下:

(1)1.2 V内部电压,1.8 V/2.5 V/3.3 V外部I/O微控制器,带有16 kB ICache/16 kB D-Cache/MMU;

(2)外部存储器控制器(SDRAM控制器和片选逻辑);

(3)LCD控制器(支持STN和TFT)和1通道LCD专用DMA;

(4)4个通道的DMA,带有外部请求管脚;

(5)3通道UART(Universal Asynchronous Receiver and Transmitter),IrDA1.0,64字节Tx FIFO和64字节Tx FIFO,2通道SPI;

(6)1个I2 S总线控制器;

(7)1个SD卡1.0版本接口和1个MMC卡2.11版本接口;

(8)2个主USB和1个从USB(USB1.1);

(9)4个具有PWM功能的定时器和一个内部计时器;

(10)1个看门狗定时器;

(11)130个通用I/O口和24个外部中断源;

(12)电源控制模式:常态、省电、空闲和睡眠;

(13)8通道10位ADC和触摸屏接口;

(14)1个具有日历功能的实时时钟RTC;

(15)1个具有锁相环的片上时钟发生器。

1.时钟与电源管理

时钟和电源管理模块包括三个部分:时钟控制、USB控制和电源控制。

S3C2440X内部有两个锁相环:MPLL和UPLL。其中MPLL用于产生CPU使用的FCLK时钟信号、AHB总线使用的HCLK时钟信号和APB总线使用的PCLK时钟信号;UPLL用于产生USB设备所需要的时钟信号(48MHz)。S3C2440X的时钟控制逻辑可由外部晶振或者外部时钟来提供产生慢的时钟信号,由软件设定和外围设备的连接或者不连接以降低能耗,通过OM[3∶2]来实现对时钟的选择。

OM[3∶2]=00B时,外部晶振为MPLL和UPLL提供时钟源;

OM[3∶2]=01B时,外部晶振为MPLL提供时钟源,EXTCLK为UPLL提供时钟源;

OM[3∶2]=10B时,EXTCLK为MPLL CLK提供时钟源,外部晶振为UPLLCLK提供时钟源;

OM[3:2]=11B时,EXTCLK为MPLL和UPLL提供时钟源。

为了有效地降低系统的功耗,S3C2440X采用了四种电源管理模式。

Normal模式:系统为CPU和全部外设提供时钟,如果所有外设都工作,则此时系统功耗最大。如果一个设备不工作,用户可以用软件切断和它的联系以降低功耗。

Slow模式:在这种模式下,采用外部时钟产生FCLK,此时电源的功耗取决于外部时钟。

Idle模式:在这种模式下,外部时钟与CPU核断开,外设保持正常,当需要CPU工作时,可产生中断,利用中断唤醒CPU核。

Sleep模式:在Sleep模式下,提供给CPU核和内部逻辑的电源被关闭,只保留唤醒逻辑。在此模式下要唤醒时钟需要两个独立的电源:一个提供给唤醒逻辑,另一个提供给CPU核及其内部逻辑,这个需要用到电源开关。该模式可以通过EINT[15∶0]和RTC唤醒。

2.存储器控制器

S3C2440X片内集成的存储器控制器,具有独立的刷新控制逻辑,提供了访问外部存储器所需要的控制信号,S3C2440X的存储器控制器特征如下:

(1)支持大端/小端模式;

(2)具有1 GB的地址空间,共分为8个内存块Bank0-Bank7,每个内存块为128 MB;

(3)Bank0支持16/32位数据总线编程,其他七个Bank支持8/16/32位的数据总线编程;

(4)Bank0-Bank5支持ROM、SRAM类型的存储器,Bank6和Bank7支持ROM、SRAM、SDRAM类型存储器;

(5)Bank0-Bank6的存储器起始地址是固定的,Bank7的起始地址和编程空间是可以动态调整的;

(6)所有的Bank的访问周期都是可编程的,并且总线访问周期可以通过插入外部wait来延长;

(7)支持SDRAM的自刷新和掉电模式。

存储区映射如图11-9所示,左边为非NAND Flash引导,右边为NAND Flash引导。采用非NAND Flash引导时,存储器的片选连接到nGCS0,起始地址映射到地址空间的0X00000000处,系统从存储器中直接运行启动代码;采用NAND Flash引导时,S3C2440X内部“Steppingstone”的起始地址映射到地址空间的0X00000000处,系统从“Steppingstone”中运行启动代码。S3C2440X的引导模式由OM0和OM1两个引脚的配置状态决定,具体配置如下:

OM1=0,OM0=0 由NAND FLASH引导;

OM1=0,OM0=1 由16位程序存储器引导;

OM1=1,OM0=0 由32位程序存储器引导;

OM1=1,OM0=1 CPU测试模式。

3.NAND Flash控制器

NAND Flash存储器的特点是存取速度快、容量大、成本低。S3C2440X内部集成了NAND Flash控制器,并且支持从NAND Flash启动,S3C2440X内部集成了一个称为“Steppingstone”的SRAM缓冲器,当系统启动时,NANDFlash存储器的前面4 k字节的启动代码被自动地载入到“Steppingstone”中运行,此时4 k的SRAM被映射到系统存储空间的0X00000000处。一般情况下,这4 k的引导代码需要完成的工作是将NAND Flash中程序代码拷贝到SDRAM中,当引导代码执行完毕后,跳转到SDRAM中继续执行程序代码。NAND Flash的特性如下:

(1)NAND Flash模式:支持读/擦/编程NAND Flash存储器(其启动流程如图11-10所示);

(2)自动引导模式;

(3)具有四个ECC(Error Correction Code)模块;

(4)具有4 k内部SRAM缓冲器Steppingstone。

图11-9 S3C2440X存储区映射

图11-10 NAND Flash启动流程图

4.LCD控制器

LCD控制器的主要工作是将定位在系统存储器显示缓冲区中的图像数据传送到外部LCD驱动器上,S3C2440X内置的LCD控制器支持STN型和TFT型LCD,支持灰度和彩色显示。在灰度显示上,它采用基于时间的抖动算法和FRC(Frame Rate Control)方法,支持单色、4级灰度、16级灰度模式的灰度LCD显示;在彩色显示上,支持256级和4096级色彩。此外,它还可以通过编程对LCD的各项指标进行设置,如行和列像素数、数据总线宽度、时序接口和刷新率等,其结构原理框图如图11-11所示。

图11-11 LCD控制器结构框图

5.USB Host和USB Device控制器

S3C2440X内部具有两个USB主机接口、一个USB设备接口。

USB Host的接口特性如下:

(1)支持OHCI1.0版本规范;

(2)支持USB1.1版本规范;

(3)两个下行端口;

(4)支持低速USB设备和高速USB设备。

USB Device的接口特性如下:

(1)完全兼容USB1.1协议;

(2)支持全速(Full Speed)设备;

(3)集成的USB收发器;

(4)支持Control、Interrupt和Bulk传输模式;

(5)5个具备FIFO的通信端点,1个双向的控制端点,16 byte的FIFO(EP0),4个双向的批传输端点,128 byte的FIFO(EP1,EP2,EP3,EP4);

(6)批(Bulk)接收的发送端点支持DMA操作方式(EP1,EP2,EP3,EP4);

(7)接收和发送FIFO均有128 byte的FIFO;

(8)支持挂起和远程唤醒功能。

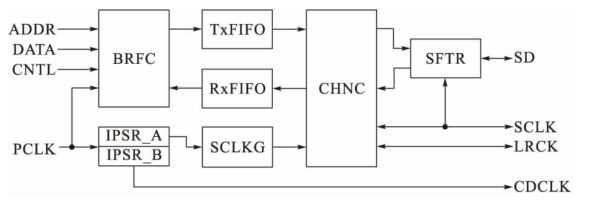

6.I2S总线

S3C2440X的I2 S总线接口可以用来实现对外部8/16位立体声数字音频信号编解码器电路的接口功能,实现音频播放和录制,支持I2 S数据格式和MSB-justified数据格式。I2 S总线的FIFO操作为DMA模式,在某一时刻,它可以在一个时刻只接收或发送数据,也可以同时接收和发送数据,其结构框图如图11-12所示。

图11-12 I2 S总线结构框图

S3C2440X芯片有289个引脚,体积比较大。

11.2.2.2 存储电路设计

1.SDRAM与S3C2440X接口电路设计

K4S561632C-TC75是韩国三星公司开发的容量为32MB的4Banks×4M×16bit的SDRAM,工作电压3.3 V,更新周期64 ms,数据宽度16位,54脚TSOP封装,兼容LVTTL接口,支持自刷新功能。其中CLK为芯片时钟输入信号,CKE为芯片时钟使能信号,CS为片选信号,BA0和BA1为组地址选择信号,A12-A0为地址总线(A12-A9为行地址,A8-A0为列地址),DQ15-DQ0为数据总线,RAS为行地址锁存信号,CAS为列地址锁存信号,CE为写使能信号,LDQM、UDQM为数据I/O屏蔽信号。

为充分发挥32位CPU的数据处理能力,系统(兰英,2008年)采用两片16位据宽度的K4S561632C-TC75构造出32位数据宽度的存储器系统,共64 MB存储空间。U14的DQ15-DQ0连接S3C2440X的低16位数据总线,U15的DQ15-DQ0连接S3C2440X的高16位数据总线,U14和U15的A12-A0都接到连接S3C2440X的地址总线上,两片SDRAM的片选CS接到连接S3C2440X的LnGCS6引脚,这样就可将两片SDRAM作为一个整体配置到Bank6,在系统存储区中的起始地址为0X30000000,此时U14中存放32位数据的低16位,U15存放32位数据的高16位。C153~C162、C166~C169电容为0.1μF高频滤波电容,每片SDRAM使用7个,来提高K4S561632C-TC75电源的稳定性。

2.NAND Flash与S3C2440X接口电路设计

K9F1208U0M是韩国三星公司生产的NAND Flash芯片,其特点是容量大、功耗小、成本低。K9F1208U0M的容量为64 MB,8位数据宽度,工作电压为2.7~3.6 V,采用48脚TSOP封装,块擦写时间为2 ms,具有硬件数据保护功能和上电自动引导功能,数据存储时间为10年以上。I/O[7∶0]为数据输入输出、控制命令和地址的输入引脚,CLE为命令锁存信号,ALE为地址锁存信号,CE为芯片使能信号,RE为读有效信号,WE为写有效信号,WP为写保护信号,R/nB为准备就绪/忙信号。K9F1208U0M的I/O口为数据、地址、控制信号复用口,它既可以接收、发送数据,也可以接收地址信息和命令信息。当CLE有效时,锁存在I/O上的是控制命令字;当ALE有效时,锁存在I/O上的是地址;RE或WE有效时,锁存在I/O上的是数据。S3C2440X内部集成了NAND Flash控制器,只需设置相关的寄存器,即可完成对NAND Flash的控制操作。

系统用一片K9F1208U0M作为固态存储介质来存储系统的Bootloader、Windows CE内核。K9F1208U0M与S3C2440X接口电路简单,其中IO0-IO7连接系统数据总线的低8位,在S3C2440X的NCON和RnB引脚处需要加4.7 kΩ的上拉电阻,其目的是增加K9F1208U0M的稳定性。

3.网卡电路设计

DM9000是CIRRUS LOGIC生产的可支持8位、16位和32位以太网卡的接口芯片,接入带宽为10 M/100 M,工作电压为3.3~5 V,采用100脚LQFP封装,支持全双工通信,内部集成IEEE802.3协议标准的MAC引擎,通过硬件实现MAC层协议以节约更多的CPU资源。支持MII和反转MII接口,支持半双工模式反馈请求,集成4 k DWORD的SRAM。考虑到体积、功耗等因素影响,将DM9000与CPU直接相连。以太网数据链路层、物理层相关操作都可由DM9000自动完成,CPU只需要向DM9000发送或读取数据报,就可完成数据的网络传输。

DM9000的SA[9∶4]为6根地址总线,当SA9和SA8为高电平,SA7和AEN(Address Enable,地址选通)为低电平,SA6~4和TXD2~0连接时,DM9000被选中。SD[15∶0]为16根数据总线,片选信号AEN连接到S3C2440X的nGCS2,只有当nGCS2有效时,DM9000才可以执行存储器读写操作。INT是DM9000的中断请求信号,与S3C2440X的IRQ LAN连接,当INT有跳变时,可以产生中断信号给CPU。RXI+、RXI-、TXO+和TXO-为以太网数据的TP接收端和TP发送端,它们通过以太网隔离器连接到RJ45上,系统采用HALO公司的内部集成以太网隔离器TG110-S050N2。

4.主从USB电路设计

系统具有两个USB Host,其中一个可作USB Device用,其中R52、R56、R50和R51为抗反射、回铃电阻,阻值为22Ω,R152和R154为信号下拉电阻,阻值为1.5 kΩ。

5.SM501显卡电路设计

之前国内嵌入式开发平台对于图形显示方面大多数采用的是LCD液晶屏,能显示的最大分辨率只能支持800×600,即使采用VGA接口也不能在更高分辨率下平滑播放MPGE1、MPGE4多媒体文件。

在本系统中为播放高分辨率的多媒体文件,清晰显示书写内容,采用板载2D加速显卡芯片SM501,SM501是一款便携多媒体协处理器芯片,具有视频和2D能力,支持多种输入/输出接口,包括模拟RGB、数字LCD屏接口、8位并行接口、USB、UART、IrDA、Zoom Video、AC97或I2 S、SSP、PWM和I2 C,同时它还带有GPIO,便于与外部器件连接。SM501的2D引擎包括一个前端色彩空间转换器,支持4∶1和1∶8的比例,视频引擎支持在每个像素点8位、16位和32位数据宽度时2个不同的视频输出,为每个视频输出提供三色硬件指针;LCD视频流水线支持一个黑点YUV色彩空间转换,比例为4∶1和1∶212;放大视频接口包括MPEG解码或TV输入的外部电路接口,可实现真正的VGA、TFT到LCD输出,并且在1024×768×32高分辨率下可平滑播放MPGE1、MPGE4多媒体文件。SM501系统模块如图11-13所示。

图11-13 SM501系统模块结构图

系统用到了SDRAM作为数据缓冲区和LCD及CRT,系统框图如图11-14所示。

图11-14 系统中SM501部分系统框图

系统中S3C2440X处理器将LCD的数据放入SDRAM的帧缓冲区中,然后将显示工作交给SM501处理。通过2D图形引擎,SM501从SDRAM的帧缓冲区中读取数据,并将这些数据输送到LCD显示器,这样LCD的数据没有经过ARM处理器的LCD控制器。因此LCD数据的传输不受ARM处理器的HCLK时钟影响,达到了支持高分辨率的设计要求。

在SM501部分用的SDRAM是韩国Hynix半导体公司生产的4Banks×1 M×32 bit的HY57V283220,容量为16 MB,工作电压为3.3 V,数据宽度32位,86脚TSOP封装,兼容LVTTL接口,支持自刷新功能。

其中CLK为时钟输入信号,CKE为时钟使能信号,CS为片选信号,BA0-BA1为组地址选择信号,A0-A11为地址总线,RAS为行地址锁存信号,CAS为列地址锁存信号,CE为写使能信号,DQM0-3为数据I/O屏蔽信号,DQ0-DQ31为数据总线,VDD/VSS为电源和地,VDDQ/VSSQ为数据输出源和地,NC保留,没有连接。SM501的LCD逻辑模块可以直接驱动一个18位或24位的TFT LCD显示屏;同时也支持12位的CSTN屏,通过一个颤抖引擎(dithering engine)可以得到有效的18位显示效果。支持的最大屏的大小为1280×1024。通过硬件和软件可控制LCD显示屏上电顺序。

6.声卡电路设计

声卡芯片是Philips公司生产的音频编解码器UDA1341TS,主要用于实现模拟音频信号采集和数字音频信号模拟输出,为模拟信号采集提供可编程增益控制(PGA)和自动增益控制(AGC),对数字信号增加了数字信号处理能力。采用28脚SSOP封装,工作电压为3.3 V。

S3C2440X的I2S时钟信号I2 SSCLK与UDA1341TS的BCK引脚连接,声道选择信号I2 S LRCK与WS引脚连接,编码时钟信号CDCLK与SYSCLK引脚连接,UDA1341TS提供了两个音频通道:音频输出引脚DATAO和音频输入引脚DATAI,分别与I2S总线的I2 S SDI和I2 S SDO引脚相连。L3MODE、L3CLOCK和L3DATA为L3总线,由于I2 S总线只能用来传输音频数据,没有控制功能,因此需要借助L3总线来完成音频信号音量的调整和低音效果设置等功能。S3C2440X内部没有提供L3总线,故需要将GPB2、GPB3和GPB4三个I/O口扩展为L3总线,从而实现对音频信号的控制功能。

7.电源及复位电路设计

(1)电源电路设计。

系统采用直流5 V供电。S3C2440X内核使用电压为1.2 V,USB Host使用电压为5 V,SM501需要1.8 V和3.3 V电压,片上外设和其他片外外设使用电压为3.3 V,为此系统采用LM1117系列电源稳压器产生系统所需要的电压。LM1117是National半导体公司生产的低漏失线性稳压器,这个系列提供1.8 V、3.3 V、5 V和电压可调的稳压芯片,其特点是具有电流限制和热保护功能,输出电流最大800 m A,线性调整率为0.2%,负载调整率为0.4%。

(2)复位电路设计。

复位电路主要完成系统的上电复位和运行时用户的按键复位功能。系统采用Maxim公司的MAX811 T/SOT143复位芯片,它有四个管脚,可以精确监控3 V、3.3 V和5 V的电压。工作电流6μA。

8.UART电路设计

S3C2440X提供三个相互独立的异步串行I/O口,每个串口包含2个16字节的FIFO寄存器,用于发送和接收数据。每个串口都可工作在中断模式或DMA模式下,通过产生中断或DMA请求在S3C2440X和UART间进行数据传输。当使用系统时钟时,S3C2440X的UART最大传输速度为115.2 kbps,当用外部设备提供时钟时,可达到更高的传输速度。

MAX3223是Maxim公司生产的串口电平转换芯片,其主要功能是完成LVTTL电压到RS-232标准电压的转换,其工作电压为3.0~5.5 V,采用20脚SOP封装。

系统在调试阶段使用UART0,显示系统的调试信息和下载Windows CE内核;由于UART0需要与PC机通信,因此,需要MAX3223进行电平转换。

9.JTAG电路设计

JTAG技术是一种嵌入式调试技术,主要用于芯片内部测试和对系统进行仿真、调试。在芯片内部封装专门的测试电路,通过JTAG测试工具可以对内部节点进行测试。大多数复杂CPU都支持JTAG协议,如ARM、DSP、FPGA等。JTAG的主要功能是烧写Bootloader。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。