3.5 4次光刻技术

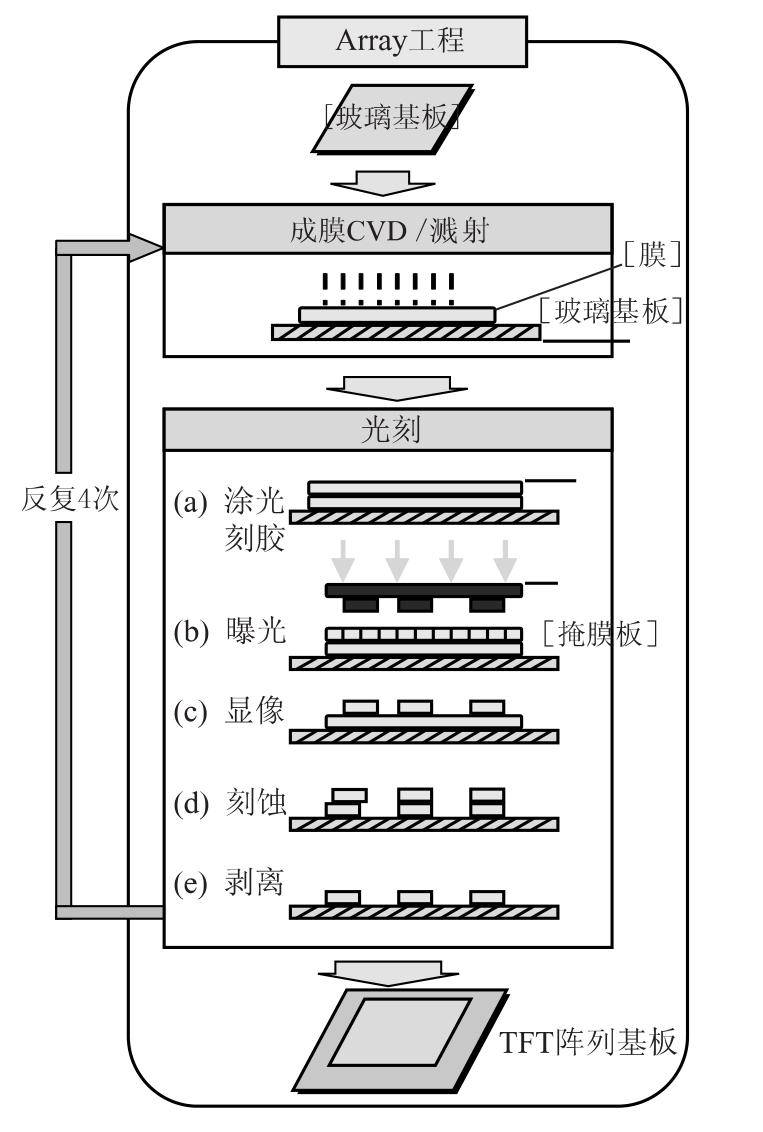

4次光刻的工艺流程图如图3.29所示。

图3.29 4次光刻循环流程

4次光刻是在5次光刻基础上发展起来的,其中比较重要的变化是将非金属层非晶硅与n+非晶硅的光刻和漏极与源极的光刻合并在一起,把ITO膜制作放在最后,通过在保护膜上打接触孔的方法,实现ITO膜与源极的接触。

TFT-LCD的生产工艺的核心技术是基本稳定的,各家的生产工艺大同小异。图3.30所示是TN型4次光刻和IPS/SFT宽视角显示器5次光刻的工艺比较。许多第5代生产线厂家采用5次光刻技术。特别是宽视角屏基本上都是采用5次光刻技术。5次光刻技术主要是把非晶硅层的光刻和漏源极的光刻分开了。宽视角显示器栅极以后的检查非常重要,而TN型没有这个检查。但TN型增加了一个终检,宽视角显示器TFT阵列不需要终检。

图3.30是TN型TFT 4次光刻工艺和IPS/SFT型TFT 5次光刻工艺的比较。IPS/SFT多了一道栅极检查工艺,有源层和漏/源电极的光刻是分开进行的。TN型材料的TFT制作完成后有一道终检工艺,IPS/SFT型材料的TFT不需要这道工艺。

图3.30 4次光刻和5次光刻工艺比较

4次光刻工艺流程如下:

●Lot构成—受入洗净—栅极溅射—第1次光刻(涂光刻胶—曝光—显影检查—线幅测定—栅极湿刻—PR剥离)—剥离后外观检查—线幅测定—栅极段差测定;

●成膜前洗净——第1层SiNx-CVD;

●成膜前洗净——非晶硅—CVD—n+非晶硅CVD;

●成膜前洗净—漏源极溅射—第2次光刻(涂光刻胶,曝光—显影检查—线幅测定—PR形状检查—第1次漏源湿刻—I/PR干刻—线幅测定—第2次漏源湿刻—PR剥离)—剥离后外观检查—线幅测定—D/I段差测定—D检查(自动外观检查)—修复(切断)—沟道干刻—沟道段差测定;

●成膜前洗净—修复(连接)—修复后洗净—保护层SiNx-CVD第3次光刻(涂光刻胶,曝光—显影检查—线幅测定—接触孔干刻—PR剥离)—剥离后外观检查—接触孔段差测定—导通检查;

●成膜前洗净—像素电极溅射(PI—SP)—第4次光刻(涂光刻胶—曝光—显影检查—尺寸测定—PI—湿刻—PR剥离)—剥离后外观检查—尺寸测定—ITO段差测定—退火前洗净—退火—接触检查—特性检查—Array检查—修复(切断)—外观检查—入库。

下面详细介绍4次光刻工艺。

(1)在准备好的玻璃基板上溅射栅极金属膜(Cr/AlNd),见图3.31。

图3.31 溅射栅极金属膜

(2)经过栅极涂光刻胶—曝光—显影检查—线幅测定—栅极湿刻—PR剥离—剥离后外观检查—线幅测定—栅极段差测定,形成栅极图形,见图3.32。

图3.32 第1次曝光,湿刻形成栅极图形

(3)准备制作3层非金属膜,成膜前洗净,连续生长3层非金属膜:(3-a)栅极SiNx绝缘层;(3-b)a-Si膜;(3-c)n+a-Si膜,见图3.33。

图3.33 连续生长3层非金属膜

再溅射一层漏源极金属膜。在栅极图形上一共形成4层膜,3层非金属,1层金属,然后准备实施第2次光刻。

(4)再溅射一层漏、源极金属膜。在栅极图形上一共形成4层膜,其中3层是非金属膜,1层是金属膜,见图3.34。

图3.34 溅射漏、源极金属膜

(5)在第4层膜上涂光刻胶,见图3.35。

图3.35 在第4层膜上涂光刻胶

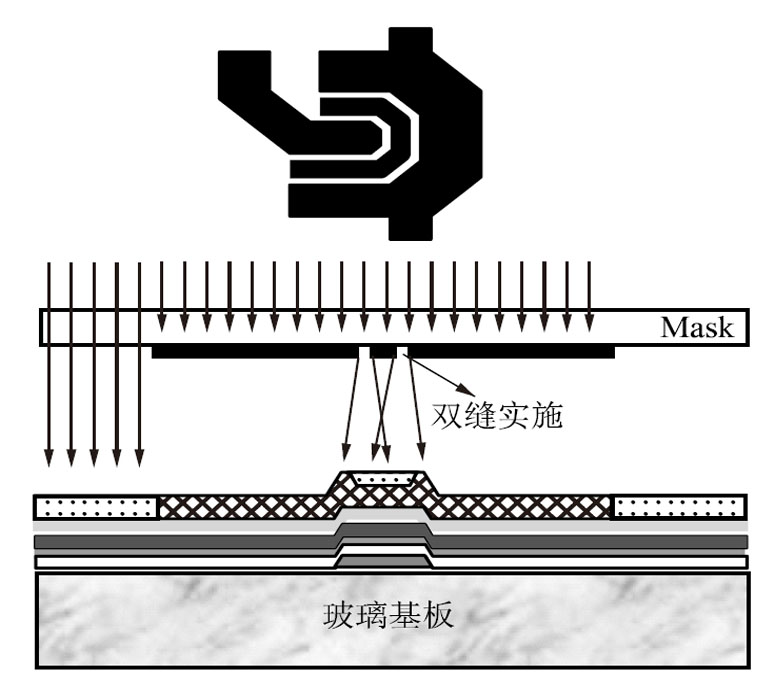

(6)曝光,TFT栅极顶部部分采用双缝曝光,控制曝光量在35%,见图3.36。

图3.36 第2次曝光(双缝曝光MASK的结构)

(7)将曝光部分光刻胶剥离。栅极顶部保留了二分之一的光刻胶,见图3.37。

图3.37 剥离曝光部分光刻胶

(8)采用湿刻,刻去多余的源极和漏极金属部分,采用干刻除去多余的n+a-Si/a-Si层,见图3.38。

图3.38 第1次湿刻和干刻

(9)采用干刻,除去多余的n+a-Si/a-Si层。再对沟道顶部的光刻胶进行干刻,把沟道顶部的金属膜露出来,见图3.39。

图3.39 第2次干刻

(10)线幅测定,检查光刻胶图形形状,进行第2次漏源湿刻,将源极和漏极分开。步骤为:线幅测定-D/段差测定—D检查(自动外观检查)—修复(切断),见图3.40。

图3.40 第2次湿刻,将源极和漏极分开

(11)干刻n+a-Si形成TFT沟道,光刻胶完全被剥离。剥离后进行外观检查,测定沟道段差。

(12)第3次干刻n+a-Si,形成非晶硅图形,光刻胶完全剥离,见图3.41。

图3.41 第3次干刻

(13)准备制作TFT保护膜,成膜前洗净,如果有缺陷,进行必要的修复(连接),修复后再洗净,然后CVD制作SiNx保护层。

(14)形成SiNx保护膜,见图3.42。

图3.42 形成SiNx保护膜

(15)涂光刻胶,曝光,显影检查,线幅测定,接触孔干刻,光刻胶剥离。剥离后外观检查,接触孔段差测定,导通检查,见图3.43。

图3.43 第3次曝光、干刻,形成源极和像素电极的接触孔

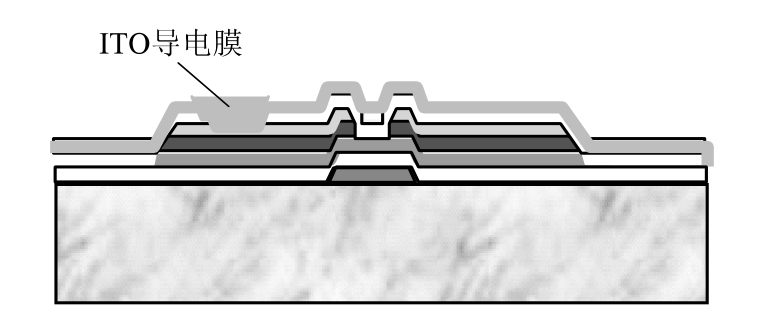

(16)准备制作ITO膜,成膜前洗净,溅射像素电极透明导电膜ITO最后形成像素电极,见图3.44。

图3.44 制作ITO膜

图3.45 形成ITO电极图形

(17)第4次光刻,涂光刻胶,曝光,检查显影,测定尺寸,湿刻ITO,剥离光刻胶,形成ITO电极图形,见图3.45。剥离后进行外观检查,测定尺寸,测定ITO段差,退火前洗净,退火,检查接触,检查特性,进行阵列检查。在这个进程中,如果发现缺陷,要修复缺陷,再进行外观检查。至此,整个TFT阵列制作完成,流入下一道工序——制屏。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。